分段电阻器数模转换器

背景技术:

1.一种类型的模数转换器(adc)是逐次逼近寄存器(sar)adc。sar adc以迭代方式确定输出数字代码,从最高有效位(msb)开始,然后是下一个最高有效位,依此类推,直到确定最低有效位(lsb)。sar adc的每个周期都会将输入模拟信号与阈值电压进行比较,阈值电压会在每次连续迭代时重置。在第一个周期中,阈值电压设置为输入电压范围的中点,如果输入电压高于阈值电压,则确定msb为“1”,如果输入电压低于阈值电压,则确定msb为“0”。一旦msb已知,如果msb被确定为1,则阈值电压在周期中重置为在前一个中点电压和最大输入电压之间范围内的中点,或者如果msb被确定为0,则阈值电压在周期中重置为在0v(即输入电压范围的下限)和前一个中点电压之间范围内的中点。该过程重复,每个周期重置阈值电压,直到确定lsb。此时,已确定完整的数字输出代码。

2.sar adc包括用于将数字值转换为阈值电压的数模转换器(dac),阈值电压通过比较器与模拟输入信号进行比较。提供给dac的数字值在每个周期发生变化,因此来自dac的模拟输出阈值电压也在每个周期发生变化,如上所述。

技术实现要素:

3.在一个示例中,一种模数转换器(adc)包括具有电阻器网络的数模转换器(dac)。电阻器网络包括第一段和第二段。第一段包括耦合在第一电源电压节点和第一组电阻器之间的第一开关。第二段包括耦合在第一电源电压节点和第二组电阻器之间的第二开关。第一段包括与第二电阻器串联耦合的第三开关。第三开关和第二电阻器的串联组合与第一组电阻器中的至少一个电阻器并联耦合。第二段包括与第三电阻器串联耦合的第四开关。第四开关和第三电阻器的串联组合与第二组电阻器中的至少一个电阻器并联耦合。

附图说明

4.对于各种示例的详细描述,现在将参考附图,其中:

5.图1图示了基于逐次逼近寄存器(sar)的模数转换器(adc)的示例。

6.图2示出了在图1的sar adc中使用的基于电阻器的数模转换器(dac)的示例实施方式。

7.图3示出了包括其中使用图1的sar adc的集成电路(ic)的服务器计算机的示例。

8.图4示出了在图1的sar adc中使用的基于电阻器的dac的另一个示例实施方式。

9.图5示出了在sar adc的dac中使用的单位电阻器的示例实施方式。

10.图6图示了串联连接的(如图5中)两个单位电阻器。

11.图7包括如图6中基于电阻器的dac的两个相邻段的电路模型。

12.图8示出了在图1的sar adc中使用的基于电阻器的dac的又一个示例实施方式。

13.图9包括如图8中基于电阻器的dac的两个相邻段的电路模型。

14.图10示出了图示图2的基于电阻器的dac的段的稳定时间段的时序图。

15.图11示出了基于电阻器的dac的个别段的替代示例和图示稳定时间段的时序图。

16.图12示出了用于减少由于dac内的开关电阻失配而导致的一对串联连接的电阻器的积分非线性的示例实施方式。

具体实施方式

17.图1示出了sar adc 100的示例实施方式。示例sar adc 100包括采样保持电路102、比较器104、sar 106和dac 108。采样保持电路102采样并保持输入电压vin,然后由比较器104将输入电压vin与来自dac 108的阈值电压109进行比较。来自比较器104的输出是高电平还是低电平,这取决于vin是大于还是小于dac的输出电压。每个周期中来自比较器104的输出表示输出数字代码的下一个最高有效位。输出数字代码存储在sar 106中,并可作为数字输出代码110从中检索。sar 106还向dac 108提供数字值107。dac 108将数字值107转换为要提供给比较器104的模拟阈值电压109。随着转换过程的每个周期更新数字值107,直到确定了数字输出代码110的所有位。

18.图2示出了dac 108的示例实施方式。在该示例中,dac 108包括电阻器网络和二进制-温度转换器235。电阻器网络包括多个二进制段210和多个温度段240。在该示例中,每个二进制段210包括一个开关sw和两个串联的电阻器r。如图所示,另一个电阻器r将一个二进制段210连接到二进制段210。每个电阻器r被称为“单位”电阻器。二进制段210的架构可以被称为r-2r电阻器网络。每个温度段240还包括一个开关sw和两个串联的电阻器r,但没有连接在温度段240之间的附加电阻器。

19.每个开关sw将该段的相应串联接法的电阻器耦合到参考电压(vref)或接地(vgnd)。在该示例中,dac 108包括10个二进制段210和15个温度段240。图2的示例中的dac 108是14位dac,其中来自sar 106的数字值107的10个最低有效位[b9:b0]控制二进制段210的开关sw,如236处所示。二进制位例如是“1”导致对应的开关将vref耦合到该段的电阻器,而二进制位为“0”导致对应的开关将vgnd耦合到该段的电阻器。数字值107的高四位由二进制至温度转换器235转换为15位温度代码以控制15个温度段t1至t15的开关sw。在每个周期中,基于数字值107的高四位的值,一个(或没有)温度位为高(将该段的电阻器耦合到vref),其余为低(将这些段的电阻器耦合到vgnd)。将温度段240连接在一起的节点n1将阈值电压109从dac 108提供给比较器104。

[0020]

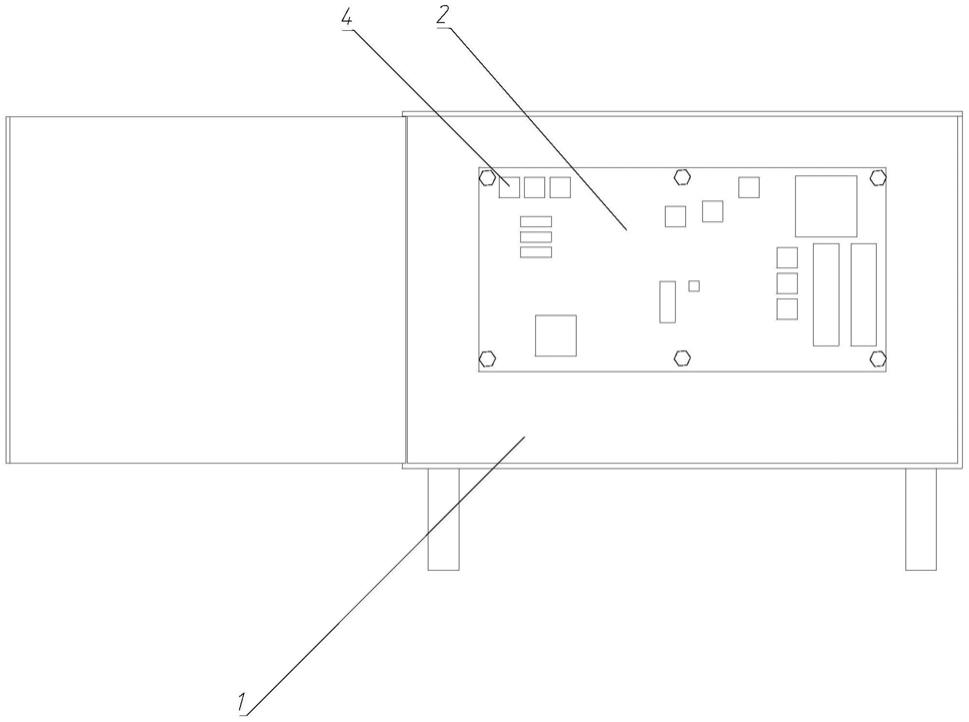

图3示出了服务器300(或其他类型的计算机)的示例,服务器300包括脉宽调制器(pwm)集成电路(ic)301、多个功率级320、多个电感器l1、中央处理单元(cpu)390和存储器392。也可以包括其他部件。pwm ic 301包括多相pwm。在pwm ic 301内提供多个pwm控制电路310,并且每个pwm控制电路310耦合到对应的功率级320。每个功率级320可以包括例如连接在电源节点和地之间的一对晶体管。每个功率级320耦合到对应的电感器l1。如图所示,电感器l1连接在一起以产生到cpu 390的电源电压(vout)。该电源电压还可用于为服务器300内的其他设备(例如存储器392)供电。每个pwm控制电路310控制对应功率级320内的每个晶体管何时接通和断开,从而调节到cpu 390的电压。

[0021]

每个功率级320产生电流感测(cs)信号和温度感测(ts)信号。cs信号表示相应功率级320的电流。cs信号由加法器345加在一起以生成组合电流(imon)。ts信号指示相应功率级320的温度。ts信号连接在一起作为到pwm ic 301的单个输入以提供指示最热功率级320的信号。

[0022]

在图3的示例中的pwm ic 301还包括sar adc 350,sar adc 350可用于将多个模拟信号355中的任何一个转换为数字值357。这种模拟信号355的示例包括到pwm ic 300的输入电压(vin)、imon信号、temp信号等。通信接口360(例如,符合电源管理总线(“pmbus”)协议)耦合到sar adc350并且可以将数字值355传输到外部设备。

[0023]

dac的差分非线性(dnl)是描述对应于相邻输入数字值的两个模拟电压之间的偏差的度量并且测量数模转换过程中的误差。在一些应用中(例如,pwm ic 301),一个sar adc 350用于数字化多个不同的模拟信号。因此,对于不同的电压范围,可以对sar adc 355施加不同的dnl要求。例如,对于模拟信号355之一,sar adc的dac的dnl要求可以是14位转换器和1.5v至1.75v的电压范围和在1.92v的dac内的参考电压(vref)的二分之一lsb dnl。其他模拟信号355可能具有不太严格的dnl要求。

[0024]

除了sar adc对特定电压范围具有一定的dnl要求之外,sar adc的dac的稳定时间限制了sar adc的转换速度。稳定时间是在节点n1上的电压保证已经达到其最终电压电平之前必须经过的开关sw的状态变化之后的时间。较长的稳定时间意味着较慢的数模转换。另一个需要考虑的问题是开关sw的导通电阻,它可能大到足以导致相对较大的积分非线性(inl)。下面描述的dac解决了这三个问题中的一个或多个,即(1)特定电压范围的dnl要求,(2)稳定时间,以及(3)开关导通电阻对inl的影响。结果,服务器300内的模数转换过程将具有更少的误差(对于模拟信号355中的至少一个或多个),具有更快的稳定时间,和/或具有更低的inl而不增加开关尺寸(如下所述)。在一个示例中,cpu 390读取imon、temp、vin等的数字化值,并且根据这些参数中的一个或多个的大小,修改其操作环境。例如,如果电流或温度超过相应的阈值,cpu 390可导致其操作频率或操作电压降低。cpu 390可以通过接口360向pwm ic 301提交信号或消息以引起vout的变化。因此,例如imon的数字化值越准确(由于改进的dnl性能),对cpu操作环境的控制就越有效。在该示例中,sar adc 350内的dac被配置为具有针对imon信号的信号范围的预定dnl,使得服务器300可以更有效地监视和控制其操作环境。

[0025]

当具有二进制段210的所有开关sw改变状态时,基于电阻器网络的dac的dnl在从一个数字值到下一个数字值的转变时更差。例如,对于14位的dac,对于数字值1023(十进制),最低阶10位都是“1”,因此控制二进制段210的所有10个开关sw以将那些段中的电阻器r连接到vref。下一个相邻的数字值是1024,这意味着所有的最低阶10位都是“0”,因此控制二进制段210的所有10个开关sw以将电阻器r连接到vgnd。二进制段210内的所有10个开关sw的状态变化也发生在从2047到2048、3071到3072等的转变中——每次最低阶10位从全“1”变为全“0”。

[0026]

如果电阻器r的电阻都完全相同,则dac的dnl会更低。然而,在实践中,基于电阻器的dac并不包括其所有电阻器的相同电阻。dac 108内的电阻器的电阻可以建模为r(1 σ),其中σ是电阻器的失配系数。对于给定的电阻器尺寸,在dac的电阻器两端的电阻器失配通常是随机的。也就是说,包含dac的ic制造商将保证特定尺寸的所有电阻器的失配系数(σ)的特定值。由于这个原因,示例dac 108内的电阻器都具有相同的尺寸并因此具有相同的面积(面积是指沿通过电阻器的电流路径的电阻器的横截面积)。单位电阻器r的失配系数σ本质上是高斯的。失配系数σ与电阻器面积的平方根成反比。例如,两个串联连接的单位电阻器r的有效电阻为因此,增加电阻器的面积会导致有效失配系数(即)

的降低,而dac内电阻器的失配系数的降低会导致期望的dnl降低。

[0027]

如上所述,对于dac的特定电压范围,可能期望具有较低的dnl。在上面的示例中,对于14位转换器和1.5v至1.75v的电压范围和1.92v的参考电压(vref),二分之一lsb dnl的dnl可能是期望的。对于具有1.92v参考电压的14位dac(10个二进制位和15个温度位),在1.5v到1.75v的范围内,主要数字值转换(其中所有10个二进制段210开关sw改变状态)发生在1.56v和1.68v的dac模拟输出电压下。当控制t13开关sw将其电阻器连接到vref(产生1.56v)时,以及当控制t14开关sw将其电阻器连接到vref(产生1.68v)时,就会产生这些电压。

[0028]

图4示出了dac 408的示例实施方式,dac 408具有类似于图2中的dac 108的架构,但是图2中的将二进制段210连接到温度段240的单个单位电阻器r实施为图4中单位电阻器r的四个实例(在401处示出),并且图2中t13和t14的温度段中的两个单位电阻器r中的每一个在图4的示例中被替换为两组并联的四个串联连接的单位电阻器r(在450处示出)。401处的四个单位电阻r包括两个串联连接的电阻器402和两个串联连接的电阻器403。串联连接的电阻器402与串联连接的电阻器403并联连接。节点n1和n3之间产生的有效电阻仍然是单个单位电阻器r的电阻,但是这组电阻器402和403的面积是单个单位电阻器面积的四倍。类似地,附图标记450图示了四个串联连接的单位电阻器r,其具有4r的组合电阻。当每四个串联的单位电阻器与另一组四个串联连接的单位电阻器r并联连接时,该段产生的有效电阻为2r。

[0029]

因此,节点n1和n2之间的有效电阻仍然是r,并且在t13和t14温度段内,有效电阻仍然是2r。然而,401处的四个单位电阻器的总面积是单位电阻器r的面积(a)的四倍(即4a),因此401处的两组并联的串联连接的单位电阻器的有效电阻为r(1 σ/2),因此与单个单位电阻器相比,电阻失配更小。此外,在450处t13和t14温度段中的八个单位电阻器的总面积是如图2所示串联的两个单位电阻器的面积的四倍。有利地,在450处,两组并联的串联连接的单位电阻器的有效电阻为2r(1 σ’/2),而对于图2中的两个串联连接的单位电阻器,每个此类段的有效电阻为2r(1 σ’),其中σ’是两个串联的单位电阻器的有效失配系数。因此,与图2中的对应电阻相比,图4中401和450处的有效电阻的电阻失配更小。

[0030]

dac 408因此在对应于感兴趣的模拟输出电压的某些数字值处具有较低的dnl,并且在其他数字值处可能具有较高的dnl。考虑到被数字化的特定模拟信号及其使用,dnl对于其他数字值可能更高不会对使用dac 408的sar adc的性能产生不利影响。

[0031]

图5示出了单个单位电阻器r的示例实施方式。在该示例中,单位电阻器是二氧化硅(或其他类型的电介质)层502内的多晶硅502的电阻。电介质层502形成在掺杂(例如、n掺杂)阱520上,并且掺杂阱520形成在衬底518(例如p掺杂衬底)内。电触点530和535(例如,通孔)被提供到多晶硅502的相对端。电阻515表示多晶硅502的电阻。电触点540也被提供到n阱520内的n掺杂区域545。n掺杂区域545具有比n阱520更高的掺杂浓度。在所示示例中,阱520和区域545是n掺杂的,但是在其他示例中它们可以是p掺杂的。在一个示例中,区域545是p掺杂的并且衬底518是n掺杂的,从而形成p-n结。为了避免正向偏置在p掺杂区域545和n掺杂衬底518之间形成的p-n结,施加到衬底的相同电压也施加到电触点545。该电压在图5中显示为pbkg。n阱520也可以连接到pbkg电压。

[0032]

图5中的电容器c表示在多晶硅502和n阱520之间形成的寄生体电容。寄生电容沿

多晶硅502和下面的n阱520的长度分布,但可以在数学上建模为两个电容相同的电容器c,如多晶硅502的相对端所示。

[0033]

图6图示了两个串联连接的基于多晶硅的单位电阻器。如图所示,一个电阻器的电触点530连接到另一个电阻器的电触点535。右侧基于多晶硅的电阻器上的电触点535与左侧基于多晶硅的电阻器的电触点530之间的有效电阻为2r。电容器560和562表示寄生电容c,它们通过导体558并联电连接并且两个n阱520都被偏置在相同的电压pbkg。

[0034]

图7示出了dac 108的两个二进制或温度段210、240的电路模型715,电路模型715包括电容器c1的寄生电容。每个段包括两个串联的单位电阻器r,如上所述。电容器c连接在电阻器r的每一端和pbkg电压之间。附图标记702和704指示2c电容器,其表示如上文关于图6所述的相邻电阻器之间的电容器560和562的并联组合。

[0035]

电路模型715在图7中被重新绘制为表示720,以更容易地图示dac的分布式rc网络。由于基于多晶硅的单位电阻器r的寄生电容,dac的稳定时间是r和c乘积的函数。

[0036]

图8图示了dac 808,其架构类似于图2,但每个单位电阻器r的电触点540(其连接到n阱520并因此连接到电容器c的一个端子)连接到对应的开关sw而不是连接到pbkg电压。通过给定段810或840的开关sw,单位电阻器的电触点540根据开关的状态连接到vref或vgnd。如图所示,二进制段810之间以及二进制段810和温度段840之间的电阻器具有连接到pbkg的电触点540。在图8的dac 808中,单位电阻器放置在与连接相邻二进制段810的电阻器和二进制与温度段之间的电阻器分开的阱中以及在与ic中的其他结构的阱分开的阱中。

[0037]

作为将电触点540连接到开关sw的结果,电路模型从图7中所示的模型715/720改变为图9中所示的模型910/920/930。由于电触点540与开关sw的连接,图7中的电容器770在图8中被短路,因此在图9中未示出。图9中的组合并联2c电容器连接在每个段中的上电阻器两端,如在电路模型920中更好地图示。在每个段的底部处的下电容器c连接在串联连接的单位电阻器两端,如在电路模型920中更好地图示。每个段包括两个串联连接的单位电阻器r、在两个单位电阻器两端的电容器c和在单位电阻器之一两端的2c电容器。每个段的阻抗相同并且在电路模型930中表示为阻抗z。电路模型930图示了温度段是分压器并且在阻抗z之间的节点931上的电压是vref/2。

[0038]

在dac中使用的电阻器包括n阱520,其与用于连接相邻二进制段810的电阻器以及在二进制和温度段之间的电阻器的n阱分开,并且也与ic中的其他结构的阱分开。通过使用分开的n阱并将这些阱连接到开关节点,当接通特定的温度支路时,每个这样的温度支路包括匹配阻抗网络,如上文关于图9所解释的。开关状态中的任何变化将不依赖于r和c,从而导致比图2的示例更快的稳定时间。

[0039]

再次参考图2,每个开关sw将其段连接到vref或vgnd。每个开关sw可以实现为一对晶体管,例如p型金属氧化物半导体场效应晶体管(pmos)和n型金属氧化物半导体场效应晶体管(nmos)。pmos晶体管连接到vref,当接通时,将vref连接到串联连接的电阻器。nmos晶体管连接到vgnd,当接通时,将vgnd连接到串联连接的电阻器。一般而言,面对温度或vref电压等变化,ic上pmos晶体管的导通电阻在它们之间一致地跟踪。类似地,ic上nmos晶体管的导通电阻也在它们之间一致地跟踪。

[0040]

pmos和nmos晶体管呈现在pmos和nmos晶体管之间的导通电阻将不会跨工艺和温度跟踪的约束。可以看出,由于开关电阻失配导致的inl等于:

[0041][0042]

其中在方程式(1)中的r'是单个温度段的电阻(例如,本文所述示例中的2r),inl

switch

是由于开关电阻失配导致的inl贡献。由于开关电阻失配而降低inl的一种方法是为单位电阻器r选择较大的电阻。然而,较大的电阻会导致较长的稳定时间,通常r的值由dac的稳定要求来判断。替代地,可以通过增加pmos和nmos晶体管的尺寸来减小inl

switch

,这会导致它们的导通电阻值更小。然而,不幸的是,增加晶体管的尺寸会导致更大面积的dac。

[0043]

图10和图11描述了减少inl的不同机制。图10图示了单个段1010(例如,二进制段或温度段)。电阻器r表示实现目标稳定时间t的段的电阻。也就是说,当开关1012被配置为将电阻器r连接到vref时,节点1015上的电压由于从vgnd到vref的突然变化应该在时间t内稳定下来。

[0044]

图11示出了一种实施方式,其中电阻器r被经由开关1111并联耦合的两个电阻器r2和r3代替。r2可以实现为基于多晶硅的电阻器,例如图5中所示的电阻器,r3可以实现为具有相对高的片电阻率和相对小的宽度(与电阻器r2相比)的基于多晶硅的电阻器。稳定时间段t(也称为操作时间段)分为两部分——t1和t2。在t1期间,开关1111闭合,r2和r3的并联组合的有效电阻分别小于r2或r3,且小于r。在t2期间,开关1111断开,只有大于r的电阻器r2接收电流。通过这种布置,稳定时间通常保持不变(t),因为在t1期间使用r2||r3(小于r),而在t2期间使用r2。最终稳定发生在r2(大于r),因此根据上述方程式(1),r’越大,inl越小。

[0045]

下面的方程式图示了如何选择电阻器r2和r3的值的示例。开关1111接通时间t1并且r2和r3的并联组合(有效电阻r1)通过开关1012耦合到vref。r1的有效体电容(例如,如图5所图示的r2的寄生电容)为c。时间间隔t1内的充电方程式为:

[0046][0047]

其中v1是中间电压值(即t1结束时在r1两端的电压),vx是时间段t2结束时的最终电压。

[0048]

在时间tl之后,开关1111断开(关断),并且电阻值变为r2。根据以下方程式,从中间电压v1到最终电压值(vf)发生最终稳定:

[0049][0050][0051][0052][0053]

根据方程式(6),通过在时间t1中使用电阻器r1和在时间t2中使用电阻器r2,可以在时间t1 t2中获得目标稳定的r值。例如,假设目标稳定时间需要60kω的电阻。电阻器r2可以是一个100kω的电阻器,r3可以是另一个100kω的电阻器。当开关1111闭合时,r2和r3

的并联组合的有效电阻为50kω。如果开关1111接通时间2t/3并关断时间t/3,则稳定时间将与在整个时间段t内使用单个60kω时相同。因为在时间段t结束时的电阻是100kω,所以inl会减小,而不会增加对于开关1012使用的晶体管的尺寸。

[0054]

在一个示例中,图2中的每个单位电阻器r可以如图11的示例中所示实施。在另一示例中,如图12所图示的,开关111和电阻器r5可以连接在每对串联连接的单位电阻器r4两端,而不是连接在每个个别的单位电阻器两端。如上所述,每个电阻器r4的电阻都大于图2中的r,2*r4和r5的有效并联电阻小于r。

[0055]

在整个说明书中使用术语“耦合”。该术语可以涵盖实现与本公开的说明书一致的功能关系的连接、通信或信号路径。例如,如果设备a生成信号以控制设备b执行动作,则在第一示例中,设备a耦合至设备b,或者在第二示例中,如果中间部件c不会显著改变设备a和设备b之间的功能关系,则设备a通过中间部件c耦合到设备b,使得设备b经由由设备a生成的控制信号由设备a控制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。