khz~100ghz的片内集成电容dc耦合的电路

【技术领域】

1.本技术涉及一种khz~100ghz的片内集成电容dc耦合的电路,属于电子电路技术领域。

背景技术:

2.随着光通信的迅猛发展,对高速电芯片也提出了更高的要求,比如:需要更高的带宽,更高的集成度,更低的功耗等。

3.光通信电路与常规射频电路有很多相似之处,但也有本质的不同点:即带宽要求不一样。常规射频电路是窄带系统,而光通信电路是宽带系统。无论是光通信电路,还是常规射频电路,阻抗匹配都是很关键的指标,阻抗匹配的效果直接影响了信号的传输质量。

4.但是,大多数射频电路的匹配要求都是窄带的(如gsm是中心频率900mhz,约25m频率范围的阻抗匹配,3g是中心频率1800mhz,约80m频率范围的阻抗匹配),即,在一个特定的中心频率附近(约5%)实现阻抗匹配。而对于光通信电路设计来讲,其阻抗匹配必须是宽带的,频率范围从100khz一直延伸到几十ghz;所以,常规射频电路的阻抗匹配设计不适用于电芯片的宽带阻抗匹配设计。

5.同时,对于芯片内外dc电压不一致的场景,需要采用电容对芯片内外的dc电压进行隔直。传统方案是在芯片外部加宽带隔直电容的ac耦合方案。然而,ac耦合的方式会导致芯片的封装尺寸变大、且集成度低的问题。

技术实现要素:

6.本技术提供了一种khz~100ghz的片内集成电容dc耦合的电路,可以解决常规射频电路的阻抗匹配设计不适用于电芯片的宽带阻抗匹配设计,无法实现宽带阻抗匹配的问题;通过芯片上集成电容的dc耦合方案,可以减小封装尺寸,降低成本,提高宽带阻抗匹配性。本技术提供如下技术方案:一种khz~100ghz的片内集成电容dc耦合的电路,所述电路包括:阻抗匹配结构、输入阻抗、输入级结构和片上电容;所述阻抗匹配结构通过所述片上电容与所述输入级结构相连,或者,所述片上电容通过所述阻抗匹配结构与所述输入级结构相连;所述输入阻抗与所述阻抗匹配结构相连;

7.所述阻抗匹配结构包括一端与输入端相连的匹配电感和第一匹配分支、一端与所述匹配电感的另一端和第一匹配分支的另一端分别相连的第二匹配分支;一端与所述匹配电感相连的第三匹配分支;所述第二匹配分支的另一端和所述第三匹配分支的另一端与所述输入阻抗相连;

8.其中,所述第一匹配分支、所述第二匹配分支和所述第三匹配分支均为rlc电路,所述第一匹配分支、所述第二匹配分支和所述第三匹配分支具有相同或不同的电路结构;或者,所述第一匹配分支、所述第二匹配分支和所述第三匹配分支中的一者或两者为断路,其它匹配分支为rlc电路。

9.可选地,所述rlc电路为以下结构中的一种:

10.电感;或者,

11.电容;或者,

12.电阻;或者,

13.相互并联的电感和电容;或者,

14.相互并联的电感和电阻;或者,

15.相互并联的电感和电阻;或者,

16.电容与电阻串联后与电感相并联;或者,

17.电容与电阻串联后与串联后的电感和电阻相并联;或者,

18.电容与电阻串联后与串联后的电感和电容相并联。

19.可选地,所述输入级结构包括电流源、与所述电流源相连的输入级晶体管;所述输入级晶体管和所述电流源之间引出所述电路的输出端。

20.可选地,所述输入级晶体管为cmos或者为双极型晶体管。

21.可选地,所述输入级晶体管的电压输入端输入的电压通过电阻分压得到;或者,通过电流乘以电阻得到;或者,通过低压差线性稳压器输出得到。

22.可选地,所述匹配电感为传输线或者为片上电感。

23.可选地,所述电路包括两个相互镜像的子部分,每个子部分均包括所述阻抗匹配结构、输入阻抗、输入级结构和片上电容。

24.可选地,两个子部分中的输入阻抗相连,且所述两个子部分的输出阻抗之间连接有共模滤波电容,所述共模滤波电容的另一端接地。

25.可选地,所述电路集成在同一芯片中。

26.本技术的有益效果至少包括:通过设置阻抗匹配结构、输入阻抗、输入级结构和片上电容;阻抗匹配结构包括一端与输入端相连的匹配电感和第一匹配分支、一端与匹配电感的另一端和第一匹配分支的另一端分别相连的第二匹配分支;一端与匹配电感相连的第三匹配分支;第二匹配分支的另一端和第三匹配分支的另一端与输入阻抗相连;其中,第一匹配分支、第二匹配分支和第三匹配分支均为rlc电路,第一匹配分支、第二匹配分支和第三匹配分支具有相同或不同的电路结构;或者,第一匹配分支、第二匹配分支和第三匹配分支中的一者或两者为断路,其它匹配分支为rlc电路;可以解决ac耦合的方式会导致芯片的封装尺寸变大、且集成度低的问题;通过芯片上集成电容的dc耦合方案,节省了pcb板上的大尺寸宽带电容,有效地减小了芯片的封装尺寸,可以降低成本,同时改善了宽带阻抗的连续性。同时,通过片上隔直电容实现dc耦合,同时通过改进的输入匹配网络,可以改善(减小)芯片回损s11。

27.上述说明仅是本技术技术方案的概述,为了能够更清楚了解本技术的技术手段,并可依照说明书的内容予以实施,以下以本技术的较佳实施例并配合附图详细说明如后。

【附图说明】

28.图1是本技术一个实施例提供的ac耦合方案的电路示意图;

29.图2是本技术一个实施例提供的khz~100ghz的片内集成电容dc耦合的电路示意图;

30.图3是本技术一个实施例提供的rlc电路的不同实现方式的示意图;

31.图4是本技术一个实施例提供的输入级结构的不同实现方式的示意图;

32.图5是本技术另一个实施例提供的khz~100ghz的片内集成电容dc耦合的电路示意图;

33.图6是本技术又一个实施例提供的khz~100ghz的片内集成电容dc耦合的电路示意图;

34.图7是本技术一个实施例提供的dc耦合方案相对于ac耦合方案的输入回波损耗s11仿真结果的示意图。

【具体实施方式】

35.下面结合附图和实施例,对本技术的具体实施方式做进一步详细描述。以下实施例用于说明本技术,但不用来限制本技术的范围。

36.首先,对本技术涉及的若干名词进行介绍。

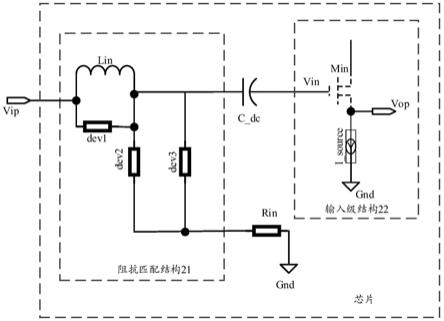

37.交流耦合(ac coupling):是指通过隔直电容耦合,去掉直流分量的耦合方式。

38.直流耦合(dc coupling):是指直流、交流一起过,而不是去掉了交流分量的耦合方式。

39.比如:在3v的直流电平上叠加一个1vpp的正弦波,如果用直流耦合,输出的是以3v为基准,

±

0.5v的正弦波;如果用交流耦合,输出的是以0v为基准,

±

0.5v的正弦波。

40.宽带芯片的常规隔直耦合(ac耦合)结构如图1所示,图1中c_pcb为pcb板上电容;ind表示电感。常规的隔直ac耦合方案,根据图1中(1)部分所示的单端ac耦合方案、(2)和(3)部分所示的为差分ac耦合方案可知,c_pcb均设置在芯片之外,以进行宽带隔直。但是,这就会导致芯片的封装尺寸变大、且集成度低的问题。

41.基于此,为减小封装,降低成本,同时改善宽带系统的阻抗一致性,本技术提供一种khz~100ghz的片内集成电容dc耦合的电路,该电路可以用于无线,微波,基站,光通信,不同模拟模块之间的信号接口等场景,本实施例不对该电路的应用场景作限定。下面对该电路进行介绍。

42.图2是本技术一个实施例提供的khz~100ghz的片内集成电容dc耦合的电路的电路示意图,根据图2可知,该电路包括:阻抗匹配结构21、输入阻抗rin、输入级结构22和片上电容c_dc。

43.阻抗匹配结构21通过片上电容与输入级结构22相连,或者,片上电容通过阻抗匹配结构21与输入级结构22相连;输入阻抗rin与阻抗匹配结构21相连。

44.换言之,阻抗匹配结构21与片上电容之间可以互换位置。

45.参考图2,阻抗匹配结构21包括一端与输入端vip相连的匹配电感lin和第一匹配分支dev1、一端与匹配电感lin的另一端和第一匹配分支dev1的另一端分别相连的第二匹配分支dev2;一端与匹配电感lin相连的第三匹配分支dev3;第二匹配分支dev2的另一端和第三匹配分支dev3的另一端与输入阻抗rin相连。

46.其中,第一匹配分支dev1、第二匹配分支dev2和第三匹配分支dev3均为rlc电路,第一匹配分支dev1、第二匹配分支dev2和第三匹配分支dev3具有相同或不同的电路结构。

47.或者,第一匹配分支dev1、第二匹配分支dev2和第三匹配分支dev3中的一者或两者为断路,其它匹配分支为rlc电路。不同的其它匹配分支之间的电路结构相同不同。换言

之,第一匹配分支dev1、第二匹配分支dev2和第三匹配分支dev3不全部为断路。

48.参考图3,rlc电路为以下结构中的一种:图3(1)中所示的电感;或者,图3(2)中所示的电容;或者,图3(3)中所示的电阻;或者,图3(4)中所示的相互并联的电感和电容;或者,图3(5)中所示的相互并联的电感和电阻;或者,图3(6)中所示的相互并联的电感和电阻;或者,图3(7)中所示的电容与电阻串联后与电感相并联;或者,图3(8)中所示的电容与电阻串联后与串联后的电感和电阻相并联;或者,图3(9)中所示的电容与电阻串联后与串联后的电感和电容相并联。

49.输入级结构22包括电流源i_source、与电流源i_source相连的输入级晶体管min;输入级晶体管min和电流源i_source之间引出电路的输出端vop。

50.示意性地,输入级晶体管min为cmos或者为双极型晶体管。比如:参考图4所示的输入级结构22的具体实现时的示意图,根据图4中的(1)可知,输入级晶体管min可以为pmos,此时,电流源i_source的另一端接地。根据图4中的(2)可知,输入级晶体管min还可以为nmos,此时nmos的一端接地。根据图4中的(3)可知,输入级晶体管min还可以为npn型晶体管,此时,电流源i_source的另一端接地。根据图4中的(4)可知,输入级晶体管min还可以为pnp型晶体管,此时,pnp型晶体管的一端接地。

51.输入级晶体管min的电压输入端vin输入的电压包括输入级晶体管min的工作直流电压。可选地,电压输入端vin输入的电压通过电阻分压得到;或者,通过电流乘以电阻得到;或者,通过低压差线性稳压器(low dropout regulator,ldo)输出得到。

52.可选地,匹配电感lin为传输线或者为片上电感。

53.可选地,输入阻抗rin通常为50欧姆,在实际实现时,输入阻抗rin的阻抗值也可以自适应地设置为其它数值,本实施例不对输入阻抗rin的取值作限定。

54.图1中以单端dc耦合为例进行说明,此时,输入阻抗rin的另一端接地。

55.在实际实现时,电路还可以实现为差分dc耦合。具体地,参考图5,此时电路包括两个相互镜像的子部分51和52,每个子部分均包括阻抗匹配结构21、输入阻抗rin、输入级结构22和片上电容。其中,子部分51和52的输出阻抗相连。

56.可选地,参考图6,两个子部分中的输入阻抗rin相连,且两个子部分的输出阻抗之间连接有共模滤波电容c_cm,共模滤波电容c_cm的另一端接地。

57.本实施例中,上述电路集成在同一芯片中,从而提高芯片的集成度,并可以降低输入回波损耗s11。为了更清楚地表示本技术提供的dc耦合方案相对于ac耦合方案改善的输入回波损耗s11,参考图7所示的dc耦合方案(参考图7中的s11 updated对应的曲线)和ac耦合方案(参考图7中的s11original对应的曲线)的输入回波损耗s11的仿真结果。根据图7可知,改进之后的dc耦合方案与传统的ac耦合方案相比,芯片输入回波损耗s11改善(减小)了17db以上,从1.0ghz一直到60ghz,改进之后的dc耦合方案的s11明显小于改进之前的ac耦合方案的s11。

58.综上所述,本实施例提供的khz~100ghz的片内集成电容dc耦合的电路,通过设置阻抗匹配结构21、输入阻抗rin、输入级结构和片上电容;阻抗匹配结构21包括一端与输入端vip相连的匹配电感lin和第一匹配分支dev1、一端与匹配电感lin的另一端和第一匹配分支dev1的另一端分别相连的第二匹配分支dev2;一端与匹配电感lin相连的第三匹配分支dev3;第二匹配分支dev2的另一端和第三匹配分支dev3的另一端与输入阻抗rin相连;其

中,第一匹配分支dev1、第二匹配分支dev2和第三匹配分支dev3均为rlc电路,第一匹配分支dev1、第二匹配分支dev2和第三匹配分支dev3具有相同或不同的电路结构;或者,第一匹配分支dev1、第二匹配分支dev2和第三匹配分支dev3中的一者或两者为断路,其它匹配分支为rlc电路;可以解决ac耦合的方式会导致芯片的封装尺寸变大、且集成度低的问题;通过芯片上集成电容的dc耦合方案,节省了pcb板上的大尺寸宽带电容,有效地减小了芯片的封装尺寸,可以降低成本,同时改善了宽带阻抗的连续性。同时,通过片上隔直电容c_dc实现dc耦合,同时通过改进的输入匹配网络,可以改善(减小)芯片的输入回波损耗s11。

59.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

60.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。