高速串行rapidio通用测试系统和方法

技术领域

1.本发明属于雷达测试技术领域,具体涉及一种高速串行rapidio通用测试系统和方法。

背景技术:

2.rapidio技术是一项点对点的嵌入式系统互连的国际标准,为高性能嵌入式处理器系统内部和嵌入式系统之间提供了高效可靠地互连和数据交换,广泛应用于现代通信系统和雷达等电子武器装备中。高速串行rapidio技术是rapidio技术的一个分支,目前主流嵌入式处理器系统设计多采用串行rapidio技术。

3.实际测试中,rapidio在实际电子系统应用中非常复杂多样,即使在同一个系统中,uut有多个品种,rapidio总线信号分布在vpx总线的不同连接器上,数据传输速率和工作通道模式也有很大不同。当前对于rapidio的测试已经有些成熟的测试方法,但仅限于信号完整性、眼图、接收性能和误码率等物理特性的测试,还没有针对rapidio数据传输和交换等逻辑功能测试的通用技术和方法。相应地,针对雷达系统中基于vpx总线高速数字电路模块,高速串行rapidio技术大量应用,目前缺乏有效地通用功能测试手段。对于雷达模块大量的调试、测试、维护、维修和验证需求来说,在实际的调试和测试中,采用的方法是将具有rapidio功能的高速数字模块置于专用的具有相应互联关系的测试插箱中,使用另外的专用高速测试模块和专用接口模块(后插板)来实现rapidio总线信号的测试通路建立和测试资源的配备,以完成rapidio的调试和功能测试。这种方式存在以下问题:

4.1、测试方法不统一,每个模块采用各自测试调试程序,测试流程开发成本高昂;

5.2、受系统互连拓扑关系限制,必须使用专用模块或专用接口模块配合完成测试,必须使用专用插箱,构建测试系统非常复杂,测试系统设计成本高昂,每种专用模块或专用接口模块都需要有专门的测试方法和测试流程,测试流程开发成本高昂。

6.因此rapidio通用测试方法和测试技术研究有着紧迫的需求和必要。

技术实现要素:

7.本发明目的是:针对现有技术的不足,提供一种高速串行rapidio通用测试系统和方法,能够解决雷达系统中基于vpx总线高速数字电路模块rapidio通用测试难题,规范rapidio测试方法,节约测试成本和系统设计成本,简化测试系统组成,提升新一代雷达的综合保障能力和保障水平。

8.具体地说,本发明是采用以下技术方案实现的。

9.一方面,本发明提供一种高速串行rapidio通用测试系统,包括通用rapidio测试器、通用rapidio测试适配器、通用vpx总线测试插箱;

10.所述通用rapidio测试器包括主测试模块、以太网口、光纤接口;所述通用rapidio测试器,通过所述光纤接口提供若干路x1模式串行rapidio测试通道,所述测试通道数达到vpx总线被测模块的高速串行数据发送和接收的最大串行通道数;所述主测试模块包括高

性能嵌入式处理器和至少一个高性能fpga;所述高性能嵌入式处理器,通过所述以太网口接收和解析上位机指令,根据指令内容,控制主测试模块工作状态;所述fpga提供高速串行rapidio测试资源和多路rapidio测试通道,完成高速串行数据发送和接收;

11.所述通用rapidio测试适配器包括若干vpx总线连接器;所述通用rapidio测试适配器实现被测uut的rapidio信号和rapidio测试器的测试通道之间信号转接,构成rapidio电气接口的点对点通信路径;对vpx总线连接器的所有高速串行接口进行全扩展,对外以光纤接口形式实现;

12.所述通用vpx总线测试插箱提供被测uut的工作电源以及背板连接;所述背板基于vpx总线,包括至少一个测试槽位;测试槽位的p1~p6连接器与其它槽位没有互连关系,该测试槽位前后连接器信号按照vpx总线标准定义进行全对接,以满足测试要求。

13.进一步地,所述高性能嵌入式处理器为cpu处理器。

14.进一步地,所述fpga实现数据传输速率动态选择。

15.进一步地,所述高速串行rapidio测试资源采用fpga内部ip核模块实现,rapidio物理层链路连接利用fpga内部gt资源实现,其中每个fpga提供32路高速x1模式rapidio测试通道;所述光纤接口采用24合1光电模块完成光电信号之间的转换,分为发送和接收两种;fpga所有gt接口的发送部分采用若干个24合1光电发送模块设计光纤接口,所有gt接口的接收部分采用若干个24合1光电接收模块设计光纤接口。

16.进一步地,所述每个vpx总线连接器按16路x1通道计算,共计最高96路x1通道,采用4个24合1光电发送模块和4个24合1光电接收模块设计光纤接口。

17.进一步地,所述适配器物理尺寸上采用6u标准后插板向外延伸形式,在后插板外侧边缘实现光纤接口连接器紧密排布。

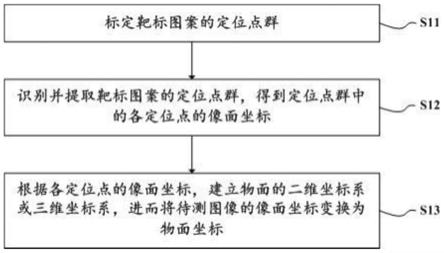

18.另一方面,本发明还提供一种高速串行rapidio通用测试方法,采用上述高速串行rapidio通用测试系统实现,包括以下步骤:

19.完成通用rapidio测试器的主测试模块中fpga的rapidio通道配置,完成初始化数据配置;

20.高性能嵌入式处理器接收配置数据和测试指令,并进行解析,控制fpga完成相应的初始化操作;

21.高性能嵌入式处理器根据测试指令选择相应的测试数据,先通过通用rapidio测试适配器与被测uut建立rapidio链接,再将测试数据发送给被测uut;

22.高性能嵌入式处理器接收被测uut的测试结果。

23.本发明的高速串行rapidio通用测试系统和方法的有益效果如下:

24.通过通用rapidio测试器提供96路x1模式串行rapidio测试通道,能够完成最高96路高速串行数据发送和接收,能够满足vpx总线被测模块的最高串行总线通道数,解决了测试资源不足的问题,为高速串行rapidio提供了通用的功能测试方法,规范rapidio测试方法;

25.通过以太网口和上位机通信,采用8个24合1光电转换模块作为对外测试光纤接口,可实现96路x1模式rapidio收发调试和测试,rapidio通道模式、数据通道传输波特率可配置,能适应不同被测模块的测试需求,满足不同通道模式、不同的数据传输速率测试要求,具备了测试资源通用化的能力,摆脱了专用测试资源的约束;通过vpx总线全扩展的设

计解决了不同uut的vpx总线高速串行信号分布不均的问题,脱离了使用专用接口模块和专用插箱的限制,降低测试系统构建的成本,不再需要多种专用测试模块、专用接口模块和多种专用测试机箱;简化rapidio调试和测试的开发流程,为测试系统设计提供通用设备和便利方法;

26.通过多合一光纤接口的设计减小了通道尺寸,保证了长距离传输过程中的信号质量,有利于测试系统设计,提高了雷达系统和模块的综合保障水平和综合保障能力。

附图说明

27.图1是本实施例的高速串行rapidio通用测试系统测试框图,(a)(b)(c)分别为高速串行rapidio通用测试系统对通用vpx总线测试插箱中被测电路模块uut1、uut2、uut3进行测试的框图。

28.图2是本实施例的通用rapidio测试器示意框图。

29.图3是本实施例的通用rapidio主测试模块功能框图。

30.图4是本实施例的通用rapidio测试适配器示意图。

31.具体实施

32.下面结合实施例并参照附图对本发明作进一步详细描述。

33.实施例1:

34.本发明的一个实施例,为一种高速串行rapidio通用测试系统及测试方法,用于对vpx总线高速数字模块即被测电路模块(uut)进行测试。

35.如图1所示,本实例的高速串行rapidio通用测试系统包括:通用rapidio测试器、通用rapidio测试适配器、通用vpx总线测试插箱。高速串行rapidio通用测试系统可以对通用vpx总线测试插箱中不同被测电路模块uut1、uut2、uut3进行rapidio收发调试和测试。

36.1、通用rapidio测试器

37.通用rapidio测试器主要功能是通过光纤接口形式提供96路x1模式串行rapidio测试通道,能够完成最高96路高速串行数据发送和接收。96路为满足vpx总线被测模块的最大串行总线通道数,解决了测试资源不足的问题。可以理解,也可以采用48路或其他低于96路的x1模式串行rapidio测试通道,只要根据实际测试需要,达到能够满足实现所有被测模块的高速串行数据发送和接收的串行通道数即可。

38.通用rapidio测试器设计为高度为1u的可上架设备,由主测试模块、以太网口、光纤接口组成,如图2所示,优选地,还可以包括风机、电源模块、。通用rapidio测试器通过以太网口和上位机通信;采用8个24合1光电转换模块作为对外测试光纤接口,可实现96路x1模式rapidio收发调试和测试。rapidio通道模式可配置为x1、x2、x4、x8,数据通道传输波特率可配置为1.25gbps、2.5gbps、3.125gbps、5gbps、6.25gbps。本实施例的高速串行rapidio通用测试系统具备上述配置能力后,能够适应不同被测模块的测试需求,满足多种串行rapidio通道模式、不同数据传输速率的测试要求,具备测试资源通用化的能力,摆脱了专用测试资源的约束。

39.主测试模块是通用rapidio测试器核心部件,采用高性能嵌入式处理器 至少一个高性能fpga为主架构设计实现。fpga根据需要进行的rapidio测试通道数确定。如图3所示,主测试模块采用cpu处理器 3个fpga的主架构设计实现。其中,cpu处理器(即高性能嵌入式

处理器)主要功能是控制主测试模块工作状态,通过以太网口接收和解析上位机指令,根据指令内容,实施具体操作控制。fpga主要功能是提供高速串行rapidio测试资源和多路rapidio测试通道,每个fpga提供32路x1模式串行rapidio测试通道,能够完成最高96路高速串行数据发送和接收,能够满足vpx总线被测模块的最高串行总线通道数,解决了测试资源不足的问题。fpga实现数据传输速率动态选择,满足不同数据传输速率的测试要求。高速串行rapidio测试资源采用fpga内部ip核模块实现,rapidio物理层链路连接利用fpga内部gt(高速串行收发器)资源实现,其中每个fpga提供32路高速x1模式rapidio测试通道。24合1光电模块用于完成光电信号之间的转换,分为发送和接收两种模块。fpga所有96个gt接口的tx(发送)部分采用4个24合1光电发送模块设计光纤接口,所有96个gt接口的rx(接收)部分采用4个24合1光电接收模块设计光纤接口。通过上述两种光口连接器(发送光模块和接收光模块)组合,实现96路x1模式rapidio收发组合调试和测试。多合一(24合1)光纤接口减小了通道尺寸,保证了长距离传输过程中的信号质量,有利于测试系统设计。

40.2、通用rapidio测试适配器

41.通用rapidio测试适配器用于实现被测vpx总线高速数字模块(uut)的rapidio信号和rapidio测试器的测试通道之间信号转接,构成rapidio电气接口的点对点通信路径。6u高vpx总线(vita 46.3标准)连接器包括7个连接器,序号p0-p6。p0主要用于供电,p1-p6中每个连接器最多支持定义16组高速串行收发信号。通用rapidio测试适配器对标准6u高度的vpx总线连接器的所有标准约定的高速串行接口定义引脚(从p1到p6)进行全扩展,对外以光纤接口形式实现设计。每个连接器按16路x1通道计算,共计最高96路x1通道,采用4个24合1光电发送模块和4个24合1光电接收模块设计光纤接口。适配器物理尺寸上采用6u标准后插板向外延伸形式,在后插板外侧边缘实现光纤接口连接器紧密排布,可根据具体uut测试需要选装光口连接器,以节约成本,如图4所示。vpx总线全扩展的设计解决了不同uut的vpx总线高速串行信号分布不均的问题,脱离了使用专用接口模块和专用插箱的限制。

42.3、通用测试插箱

43.通用测试插箱提供了测试工作环境,用于提供uut工作电源、散热,以及背板连接。通用测试插箱背板基于vpx总线,包括至少一个测试槽位。测试槽位的p1-p6连接器与其它槽位没有互连关系,该测试槽位前后连接器信号按照标准定义进行全对接,以满足测试要求。

44.在另一个实施例中,vpx总线高速数字模块是被测模块(uut),vpx总线p1连接器上有4路x4串行rapidio总线信号,p3连接器上有4路x4串行rapidio总线信号。数据传输波特率2.5gbps。uut的p1、p3连接器上的各4路x4串行rapidio总线信号,通过背板连至通用rapidio测试适配器的p1、p3连接器,再至通用rapidio测试适配器的xs1-xs4光口;再通过光纤电缆分别连接到通用rapidio测试器的xs1-xs4光口,再至通用rapidio测试器的fpga1和fpga2的gt接口,再至fpga1和fpga2内部的rapidio功能ip核模块,形成所有rapidio测试通路。

45.本实施例的高速串行rapidio通用测试方法的执行过程如下:

46.1、启动上位机的测试软件,完成通用rapidio测试器的主测试模块中fpga的rapidio通道配置,完成数据传输速率选择等初始化数据配置,通过以太网口将配置数据和

测试指令发送给主测试模块中的高性能嵌入式处理器(cpu)。

47.2、高性能嵌入式处理器接收上位机发来的配置数据和测试指令,并进行解析,控制fpga完成相应的初始化操作。

48.3、进行测试时,高性能嵌入式处理器根据测试指令选择相应的测试数据,先通过通用rapidio测试适配器与被测uut建立rapidio链接,再将测试数据发送给被测uut。

49.4、高性能嵌入式处理器接收被测uut的测试结果,完成最终结果处理。

50.本发明将所有vpx总线上所有可能分布的串行rapidio总线信号全部通过后插板上的通用rapidio测试适配器引出,通过光纤连接到通用rapidio测试器的测试资源,实现了rapidio的通用测试;减少了测试系统硬件品种,如专用测试模块、专用接口模块、专用插箱等,规范了测试方法,减少了开发流程,节约了测试成本,简化了系统设计。

51.例如,如果uut1、uut2、uut3的rapidio总线信号分布在vpx总线的不同连接器上,采用以往的测试方法时,需要配备具有相应的互连关系的专用插箱、专用模块、专用接口模块(后插),实现rapidio总线信号的测试通路建立和测试资源的配备。本发明克服了上述问题,将所有vpx总线上所有可能分布的串行rapidio总线信号的标准定义引脚进行全扩展设计,全部通过后插的通用rapidio测试适配器引出,通过光纤电缆连接到用rapidio测试器的测试资源通道,实现了rapidio的通用测试。减少了测试系统硬件品种,如专用模块、专用接口模块、专用插箱等等,规范了测试方法,减少了开发流程,节约了测试成本,简化了系统设计。

52.在一些实施例中,上述技术的某些方面可以由执行软件的处理系统的一个或多个处理器来实现。该软件包括存储或以其他方式有形实施在非暂时性计算机可读存储介质上的一个或多个可执行指令集合。软件可以包括指令和某些数据,这些指令和某些数据在由一个或多个处理器执行时操纵一个或多个处理器以执行上述技术的一个或多个方面。非暂时性计算机可读存储介质可以包括例如磁或光盘存储设备,诸如闪存、高速缓存、随机存取存储器(ram)等的固态存储设备或其他非易失性存储器设备。存储在非临时性计算机可读存储介质上的可执行指令可以是源代码、汇编语言代码、目标代码或被一个或多个处理器解释或以其他方式执行的其他指令格式。

53.计算机可读存储介质可以包括在使用期间可由计算机系统访问以向计算机系统提供指令和/或数据的任何存储介质或存储介质的组合。这样的存储介质可以包括但不限于光学介质(例如,光盘(cd)、数字多功能光盘(dvd)、蓝光光盘)、磁介质(例如,软盘、磁带或磁性硬盘驱动器)、易失性存储器(例如,随机存取存储器(ram)或高速缓存)、非易失性存储器(例如,只读存储器(rom)或闪存)或基于微机电系统(mems)的存储介质。计算机可读存储介质可以嵌入计算系统(例如,系统ram或rom)中,固定地附接到计算系统(例如,磁性硬盘驱动器),可移除地附接到计算系统(例如,光盘或通用基于串行总线(usb)的闪存),或者经由有线或无线网络(例如,网络可访问存储(nas))耦合到计算机系统。

54.请注意,并非上述一般性描述中的所有活动或要素都是必需的,特定活动或设备的一部分可能不是必需的,并且除了描述的那些之外可以执行一个或多个进一步的活动或包括的要素。更进一步,活动列出的顺序不必是执行它们的顺序。而且,已经参考具体实施例描述了这些概念。然而,本领域的普通技术人员认识到,在不脱离如下权利要求书中阐述的本公开的范围的情况下,可以进行各种修改和改变。因此,说明书和附图被认为是说明性

的而不是限制性的,并且所有这样的修改被包括在本公开的范围内。

55.上面已经关于具体实施例描述了益处、其他优点和问题的解决方案。然而,可能导致任何益处、优点或解决方案发生或变得更明显的益处、优点、问题的解决方案以及任何特征都不应被解释为任何或其他方面的关键、必需或任何或所有权利要求的基本特征。此外,上面公开的特定实施例仅仅是说明性的,因为所公开的主题可以以受益于这里的教导的本领域技术人员显而易见的不同但等同的方式进行修改和实施。除了在下面的权利要求书中描述的以外,没有意图限制在此示出的构造或设计的细节。因此明显的是,上面公开的特定实施例可以被改变或修改,并且所有这样的变化被认为在所公开的主题的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。