1.本发明涉及电子电路设计技术领域,具体来说,涉及一种数字脉宽捕获系统及方法。

背景技术:

2.在mcu(微控制单元,microcontrollerunit)芯片中,通常需要通过数字捕获单元(digital capture unit)对外部输入的数字信号的周期、占空比等进行测量。一般的,该单元包含每周期计数值递增的定时器,可配置在信号的上升沿或下降沿(或者双沿)记录该时刻下定时器的计数值并保存;随后通过软件或者硬件的方式计算信号的周期或占空比等。某些场合下,数字捕获单元需要有较高的测量精度,例如达到100ps级甚至更高的精度。

3.目前有主要通过提高输入时钟频率的方式来提高数字输入脉宽测量精度,如果需要进一步提高测量的精度,则需要提高定时器的输入时钟频率,例如,对于1ns精度,则输入时钟频率需大于1ghz;或者通过高速采样芯片(例如某些示波器可以提供大于20g的采样率),后对采样信号进行分析已得到较为精确的测量值。前者由于频率过高,在芯片实现时难以满足时序要求,后者需要极高的成本。

4.而对于在实际应用中被大量使用的mcu芯片,其工作频率往往远远小于1ghz(对应1ns精度)。因此需要寻找一种在较低的工作频率(例如100mhz)下达到较高测量精度(例如100ps)的方法。

技术实现要素:

5.为了解决现有技术存在的不足,本发明的目的在于提供一种数字脉宽捕获系统及方法,在较低的输入时钟频率下,能够显著提高对于数字输入信号脉宽测量(捕获)精度,便于在芯片尤其是工作频率较低的芯片中实现。

6.为实现上述目的,本发明提供的数字脉宽捕获系统,包括,逐级延时单元、边沿检测单元、最先边沿检测单元、fifo及控制单元,以及数字定时器,其中,所述逐级延时单元,其对主时钟信号进行逐级延时,生成多个逐级延时时钟信号;多个所述边沿检测单元的每一个,利用所述逐级延时时钟信号对输入信号的边沿进行检测,输出逻辑电平为

‘1’

的边缘检测信号;所述最先边沿检测单元,对多个所述边缘检测信号进行检测,将最先发生跳变的路径编号作为测量值的小数部分输出;所述数字定时器,其利用输入的主时钟信号对输入信号进行测量,生成测量值的整数部分输出;所述fifo及控制单元,其将所述测量值的整数部分和所述测量值的小数部分结合,获得最终的测量值输出。

7.进一步地,所述逐级延时单元,包括,主延时线、从延时线控制单元、从延时线,其中,

所述主延时线,其根据接收的主时钟信号,生成控制信号发送给所述从延时线控制单元;所述从延时线控制单元,其根据所述控制信号,生成多个延时单元控制信号,分别发送给多个所述从延时线;多个所述从延时线的每一个,根据所述延时单元控制信号,控制主时钟信号的延时时间,生成多个逐级延时时钟信号输出给对应的所述边沿检测单元。

8.进一步地,所述从延时线控制单元,根据所述主延时线输出的控制信号,确定需要的延时单元和延时单元控制信号的数目。

9.进一步地,所述主延时线,包括,相位检测控制单元和延时单元,其中,所述相位检测控制单元,其输入端分别连接主时钟信号和多个逐级相连的所述延时单元中最后一个的输出端;其输出端输出控制信号,控制每一个所述延时单元的使能或者直通,将相位偏差调整到半个主时钟信号周期;多个逐级相连的所述延时单元的第一级输入连接主时钟信号,最后一级输出连接所述相位检测控制单元的一个输入端。

10.更进一步地,所述边沿检测单元结构,包括,d触发器和异或门,其中,所述d触发器,其cp输入端与所述逐级延时单元的输出端相连接,d输入端连接输入信号;其输出端与所述异或门的一个输入端相连接;所述异或门的另一个输入端连接主时钟信号,当输入信号有跳变时,其输出端输出逻辑电平为

‘1’

的边缘检测信号。

11.为实现上述目的,本发明还提供一种数字脉宽捕获方法,包括以下步骤:1)利用数字定时器对输入信号进行测量,将测量结果作为测量值的整数部分;2)对主时钟信号进行逐级延时,生成多个逐级延时时钟信号;3)利用逐级延时时钟信号对输入信号的边沿进行检测,生成边缘检测信号;4)从边缘检测信号中检测出最先发生跳变的路径,并将输出路径编号作为测量值的小数部分;5)将测量值的整数部分与测量值的小数部分结合,获得最终的测量值。

12.进一步地,所述步骤2)还包括,探测输入时钟和输出时钟之间的相位偏差,并生成控制信号;根据控制信号,确定延时单元和延时单元控制信号的数目;根据所述延时单元控制信号,控制主时钟信号的延时时间,生成多个逐级延时时钟信号。

13.更进一步地,所述步骤3)还包括,利用所述逐级延时时钟信号检测输入信号,当输入信号有跳变时,输出逻辑电平为

‘1’

的边缘检测信号。

14.为实现上述目的,本发明还提供一种数字脉宽捕获芯片,包括,上述的数字脉宽捕获系统。

15.为实现上述目的,本发明还提供一种数字脉宽捕获装置,包括,上述数字脉宽捕获芯片。

16.为实现上述目的,本发明还提供一种电子设备,包括处理器,以及存储器,所述存储器存储有计算机程序,该计算机程序在被所述处理器读取执行时,执行上述数字脉宽捕

获方法的步骤。

17.为实现上述目的,本发明还提供一种计算机可读存储介质,所述计算机可读存储介质中存储有计算机程序,该计算机程序被设置为运行时执行上述数字脉宽捕获方法的步骤。

18.本发明的数字脉宽捕获系统及方法,与现有技术相比较,具有以下有益效果:对输入时钟信号延时后进行多次采样,检测在一个主时钟周期内最先发生跳变的路径(作为小数部分),结合主延时线上输入时钟信号的计数(整数部分)得到精确的测量值。假设输入主时钟的周期为t,在采用n条延时单元的情况下,则测量的时间分辨率为可达t/n,即精度增大了n倍,在输入时钟频率不增加的情况下显著提高了数字脉宽捕获的精度。

19.本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。

附图说明

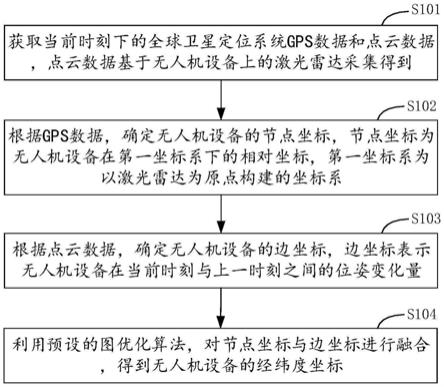

20.附图用来提供对本发明的进一步理解,并且构成说明书的一部分,并与本发明的实施例一起,用于解释本发明,并不构成对本发明的限制。在附图中:图1为根据本发明的数字脉宽捕获系统结构示意图;图2为根据本发明的逐级延时单元结构示意图;图3为根据本发明的输入脉冲信号经过逐级延时单元后的波形示意图;图4为根据本发明的主延时线结构示意图;图5为根据本发明的从延时线结构示意图;图6为根据本发明的边沿检测单元结构示意图;图7为根据本发明的数字脉宽捕获方法流程图;图8为根据本发明的一个应用实施例场景示意图。

具体实施方式

21.以下结合附图对本发明的优选实施例进行说明,应当理解,此处所描述的优选实施例仅用于说明和解释本发明,并不用于限定本发明。

22.需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括

……”

限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

23.本发明所提供的技术方案主要应用于汽车电子电路,对于在实际应用中被大量使用的mcu芯片,其工作频率往往远远小于1ghz(对应1ns精度),目前有主要通过提高输入时钟频率的方式来提高数字输入脉宽测量精度,如果需要进一步提高测量的精度,则需要提高定时器的输入时钟频率,或者通过高速采样芯片,前者由于所需频率过高,在芯片实现时难以满足时序要求,后者需要极高的成本。

24.本发明实施例中提出主延时线(master dll)和从延时线(slave dll)通过主延时线和多个从延时线达到对输入主时钟进行逐级延时的效果,这些被逐级延时的时钟输入下级的边沿检测单元用于对输入信号边沿的检测。

25.实施例1图1为根据本发明的数字脉宽捕获系统结构示意图,如图1所示,本发明的数字脉宽捕获系统,包括,逐级延时单元10、边沿检测单元20、最先边沿检测单元30、fifo及控制单元40,以及数字定时器50,其中,逐级延时单元10,对接收的主时钟信号(clk_0)进行逐级延时,生成多个逐级延时时钟信号(clk_1、clk_2

……

clk_n-1),分别发送给对应的多个边沿检测单元20。

26.多个边沿检测单元20的每一个,接收来自逐级延时单元10的逐级延时时钟信号,并利用逐级延时时钟信号对输入信号(input)的边沿进行检测,检测每条路径上的输入信号是否有跳变,其为组合逻辑,当输入信号有跳变时其输出逻辑电平为

‘1’

的边缘检测信号(edge_detected_x)。

27.最先边沿检测单元30,其接收来自多个边沿检测单元20的边缘检测信号(edge_detected_1、edge_detected_2

……

edge_detected_n-1),其为组合逻辑,检测在一个主时钟周期内最先发生跳变的路径并将输出路径编号作为测量值的小数部分在下个主时钟信号的上升沿发送给fifo及控制单元40。

28.数字定时器50,其利用输入的主时钟信号对输入信号进行测量,并将测量结果作为测量值的整数部分发送给fifo及控制单元40。

29.fifo及控制单元40,其分别接收来自数字定时器50的测量值的整数部分和最先边沿检测单元30的测量值的小数部分,在主时钟信号的上升沿将测量值的整数部分和小数部分(edge_detected_out)push进fifo,以供后续软件进行读取。

30.图2为根据本发明的逐级延时单元结构示意图,如图2所示,本发明的逐级延时单元10,包括,主延时线11、从延时线控制单元(slave dll cfg)12、从延时线13,其中,主延时线11,其根据接收的主时钟信号,生成控制信号(dly_cell_n[n:0])发送给从延时线控制单元12。

[0031]

从延时线控制单元12,其根据来自主延时线11的控制信号,生成多个延时单元控制信号(dll_ctl_1、dll_ctl_2

……

dll_ctl_n-1),分别发送给从延时线13。

[0032]

本发明实施例中,从延时线控制单元12,根据主延时线11输出的dly_cell_n(代表延时180度需要的delay cell的数目)生成各个从延时线的控制信号dll_ctl_x。其中dll_ctl_x=dly_cell_n*2/n*x。

[0033]

多个从延时线13的每一个,根据接收的从延时线控制单元12的延时单元控制信号控制主时钟信号的延时时间,生成多个逐级延时时钟信号(clk_1、clk_2

……

clk_n-1)分别输出给对应的边沿检测单元20。

[0034]

图3为根据本发明的输入脉冲信号经过逐级延时单元后的波形示意图,如图3所示,从延时线控制单元12根据主延时线11输出的dly_cell_n(代表延时180度需要的delay cell的数目)生成各个从延时线的控制信号dll_ctl_x。其中dll_ctl_x=dly_cell_n*2/n*x。经各个从延时线延时后的各个时钟(clk_1到clk_n-1)波形及其相位关系,tdelay_1为时钟信号clk_1的延时时间,tdelay_n-1为时钟信号clk_n-1的延时时间。假设clk_0(主时钟)

的周期为t,则tdelay_1 = t/n, tdelay_2 = 2*t/n, and tdelay_n-1 =(n-1)/ n * t; clk_1到clk_n-1的周期不变,依然为t。

[0035]

图4为根据本发明的主延时线结构示意图,如图4所示,本发明的主延时线11,包括,相位检测控制单元(phase detect and control unit)110、多个延时单元(delaycell,延时单元-1、延时单元-2

……

延时单元-n),其中,相位检测控制单元110,其输入端分别连接主时钟信号和多个延时单元中最后一个延时单元的输出端,其输出端输出控制信号(dly_cell_n[n:0])控制每一个delay cell的使能或者bypass将相位偏差调整到半个主时钟信号周期(即180度)。

[0036]

多个延时单元(延时单元-1、延时单元-2

……

延时单元-n)的输入端和输出端逐级相连,第一级延时单元的输入端连接主时钟信号,最后一级延时单元的输出端连接相位检测控制单元110的输入端。

[0037]

本发明实施例中,主延时线11通过phase detect and control unit探测输入时钟和输出时钟(clk_out)之间的相位偏差,并生成控制信号dly_cell_n[n:0]控制delay cell的使能或者bypass将相位偏差调整到半个clk_in周期(即180度)。对于每个delay cell,如使能则对其输入的时钟产生的延时。如果clk_out的频率产生变化(例如因为温度变化),phase detect and control unit会动态调整dly_cell_n[n:0]的值以确保相位偏差调整到半个clk_in周期,此时dly_cell_n[n:0]* =clk_in周期/2。

[0038]

图5为根据本发明的从延时线结构示意图,如图5所示,本发明的从延时线13,除不需要相位检测控制单元之外,其他部分和主延时线11结构相同,不再赘述。

[0039]

图6为根据本发明的边沿检测单元结构示意图,如图6所示,本发明的边沿检测单元20,包括,d触发器21和异或门22,其中,d触发器21的cp输入端与逐级延时单元10的输出的逐级延时时钟信号相连接,d输入端连接输入信号,其输出端与异或门22的一个输入端相连接。

[0040]

异或门22的另一个输入端连接主时钟信号,当输入信号有跳变时,其输出端输出逻辑电平为

‘1’

的边缘检测信号(edge_detected_x)。

[0041]

实施例2本发明还提供一种数字脉宽捕获方法。图7为根据本发明的数字脉宽捕获方法流程图,下面将参考图7,对本发明的数字脉宽捕获方法进行详细描述。

[0042]

首先,在步骤701,利用数字定时器对输入信号进行测量,将测量结果作为测量值的整数部分。

[0043]

在步骤702,对主时钟信号进行逐级延时,生成多个逐级延时时钟信号。

[0044]

本发明实施例中,主延时线11的相位检测控制单元探测输入时钟和输出时钟之间的相位偏差,并生成控制信号dly_cell_n[n:0];从延时线控制单元12根据控制信号dly_cell_n[n:0]生成各个延时单元控制信号;从延时线根据延时单元控制信号控制主时钟信号的延时时间,生成多个逐级延时时钟信号。

[0045]

在步骤703,利用逐级延时时钟信号对输入信号的边沿进行检测,生成边缘检测信号。

[0046]

本发明实施例中,边沿检测单元利用逐级延时时钟信号检测输入信号,当输入信号有跳变时,输出逻辑电平为

‘1’

的边缘检测信号(edge_detected_x)。

[0047]

在步骤704,从边缘检测信号中检测出最先发生跳变的路径,并将输出路径编号作为测量值的小数部分。

[0048]

本发明实施例中,最先边沿检测单元对接收的多个边缘检测信号,从中检测出最先发生跳变的路径,并将输出路径编号作为测量值的小数部分。

[0049]

在步骤705,将测量值的整数部分与测量值的小数部分结合,获得最终的测量值。

[0050]

实施例3对于多个输入的场景,逐级延时单元及延时时钟(clk_1到clk_n-1)可以复用,即只需要一个逐级延时单元用于多个输入信号的高精度脉宽测量。图8为根据本发明的一个应用实施例场景示意图,如图8所示,当输入为两路输入信号时,系统包括一个逐级延时单元,每一路输入信号分别对应一组边沿检测单元、一个最先边沿检测单元、一个数字定时器及一个fifo及控制单元。适应更多输入信号的结构于此类似,不再赘述。

[0051]

实施例4本发明的实施例还提供一种数字脉宽捕获芯片,包括,上述实施例中的数字脉宽捕获系统。

[0052]

实施例5本发明的实施例还提供一种数字脉宽捕获装置,包括,上述实施例中的数字脉宽捕获芯片。

[0053]

实施例6本发明的实施例还提供一种电子设备,包括处理器,以及存储器,其中,存储器存储有计算机程序,计算机程序在被处理器读取执行时,执行上述数字脉宽捕获方法实施例中的步骤。

[0054]

实施例7本发明的实施例还提供一种计算机可读存储介质,该计算机可读存储介质中存储有计算机程序,其中,该计算机程序被设置为运行时执行上述数字脉宽捕获方法实施例中的步骤。

[0055]

本发明的本发明的数字脉宽捕获系统及方法,该方法利用数字锁相环等技术提供多条可配置的延时单元,这些延时单元分别对主时钟进行不同的延时,随后利用多个延时时钟对同一个输入数字信号进行采样并记录最先采样到跳变沿的通路(作为小数部分),结合主时钟计数(整数部分)得到精确的测量值。假设输入主时钟的周期为t,在采用n条延时单元的情况下,则测量的时间分辨率为可达t/n,即精度增大了n倍,在输入时钟频率不增加的情况下显著提高了数字脉宽捕获精度。

[0056]

本领域普通技术人员可以理解:以上所述仅为本发明的优选实施例而已,并不用于限制本发明,尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例记载的技术方案进行修改,或者对其中部分技术特征进行等同替换。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。