1.本发明涉及半导体技术领域,具体涉及一种基于肖特基二极管的氧化镓微米柱阵列及其制备方法。

背景技术:

2.目前,超宽禁带半导体氧化镓(ga2o3)材料相比于si、gaas等材料具有宽带隙、高电子饱和漂移速度、高热导率、高击穿电场强度、高巴利加优值等优势,是先进电力电子器件的优选材料。近年来,氧化镓肖特基二极管(ga2o

3 sbd)器件性能已经有所提升。2016年,日本flosfia公司制备出耐压为531v、导通电阻仅为0.1mω

·

cm2的氧化镓sbd器件;2017年,日本信息通信研究院机构(nict)采用场板结构,降低峰值电场,制备出耐压1076v的纵向β相的氧化镓sbd器件,其击穿电压为190v,峰值击穿场强达到5.9mv/cm,这远远大于了sic的击穿场强理论值(3.18mv/cm),这证明了氧化镓材料具有高耐压的特点。2018年,康奈尔大学采用凹槽结构,降低了表面电场,实现了2440v垂直结构的β相的氧化镓sbd器件,这是已经报道的垂直结构氧化镓sbd器件的最高水平。然而,目前所研究的异质衬底氧化镓sbd器件其击穿电压和导通特性远远低于材料的预期值。

3.以上所述氧化镓sbd器件存在以下不足之处:1.对于氧化镓材料本身来说,特别是异质衬底的氧化镓,由于其与衬底之间的晶格失配导致的位错密度高达10

10

cm-2

。通常,位错是作为载流子捕获中心和散射中心,形成导电通道泄露的路径,它严重降低了载流子的迁移速率。2.现有的氧化镓sbd器件其界面态对器件漏电影响较大,其开启电压很高,不能满足低的开启电压,快的开关速度和低的能源损耗等需求。

技术实现要素:

4.为了解决现有技术中存在的问题,本发明提供了一种基于肖特基二极管的氧化镓微米柱阵列及其制备方法,将氢化物气相沉积(hvpe)和超声雾化辅助化学气相沉积法(mist cvd)结合,快速制备出ga2o3微米柱阵列,制备高质量的氧化镓阵列材料,以实现低开启电压、快开关速度和低能源损耗的氧化镓微米柱阵列的肖特基二极管。相对于其他氧化镓肖特基二极管的方法,本发明制备的氧化镓微米柱阵列形貌精准可控,重复性好,效率高,制造工艺简单,可以有效地集成和大规模生产。

5.本发明为解决上述技术问题采用以下技术方案:

6.本发明解决技术问题所采用的技术方案如下:

7.一种基于肖特基二极管的氧化镓微米柱阵列,所述肖特基二极管由下往上依次包括衬底层,氧化镓层,氧化镓微米柱的肖特基阵列;所述氧化镓微米柱的肖特基阵列包括氧化镓微米柱、底电极和顶电极,所述底电极和顶电极采用一对多结构;所述氧化镓层为平整的薄膜,所述氧化镓层材料为α相、κ相、γ相或β相氧化镓,所述氧化镓微米柱材料为α相、κ相、γ相或β相氧化镓。

8.进一步的,所述氧化镓微米柱为六棱台结构,底面为六边形,顶部为等边三角形去

掉三个顶角,侧面由三个六边形,三个朝下的五边形和6个朝上的五边形组成;所述氧化镓微米柱孔径大小为1-10μm,高度为50nm-10000nm,微米柱间距为1-20μm。

9.进一步的,所述顶电极为在氧化镓微米柱顶部设置的一个肖特基接触电极,所述底电极为在氧化镓微米柱底部设置的两个欧姆接触电极。

10.进一步的,所述肖特基接触电极为ni/au;所述欧姆接触电极为ti/au或ti/al/ni/au;所述电极厚度为10-500nm。

11.进一步的,所述氧化镓层厚度为50nm-1000nm。。

12.进一步的,所述衬底为绝缘或导电衬底,如氧化镓单晶、蓝宝石、硅、ito导电玻璃衬底等。

13.所述基于肖特基二极管的氧化镓微米柱阵列的制备方法,包括如下步骤:

14.(1)先使用mist cvd在衬底上制备氧化镓层,通过调节mist cvd过程中生长的温度、掺杂浓度以及雾化器的功率,制备得到不同晶向及不同掺杂浓度的氧化镓;

15.(2)再使用pecvd或ald技术,在氧化镓层上生长二氧化硅层;

16.(3)基于集成电路工艺技术,在二氧化硅层上涂抹一定厚度光刻胶,光刻胶上方覆盖掩模版,进行曝光和显影步骤;

17.(4)用euv光刻技术,刻蚀未被保护的区域,制作图形;

18.(5)利用rie、icp等刻蚀技术,将光刻胶上的图形转移至二氧化硅层上,用二氧化硅层作为下一步制备过程的图形掩膜;

19.(6)之后洗去光刻胶,得到二氧化硅掩膜结构,将带有图形的基片放入hvpe腔室中;

20.(7)通过调节hvpe二次外延生长过程中的生长温度、生长时间、氧气和氯化氢的比例和压强,制备得到所需晶向的氧化镓材料;

21.(8)用hf洗去二氧化硅后,得到所需晶向的氧化镓微米柱阵列;

22.(9)将所得氧化镓微米柱结构柱底平面沉积欧姆接触电极;

23.(10)在氧化镓微米柱顶部沉积肖特基接触电极。

24.进一步的,所述步骤(1)中,mist cvd制备生长的高掺杂浓度氧化镓层,氧化镓掺杂浓度为10

18-10

19

cm-3

。

25.进一步的,所述步骤(2)中,二氧化硅层的厚度50nm-500nm。

26.进一步的,所述步骤(7)中,hvpe制备生长的低掺杂浓度氧化镓微米柱阵列,氧化镓掺杂浓度为10

15-10

17

cm-3

。

27.有益效果

28.(1)本发明的氧化镓微米柱相对于常规的氧化镓薄膜,具有更低的位错密度(包括刃位错密度和螺位错密度),有效地提升了氧化镓的晶体质量。

29.(2)本发明的氧化镓微米柱阵列,具有结构简单、功耗低、工艺简单、成本低等优势,特别是可重复性强的优势。相对于传统纳米级别的氧化镓来说,具有精准可控的结构以及重复可行性,便于大规模集成和使用。

30.(3)本发明所属的半导体材料结构,优选不同晶向的氧化镓为原材料,其中β相氧化镓为单斜结构,α相氧化镓为六方结构,κ相氧化镓为正交结构,γ相氧化镓为立方结构,独特的氧化镓结构通过特定的选区生长后会呈现独特的氧化镓结构。

31.(4)本发明的氧化镓微米柱结构的肖特基结构,其核心材料为氧化物,可有效避免空气氧化。

32.(5)本发明的氧化镓微米柱结构的肖特基,其底电极和顶电极采用一对多结构,可独立控制各肖特基的开关特性,降低成本,提高开关效率。

33.(6)本发明采用的技术手段,摒弃了传统的氧化镓薄膜和氧化镓纳米线等材料由于在异质衬底上晶格失配大导致的材料质量问题和无序不可重复的的问题,而是在提高氧化镓晶体质量前提上,将氧化镓不同掺杂浓度以及不同晶向结合,实现了器件的使用范围以及器件的小型化和集成化,工艺简单,调制能力强、设计灵活,可针对不同带隙特性更改设计,便于大规模使用。

附图说明

34.图1为本发明实施例的氧化镓微米柱阵列结构制备步骤实例。

35.图2为本发明实施例的氧化镓微米柱的肖特基结构步骤实例。

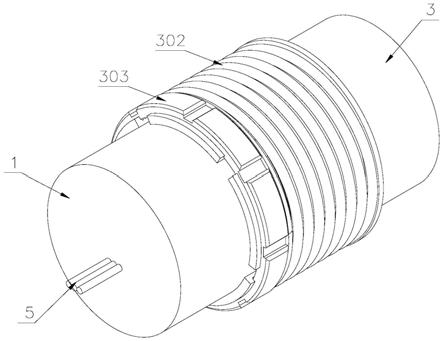

36.图3为本发明实施例的氧化镓微米柱的肖特基结构及一对多电极俯视图。

37.图4为本发明实施例的κ相氧化镓层与α相氧化镓微米柱的结构示意图。

38.图5为本发明实施例的α氧化镓微米柱阵列结构实体图。

具体实施方式

39.下面将结合附图对本发明实施方式作进一步地详细描述。显然,所描述的实施例为α相氧化镓微米柱阵列实施例,该实施例只是本发明的一部分,而不是全部的实施例,其他晶向的氧化镓的微米柱阵列都属于本发明保护范围。所描述的实施例仅用于图示说明,而不是对本发明范围的限制。基于本发明的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明的保护范围。

40.实施例1:基于肖特基二极管的α相氧化镓微米柱阵列

41.如图1-3所示,本实施例为一种基于肖特基二极管的α相氧化镓微米柱阵列,所述肖特基二极管由下往上依次包括衬底层101,氧化镓层102,α相氧化镓微米柱的肖特基阵列301;所述α相氧化镓微米柱的肖特基阵列301包括α相氧化镓微米柱201、底电极203和顶电极204,所述底电极203和顶电极204采用一对多结构,可独立准确控制各肖特基的开关特性。所述氧化镓层102为平整的薄膜。所述α相氧化镓微米柱201为六棱台结构,底面为六边形,顶部为等边三角形去掉三个顶角,侧面由三个六边形,三个朝下的五边形和6个朝上的五边形组成;所述α相氧化镓微米柱201孔径大小为1-10μm,高度为50nm-10000nm,微米柱间距为1-20μm。

42.如图1所示为α相氧化镓微米柱阵列结构制备流程示意图,具体包括以下步骤:

43.(1)先使用超声雾化辅助化学气相沉积法(mist cvd)在蓝宝石衬底101上制备高掺杂浓度的氧化镓层102,通过调节mist cvd过程中生长的温度以及雾化器的功率,制备得到不同晶向的氧化镓;氧化镓掺杂浓度为10

18-10

19

cm-3

,氧化镓层102厚度为50nm-1000nm;

44.(2)再使用pecvd或ald技术,在氧化镓层上生长二氧化硅层103,二氧化硅103的厚度为50nm-500nm;

45.(3)基于集成电路工艺技术,在二氧化硅层上涂抹一定厚度光刻胶,光刻胶上方覆

盖掩模版,进行曝光和显影步骤;

46.(4)用euv光刻技术,刻蚀未被保护的区域,制作图形104,所述图形,但不仅限该图案,圆形、三角形、六边形等;

47.(5)利用rie、icp等刻蚀技术,将光刻胶上的图形104转移至二氧化硅层上,用二氧化硅层103作为下一步制备过程的图形掩膜105;

48.(6)之后洗去光刻胶,得到二氧化硅掩膜结构,将带有图形的基片放入hvpe腔室中;

49.(7)通过调节hvpe二次外延生长过程中的生长温度、生长时间、氧气和氯化氢的比例和压强等条件,制备得到低掺杂浓度的α相的氧化镓材料106;氧化镓掺杂浓度为10

15-10

17

cm-3

;

50.(8)用hf洗去二氧化硅后,得到α相的氧化镓微米柱阵列107。通过氧化镓的选区生长107,有效地降低氧化镓层102中由于氧化镓与衬底101之间晶格失配导致的位错密度(包含刃位错和螺位错),有效地改善氧化镓的晶体质量。

51.如图2所示为基于α相氧化镓微米柱的肖特基结构205的制备流程剖面示意图,

52.(a)将所得α相氧化镓微米柱201的结构柱底平面沉积所述底电极203,即欧姆接触电极(ti/au或ti/al/ni/au);

53.(b)在α相氧化镓微米柱201顶部沉积所述顶电极204,即肖特基接触电极(ni/au)。

54.电极制备工艺使用suss光刻技术、pvd金属沉积技术。所述欧姆接触电极和肖特基接触电极的厚度为10-500nm。

55.实施例2:基于κ相氧化镓层的α相氧化镓微米柱阵列结构403

56.如图4所示,与实施例1的区别在于,氧化镓层102采用κ相氧化镓层402。

57.本发明对其他晶向氧化镓之间的层与微米柱之间的组合不一一列出,但都在保护范围之内。

58.相比于其他肖特基结构来说,高质量的氧化镓,特别是亚稳相氧化镓,经过选区生长后降低两个数量级的位错密度,晶体质量大大提升,使得氧化镓微米柱肖特基的导通电阻很低,功耗更,能够极大地降低器件工作的电能损耗。相对于常规的氧化镓器件制备,本发明的氧化镓微米柱肖特基其氧化镓质量更高,可重复性强,成本低,有利于大规模集成和生产,而对于纳米级别的氧化镓来说,氧化镓微米柱阵列可重复性更高,能够精准控制以及设计所需独特结构的氧化镓结构。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。