1.本发明涉及显示技术领域,且特别是涉及一种具有特殊像素结构配置的显示面板及其制作方法。

背景技术:

2.随着显示科技及面板生产技术的演进,平面型显示面板现今已应用在各种类型的电子产品上。举凡智能手机、平板电脑等,均具有平面型显示面板。为了近一步降低平面型显示面板的电力消耗,相关产业已提出各种解决方案,以符合节能减碳的需求,其中之一为将显示面板的像素结构设计为双栅极像素结构。在双栅极像素结构中,同一条数据线耦接相邻两列的子像素,且在同一个像素行的子像素分别耦接两条相邻的栅极线,如此一来可减去半数数据线,进而达到降低显示面板电力消耗的功效,同时也可达成窄边框以及生产成本降低等效果。

3.然而,在现有的双栅极像素结构中,由于每个像素单元的布局面积不一致,可能造成左右两侧子像素单元中像素晶体管的栅极-源极间电容值(cgs)的不一致,而导致画面显示不良的问题,且容易使显示画面出现垂直细线(v-line)瑕疵。

技术实现要素:

4.本发明的一目的是在于提供一种显示面板,其具有特殊的像素结构配置方式,可解决上述画面显示不良的问题,且同时达到降低电力耗损等效果。本发明的另一目的是在于提供上述显示面板的制作方法。

5.根据上述目的,本发明提出一种显示面板,包含多个像素单元、多条数据线和多条扫描线。多个像素单元排列为多个像素行和多个像素列,且每个像素单元包含多个子像素单元。多条数据线用以传送多个数据信号至多个像素单元,每条数据线具有非直线连续弯曲状或弯折状。多条扫描线用以依序传送多个扫描信号至多个像素单元。每个像素单元中的子像素单元耦接至不同扫描线,且每条数据线以一个像素单元为单位弯曲或弯折。

6.依据本发明的一实施例,多条数据线中的第二条至倒数第二条数据线各自具有多个第一区段和多个第二区段,且在同一条数据线中的第一区段和第二区段分别耦接至相邻的像素列。

7.依据本发明的又一实施例,显示面板还包含多条触控感测线,多条触控感测线用以提供多个触控感测信号,每条触控感测线具有非直线连续弯曲状或弯折状,且每条触控感测线以一个像素单元为单位弯曲或弯折。

8.依据本发明的又一实施例,多条数据线与多条触控感测线属于显示面板中的同一个金属层。

9.依据本发明的又一实施例,多条数据线与多条触控感测线中相邻的数据线与触控感测线相距3微米至5微米。

10.依据本发明的又一实施例,显示面板还包含像素电极层和公共电极层。像素电极

层具有多个像素电极,多个像素电极分别位于像素单元的子像素单元中。公共电极层具有多个公共电极,多个公共电极分别耦接至多条触控感测线。

11.依据本发明的又一实施例,每个公共电极在多条触控感测线中至少一条触控感测线的正上方具有缺口。

12.依据本发明的又一实施例,公共电极层位于像素电极层的上方,且每个公共电极穿过至少一个第一通孔耦接至多条触控感测线中的至少一条触控感测线。

13.依据本发明的又一实施例,像素电极层位于公共电极层的上方,像素电极层还包含多个桥接电极,且每个公共电极通过多个桥接电极中的至少一个桥接电极耦接至多条触控感测线中的至少一条触控感测线。

14.依据本发明的又一实施例,每个像素电极穿过第二通孔耦接至多个子像素单元中的一个子像素单元的像素晶体管。

15.依据本发明的又一实施例,每个公共电极在多条扫描线中至少一条扫描线的正上方具有缺口。

16.根据上述目的,本发明另提出一种制作显示面板的方法,包含在基板上形成第一金属层且在第一金属层的上方形成第二金属层。第一金属层包含多条扫描线。第二金属层包含多条具有非直线连续弯曲状或弯折状的数据线与多条具有非直线连续弯曲状或弯折状的触控感测线。多条扫描线与多条数据线共同定义出多个耦接至不同扫描线的多个子像素单元,且多条数据线及多条触控感测线以三个子像素单元为单位弯曲或弯折。

17.依据本发明的一实施例,制作显示面板的方法还包含在第二金属层上方形成像素电极层且在像素电极层上方形成公共电极层。像素电极层包含多个分别位于多个子像素单元中的像素电极。公共电极层包含多个分别耦接至多条触控感测线的公共电极。

18.依据本发明的又一实施例,制作显示面板的方法还包含在第二金属层上方形成公共电极层且在公共电极层上方形成像素电极层。公共电极层包含多个分别耦接至多条触控感测线的公共电极。像素电极层包含多个分别位于多个子像素单元中的像素电极。

19.依据本发明的又一实施例,制作显示面板的方法还包含图案化公共电极层,以在多条触控感测线的正上方形成公共电极的缺口。

20.本发明的有益效果至少在于,可避免现有显示面板的画面显示不良及出现垂直细线瑕疵等问题,且可同时达到降低电力耗损等效果。

附图说明

21.图1为依据本发明一些实施例的显示装置的示意图;

22.图2为图1的显示面板的主动区中像素单元和触控感测垫的配置示意图;

23.图3a为图1的显示面板的主动区中像素结构的一示例的局部示意图;

24.图3b为图3a所示的像素结构中的一区域的配置示意图;

25.图4为图3a所示的像素结构中的一区域的布局示意图;

26.图5a、图5b分别为图1的显示面板的一示例的结构示意图和剖面图;

27.图6a、图6b分别为图1的显示面板的另一示例的结构示意图和剖面图;

28.图7a、图7b分别为图1的显示面板的又一示例的结构示意图和剖面图。

circuit)。如图1所示,驱动电路120分别通过第一走线w1(1)-w1(m)、第二走线w2(1)-w2(n)和第三走线w3(1)-w3(l)提供数据信号、扫描信号和触控感测信号至位于主动区110a中的数据线、扫描线和触控感测线(图1未绘示)。

36.显示面板110可以是系统整合式玻璃面板(system on glass;sog),也就是说,驱动电路120可以是制作在显示面板110的基板112上。如此一来,便可使用相同工艺来制作驱动电路120中的电子元件和主动区110a中的电子元件(例如像素晶体管、像素电极、触控感测垫tp等,但不限于此)。如图1所示,驱动电路120是制作在基板112上,且在其为触控与显示驱动集成电路的实施例中,其分别通过第一走线w1(1)-w1(m)电性连接主动区110a中的所有数据线,分别通过第二走线w2(1)-w2(n)电性连接主动区110a中的所有扫描线,且分别通过第三走线w3(1)-w3(l)电性连接主动区110a中的所有触控感测垫tp。应注意的是,虽然图1绘示驱动电路120配置在主动区110a的下侧,但本发明并不以此为限。在其他实施例中,驱动电路120也可以是配置在主动区110a的左侧、右侧或上侧,或者分别配置在主动区110a的至少两侧。在一些实施例中,如后续段落的说明,数据线与触控感测线的个数相同,也就是说,第一走线w1(1)-w1(m)的个数与第三走线w3(1)-w3(l)的个数相同,即l等于m。

37.在其他实施例中,驱动电路120可以是位于一个或多个芯片中,且此些芯片可通过玻璃覆晶(chip on glass;cog)、卷带式自动接合(tape automated bonding;tab)、薄膜覆晶(chip on film;cof)等方式与设置在基板112上的接垫(图1未绘示)接合,以提供数据信号、扫描信号和触控感测信号至显示面板110的主动区110a中的电子元件。

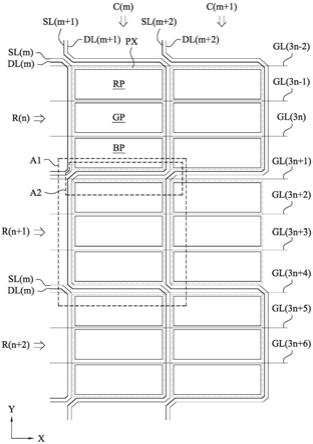

38.图3a为图1的显示面板110的主动区110a中像素结构的一示例的局部示意图。在图3a所示的局部示意图包含位于第n至(n 2)像素行r(n)-r(n 2)及位于第m和(m 1)像素列c(m)-c(m 1)的像素单元px及其周边信号线。在图3a中,数据线dl(m)耦接位于第m像素列c(m)和第n像素行r(n)及位于第m像素列c(m)和第n 2像素行r(n 2)的像素单元px,数据线dl(m 1)耦接位于第(m 1)像素列c(m 1)和第n像素行r(n)、位于第m像素列c(m)和第(n 1)像素行r(n 1)及位于第(m 1)像素列c(m 1)和第(n 2)像素行r(n 2)的像素单元px,而数据线dl(m 2)耦接位于第(m 1)像素列c(m 1)和第n 1像素行r(n 1)的像素单元px。位于第n像素行r(n)的每个像素单元px耦接扫描线gl(3n-2)-gl(3n),其中子像素单元rp、gp、bp分别耦接扫描线gl(3n-2)、gl(3n-1)、gl(3n),且位于第(n 1)像素行r(n 1)和第(n 2)像素行r(n 2)的每个像素单元px与扫描线gl(3n 1)-gl(3n 6)也具有相似的对应关系。数据线dl(m)-dl(m 2)和扫描线gl(3n-2)-gl(3n 6)分别用以提供数据信号和扫描信号至对应的像素单元px。特别地,图3a所示的像素结构为三栅极(tri-gate)像素结构,也就是说,在同一个像素单元px中的所有子像素单元rp、gp、bp均耦接至相同的数据线。举例而言,在第n像素行r(n)和第m像素列c(m)的像素单元px中的所有子像素单元rp、gp、bp均耦接至数据线dl(m)。此外,如图3a所示,数据线dl(m)-dl(m 2)和触控感测线sl(m)-sl(m 2)均以一个像素单元px为单位弯曲或弯折。

39.触控感测线sl(m)-sl(m 2)分别相邻且平行于数据线dl(m)-dl(m 2)。触控感测线sl(m)-sl(m 2)及数据线dl(m)-dl(m 2)均具有非直线的连续弯曲状或弯折状。举例而言,每条触控感测线sl(m)-sl(m 2)和数据线dl(m)-dl(m 2)可由多个前后相互连接的弓字形走线构成。以触控感测线sl(m 1)为例,其与相邻的数据线dl(m 1)大约相距3微米至5微米。

40.图3b为图3a所示的像素结构中的区域a1的配置示意图。如图3b所示,触控感测线

sl(m 1)具有第一至第三区段ss1-ss3,其中第一区段ss1位于第m像素列c(m)的左侧且大致平行y轴,第二区段ss2位于第m像素列c(m)的右侧且大致平行y轴,而第三区段ss3位于在第m像素列c(m)与第(n 1)像素行r(n 1)中的像素单元px与在第m像素列c(m)与第(n 2)像素行r(n 2)中的像素单元px之间且大致平行x轴,且x轴与y轴互为垂直。触控感测线sl(m 1)在上下相邻的像素单元px之间弯曲或弯折。由于x轴与y轴互为垂直,所以触控感测线sl(m 1)的弯曲或弯折的角度可大约为90度。同样地,与触控感测线sl(m 1)相邻的数据线dl(m 1)也具有第一至第三区段ds1-ds3,其中第一区段ds1位于第m像素列c(m)的左侧且大致平行y轴,第二区段ds2位于第m像素列c(m)的右侧且大致平行y轴,而第三区段ds3位于在第m像素列c(m)与第(n 1)像素行r(n 1)中的像素单元px与在第m像素列c(m)与第(n 2)像素行r(n 2)中的像素单元px之间且大致平行x轴。另外,如图3b所示,数据线dl(m 1)的第一区段ds1耦接位于第m像素列c(m)与第(n 1)像素行r(n 1)的像素单元px中每个子像素单元rp、gp、bp的像素晶体管tft。虽然图3b未直接显示,但本领域技术人员可由图3a、图3b绘示的内容直接理解,数据线dl(m 1)的第二区段ds2耦接位于第(m 1)像素列c(m 1)与第(n 2)像素行r(n 2)的像素单元px中每一子像素单元rp、gp、bp的像素晶体管tft。

41.应注意的是,虽然图3b仅绘示触控感测线sl(m 1)的局部配置,但本领域技术人员应可由图3b绘示的内容直接得知,触控感测线sl(m 1)和数据线dl(m 1)在第m像素列c(m)中任意两个上下相邻的像素单元px之间弯曲或弯折。此外,位于主动区110a中的其他触控感测线和数据线也可具有类似的配置方式。

42.另外,虽然图3a仅绘示部分的像素列和像素行,但仍可由图3a所示的内容直接推得,主动区110a中像素阵列的列数为(m-1)列,即为数据线dl(1)-dl(m)或触控感测线sl(1)-sl(m)的个数m减去1。此外,由于每个像素晶体管配置在其对应的子像素单元的左侧,所以第2至m条数据线dl(2)-dl(m)中的每一个和第2至m条触控感测线sl(2)-sl(m)中的每一个均具有非直线的连续弯曲状或弯折状,但第1条数据线dl(1)和第1条触控感测线sl(1)可以是直线而不具有非直线的连续弯曲状或弯折状。在其他实施例中,每个像素晶体管配置在其对应的子像素单元的右侧,且相应地第1至(m-1)条数据线dl(1)-dl(m-1)和第1至(m-1)条触控感测线sl(1)-sl(m-1)均具有非直线的连续弯曲状或弯折状,但第m条数据线dl(m)和第m条触控感测线sl(m)可以是直线而不具有非直线的连续弯曲状或弯折状。此外,在一些实施例中,数据线dl(1)-dl(m)与触控感测线sl(1)-sl(m)可属于基板112上的同一个金属层。

43.图4为图3a所示的像素结构中区域a2的布局示意图,其中细点填满部分为像素电极pe,而灰色填满部分为公共电极ce。图4所示的布局示意图为上公共电极(top com)像素结构,其中公共电极ce位于像素电极pe的上方。虽然图4仅绘示出上下相邻子像素单元的部分及邻近的数据线、扫描线和触控感测线的布局,而本领域技术人员可由图4所示的内容直接推知,主动区110a中的其他区域也可具有相似的布局。

44.如图4所示,公共电极ce在触控感测线sl(m 1)的正上方具有缺口。除了连接点cp以外,触控感测线sl(m 1)未被公共电极ce覆盖,以降低公共电极ce与触控感测线sl(m 1)之间的电容值。如图4所示,触控感测线sl(m 1)的第一至第三区段ss1-ss3均未被公共电极ce覆盖。此外,扫描线gl(3n 1)的大部分区段也未被公共电极ce覆盖,以降低公共电极ce与扫描线gl(3n 1)之间的电容值。连接点cp可配置在子像素单元的角落(例如图4所示的连接

点cp位于子像素单元的右下角),以增加子像素单元的开口率。连接点cp连接触控感测线sl(m 1)和公共电极ce,使触控感测线sl(m 1)电性连接公共电极ce。依据不同实施例,连接点cp可包含直孔(direct via)结构或是桥接结构。

45.图5a、图5b分别为图1的显示面板110的一示例的结构示意图和剖面图。在本示例中,第一金属层204位于基板202上,其可包含栅极204a和扫描线(图5b未绘示)。基板202对应图1的基板112,其可以是玻璃基板、陶瓷基板或其他合适材料的基板。栅极绝缘层206位于基板202和第一金属层204上,其覆盖基板202和第一金属层204。半导体层结构208位于栅极绝缘层206上,其包含半导体层208a以及在半导体层208a上的掺杂半导体层208b。半导体层208a的材料可以是非晶硅、单晶硅(monocrystalline silicon)、多晶硅或其他类似材料,且掺杂半导体层208b的材料可以对应是掺杂(doped)非晶硅、掺杂单晶硅、掺杂多晶硅或其他类似材料。此外,半导体层208a和掺杂半导体层208b可通过化学气相沉积法或其他类似沉积方式依序形成。

46.第二金属层210位于栅极绝缘层206和半导体层结构208上,其包含源极210a、漏极210b、数据线(图5b未绘示)和触控感测线210c。源极210a、漏极210b、栅极204a、半导体层结构208和一部分的栅极绝缘层206共同构成像素晶体管tft。在一些实施例中,源极210a的部分属于所对应的数据线的其中一个区段。形成第一金属层204和第二金属层210所使用的材料可包括铬、钨、钽、钛、钼、铝、铜等金属元素或其他类似元素,或是包括上述金属元素的任意组合所形成的合金或化合物等,但不限于此。

47.像素电极层212位于栅极绝缘层206和第二金属层210上,其直接接触漏极210b。保护层214位于半导体层结构208、第二金属层210和像素电极层212上,且覆盖像素晶体管tft和像素电极层212,以对像素晶体管tft和像素电极层212提供保护及绝缘等效果。公共电极层216位于第二金属层210和保护层214上,其可覆盖保护层214,且穿过通孔v1耦接触控感测线210c。

48.形成像素电极层212和公共电极层216的材料可以是例如氧化铟锡(indium tin oxide;ito)和氧化铟锌(indium zinc oxide;izo)等透明导电材料,但不限于此,且像素电极层212和公共电极层216可通过物理气相沉积法或其他类似沉积方式形成。保护层214的材料可以是氮化硅、氮化硅、氮氧化硅或其他类似材料,且其可通过化学气相沉积法或其他类似沉积方式形成。

49.图6a、图6b分别为图1的显示面板110的另一示例的结构示意图和剖面图。在本示例中,第一金属层304位于基板302上,其可包含栅极304a和扫描线(图6b未绘示)。栅极绝缘层306位于基板302和第一金属层304上,其覆盖基板302和第一金属层304。半导体层结构308位于栅极绝缘层306上,其包含半导体层308a以及在半导体层308a上的掺杂半导体层308b。第二金属层310位于栅极绝缘层306和半导体层结构308上,其包含源极310a、漏极310b、数据线(图6b未绘示)和触控感测线310c。基板302、第一金属层304、栅极绝缘层306、半导体层结构308和第二金属层310可分别与图5a、图5b中的基板202、第一金属层204、栅极绝缘层206、半导体层结构208和第二金属层210相同或相似,所以相关说明请参照有关图5a、图5b的说明,在此不赘述。

50.第一保护层312和覆盖层314依序位于栅极绝缘层306、半导体层结构308和第二金属层310上,且覆盖像素晶体管tft。第一保护层312可对像素晶体管tft提供保护及绝缘等

效果,而覆盖层314可用于调整显示面板的电性,降低上方公共电极对下方触控感测线和扫描线的负载,进而提升显示面板的触控感测表现。在其他实施例中,可仅具有第一保护层312但不具有覆盖层314。像素电极层316位于第二金属层310、第一保护层312和覆盖层314上,其直接接触漏极310b。第二保护层318位于第一保护层312、覆盖层314和像素电极层316上,且覆盖像素电极层316,以对像素电极层316提供保护及绝缘等效果。公共电极层320位于第二金属层310、第一保护层312和第二保护层318上,其穿过通孔v2耦接触控感测线310c。

51.形成第一保护层312和第二保护层318的材料可以是氮化硅、氮化硅、氮氧化硅或其他类似材料,且其可通过化学气相沉积法或其他类似沉积方式形成。形成覆盖层314的材料可以是有机介电材料,例如环氧树脂、丙烯酸树脂、聚酰亚胺(polyimide;pi)或其他合适材料,或是无机介电材料,例如氧化硅、氮化硅或其他合适材料。此外,形成像素电极层316和公共电极层320的材料可以是例如氧化铟锡和氧化铟锌等透明导电材料,但不限于此,且像素电极层316和公共电极层320可通过物理气相沉积法或其他类似沉积方式形成。

52.图7a、图7b分别为图1的显示面板110的又一示例的结构示意图和剖面图。在本示例中,第一金属层404位于基板402上,其可包含栅极404a和扫描线(图7b未绘示)。栅极绝缘层406位于基板402和第一金属层404上,其覆盖基板402和第一金属层404。半导体层结构408位于栅极绝缘层406上,其包含半导体层408a以及在半导体层408a上的掺杂半导体层408b。第二金属层410位于栅极绝缘层406和半导体层结构408上,其包含源极410a、漏极410b、数据线(图7b未绘示)和触控感测线410c。基板402、第一金属层404、栅极绝缘层406、半导体层结构408和第二金属层410可分别与图5a、图5b中的基板202、第一金属层204、栅极绝缘层206、半导体层结构208和第二金属层210相同或相似,所以相关说明请参照有关图5a、图5b的说明,在此不赘述。

53.第一保护层412和覆盖层414依序位于栅极绝缘层406、半导体层结构408和第二金属层410上,且覆盖像素晶体管tft。第一保护层412可对像素晶体管tft提供保护及绝缘等效果,而覆盖层414可用于调整显示面板的电性。第一保护层412和覆盖层414可分别与图6a、图6b中的第一保护层312和覆盖层314相同或相似,所以相关说明请参照有关图6a、图6b的说明,在此不赘述。

54.公共电极层416位于覆盖层414上,且第二保护层418位于第一保护层412、覆盖层414和公共电极层416上。像素电极层420位于第二金属层410、第一保护层412、公共电极层416和第二保护层418上,其包含桥接结构420a和像素电极420b,其中桥接结构420a穿过通孔v3、v4分别耦接触控感测线410c和公共电极层416,使触控感测线410c电性连接公共电极层416,而像素电极420b穿过通孔v5耦接漏极410b。

55.相较于图5a、图5b和图6a、图6b所示的上公共电极像素结构,图7a、图7b所示的像素结构为上像素电极(top-pixel)像素结构。也就是说,在图7a、图7b所示的像素结构中,像素电极层420位于公共电极层416的上方。此外,形成公共电极层416、第二保护层418和像素电极层420的材料和工艺可分别与形成图6a、图6b的公共电极层320、第二保护层318和像素电极层316相似。

56.综上所述,本发明可使每个像素单元的布局面积一致,使每个像素晶体管的栅极-源极间电容值大致相同,避免现有显示面板的画面显示不良及出现垂直细线瑕疵等问题,

且可同时达到降低电力耗损等效果。

57.虽然本发明已经以实施例公开如上,然其并非用以限定本发明,任何本领域技术人员,在不脱离本发明的精神和范围内,当可作些许变动与润饰,所以本发明的保护范围当视权利要求所界定者为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。