1.根据本发明的实施方案的一个或多个方面涉及一种光电子器件,并且更具体地涉及一种包括绝缘体上硅晶片的光电子器件。

背景技术:

2.已知硅波导中的光的光学调制,包括基于以下项的波导调制器:电光、量子限制斯塔克、franz-keldysh和载流子等离子体色散。

3.波导调制器可包括硅、iii-v型材料、其他半导体和聚合物波导。它们典型地是对称结构,但掺杂区可能不对称。例如,us 7,085,443提出了一种pn相移调制器,其中硅的掺杂在波导上是不对称的。

4.决定硅pn结移相器调制效率的主要因素是光模与pn结区域之间的重叠程度。具体地,可通过增加光模与pn结区域之间的重叠来提高硅移相器的调制效率。

技术实现要素:

5.本发明旨在提高光电子器件的调制效率。具体地,根据第一方面,本发明的实施方案提供了一种光电子器件,所述光电子器件包括:

6.光波导,所述光波导形成在绝缘体上硅晶片的硅器件层中,所述光波导包括半导体结,所述半导体结包括:

7.半导体材料的第一掺杂区;以及

8.半导体材料的第二掺杂区,所述第二掺杂区包含与所述第一掺杂区不同种类的掺杂剂,其中:

9.所述第一掺杂区的第一部分在所述第二掺杂区的顶部上水平地延伸;

10.所述第一掺杂区的第二部分沿着所述第二掺杂区的横向侧竖直地延伸;并且

11.所述第一掺杂区的第三部分作为突出部从所述第一掺杂区的所述第一部分或所述第二部分突出到所述第二掺杂区中。

12.绝缘体上硅soi晶片包括硅衬底、在硅衬底的顶部上的掩埋氧化物(box)层,以及在box层的顶部上的硅器件层(即,顶部硅层)。如本文所使用,术语“竖直地”和“水平地”应理解为相对于box层而言,使得“竖直地”是垂直于box层的上表面,并且“水平地”涉及位于与沿着box层的上表面的平面平行的任何平面内的方向。

13.根据该方面,第一掺杂区和第二掺杂区之间的半导体结在波导的光模区域中具有增加的长度,使得光模和结之间的重叠增加。因此,提高了光电子器件的调制效率。

14.现在将阐述本发明的可选特征。这些可单独地或与本发明的任何方面以任何组合应用。

15.应理解,突出部可能是从其周围向外/向内或向上/向下突出的某物。因此,通过作为突出部从第一掺杂区的第一部分或第二部分突出到第二掺杂区中,第一掺杂区的第三部分可在除了第一掺杂区的第三部分的一侧之外的所有侧被第二掺杂区包围(即,在除了它

从第一掺杂区的第一/第二部分延伸的那侧之外的所有侧被第二掺杂区包围)。具体地,第一掺杂区的第三部分的相对侧可与第二掺杂区邻接。因此,第一掺杂区的第三部分可形成延伸到第二掺杂区中的突出部/半岛。

16.具体地,第一掺杂区的第一部分可在其相应的端部之间延伸,第一掺杂区的第二部分可在其相应的端部之间延伸,并且第一掺杂区的第三部分可从第一掺杂区的第一部分或第二部分的端部之间的点突出。换句话说,第三部分不从第一掺杂区的第一或第二部分的端部延伸。

17.以此方式,第一掺杂区的第一部分、第二部分和第三部分共同可类似于英文字母“f”。

18.第一掺杂区可具有与第二掺杂区相反的掺杂类型。例如,第一掺杂区可以是p型掺杂区并且第二掺杂区可以是n型掺杂区,反之亦然。因此,第一掺杂区和第二掺杂区之间的半导体结可以是p-n结。

19.任选地,第一掺杂区的第一部分可在第二掺杂区的整个上表面的顶部上水平地延伸。

20.第一掺杂区的第二部分可在第一掺杂区的第一部分的端部与box层之间竖直地延伸。

21.任选地,光电子器件可包括具有脊区和两个横向延伸的平板区的脊形波导。

22.在一些实施方案中,第一掺杂区的第三部分可从第一掺杂区的第二部分水平地突出到第二掺杂区中。第一掺杂区的第三部分可具有半圆柱形几何形状(当在横截面中观察时为半圆形),其中第三部分的平坦表面邻近第二掺杂区,并且第三部分的弯曲表面邻近第二掺杂区。

23.以此方式,第二掺杂区在第一掺杂区的第三部分的顶部上和下方延伸。第二掺杂区还沿着第一掺杂区的第三部分的横向侧竖直地延伸。

24.在这些实施方案中,第一掺杂区的第三部分可从第一掺杂区的第二部分的中点(即,从第一掺杂区的第二部分的两个端部之间的中间点)突出到第二掺杂区中。

25.任选地,第一掺杂区的长度(即,其两个端部之间的距离)可大于第一掺杂区的第三部分水平地突出到第二掺杂区中的距离。

26.在可选的实施方案中,第一掺杂区的第三部分可从第一掺杂区的第一部分竖直地突出到第二掺杂区中。在这些实施方案中,第一掺杂区的第三部分从光波导的上表面朝向soi晶片的box层竖直地向下突出。

27.以此方式,第二掺杂区在第一掺杂区的第三部分的任一横向侧上竖直地延伸。第二掺杂区还在第一掺杂区的第三部分下方延伸。

28.在这些实施方案中,第一掺杂区的第三部分可从第一掺杂区的第一部分的中点(即,从第一掺杂区的第一部分的两个端部之间的中间点)突出到第二掺杂区中。

29.任选地,第二掺杂区的长度(即,其两个端部之间的距离)可大于第一掺杂区的第三部分竖直向下突出到第二掺杂区中的距离。

30.在一些实施方案中,光电子器件还可包括第一重掺杂区(例如,n 、p )。第一重掺杂区可在光波导的光传播区之外形成。光波导的光传播区是光被限制为传播的空间区域,并且位于光电子器件的脊区中。第一重掺杂区可在光电子器件的平板区中形成。

31.类似地,光电子器件还可包括第二重掺杂区(例如,n 、p )。第二重掺杂区可在光波导的光传播区之外形成。第二重掺杂区可在光电子器件的平板区中形成。第二重掺杂区可包含与第一重掺杂区不同种类的掺杂剂。

32.第一重掺杂区可包含与第一掺杂区相同种类的掺杂剂,但可具有比第一掺杂区更高浓度的掺杂剂(即,比第一掺杂区更重地掺杂)。第二重掺杂区可包含与第二掺杂区相同种类的掺杂剂,但可具有比第二掺杂区更高浓度的掺杂剂(即,比第二掺杂区更重地掺杂)。

33.第一掺杂区的延伸部可从光波导的光传播区(即,从第一掺杂区的第二部分)延伸到光传播区之外的第一重掺杂区。第二掺杂区的延伸部可从光波导的光传播区延伸到平板区中的第二重掺杂区。

34.具体地,第一掺杂区的延伸部可从光波导的光传播区水平地延伸到第一重掺杂区。类似地,第二掺杂区的延伸部可从光波导的光传播区水平地延伸到第二重掺杂区。第一掺杂区和第二掺杂区的相应延伸部可在soi晶片的box层的顶部上并与其邻接地水平延伸。

35.任选地,光电子器件还可包括电连接到第一重掺杂区的第一电触点和电连接到第二重掺杂区的第二电触点。例如,第一电触点和第二电触点可包括铝。

36.在一些实施方案中,光电子器件还可包括在光波导的顶部上的钝化层。在这些实施方案中,第一电触点和第二电触点可延伸穿过钝化层以分别电接触第一重掺杂区域和第二重掺杂区。例如,钝化层可包括二氧化硅。

37.还公开了制造第一方面的光电器件的方法。具体地,根据第二方面,提供了一种制造光电子器件的方法,所述光电子器件具有形成在绝缘体上硅晶片的硅器件层中的光波导,所述制造的光电子器件的所述光波导包括在以下项之间的结:

38.半导体材料的第一掺杂区;以及

39.半导体材料的第二掺杂区,所述第二掺杂区包含与所述第一掺杂区不同种类的掺杂剂,其中所述方法包括以下步骤:

40.形成所述第一掺杂区的第一部分,所述第一掺杂区的所述第一部分在所述第二掺杂区的顶部上水平地延伸;

41.形成所述第一掺杂区的第二部分,所述第一掺杂区的所述第二部分沿着所述第二掺杂区的横向侧竖直地延伸;并且

42.形成所述第一掺杂区的第三部分,其中在所述制造的光电子器件中,所述第一掺杂区的所述第三部分作为突出部从所述第一掺杂区的所述第一部分或所述第二部分突出到所述第二掺杂区中。

43.类似于第一方面,绝缘体上硅soi晶片包括硅衬底(即,硅基层)、在硅衬底的顶部上的掩埋氧化物(box)层,以及在box层的顶部上的硅器件层(即,顶部硅层)。如本文所使用,术语“竖直地”和“水平地”应理解为相对于box层而言,使得“竖直地”是垂直于box层的上表面,并且“水平地”涉及位于与沿着box层的上表面的平面平行的任何平面内的方向。

44.如上所述,突出部可能是从其周围向外/向内或向上/向下突出的某物。因此,通过作为突出部从第一掺杂区的第一部分或第二部分突出到第二掺杂区中,第一掺杂区的第三部分可在除了第一掺杂区的第三部分的一侧之外的所有侧被第二掺杂区包围(即,在除了它从第一掺杂区的第一/第二部分延伸的那侧之外的所有侧被第二掺杂区包围)。具体地,第一掺杂区的第三部分的相对侧可与第二掺杂区邻接。因此,第一掺杂区的第三部分可形

成延伸到第二掺杂区中的突出部/半岛。

45.具体地,第一掺杂区的第一部分可在其相应的端部之间延伸,第一掺杂区的第二部分可在其相应的端部之间延伸,并且第一掺杂区的第三部分可从第一掺杂区的第一部分或第二部分的端部之间的点突出。换句话说,第三部分不从第一掺杂区的第一或第二部分的端部延伸。

46.以此方式,可形成第一掺杂区的第一部分、第二部分和第三部分以便类似于英文字母“f”。

47.下面阐述了其他任选的特征。

48.类似于第一方面,第一掺杂区可具有与第二掺杂区相反的掺杂类型。例如,第一掺杂区可以是p型掺杂区并且第二掺杂区可以是n型掺杂区,反之亦然。因此,第一掺杂区和第二掺杂区之间的半导体结可以是p-n结。

49.任选地,形成所述第一掺杂区的第三部分的所述步骤包括:

50.将第一掩模层沉积在所述硅器件层上;

51.在所述第一掩模层中形成通到所述硅器件层的开口;以及

52.穿过所述第一掩模层中的所述开口将第一掺杂剂引入到所述硅器件层。

53.因此,第一掩模层中的开口提供了图案以将第一掺杂剂引入到硅器件层。

54.可通过第一掺杂剂的扩散或通过第一掺杂剂的注入(这可取决于soi晶片的硅器件层的厚度)将第一掺杂剂引入到硅器件层以形成第一掺杂层的第三部分。

55.第一掺杂区可以是p型掺杂。在这些实施方案中,第一掺杂剂可以是硼。以此方式,可通过硼扩散或硼注入来形成第一掺杂区的第三部分。

56.在可选的实施方案中,第一掺杂区可以是n型掺杂。在这些实施方案中,例如,第一掺杂剂可以是磷。

57.例如,第一掩模层可包括二氧化硅。例如,第一掩模层的厚度可以是大约500nm。

58.任选地,可在单个工艺步骤中执行形成第一掺杂区的第一部分和第二部分的步骤。例如,形成第一掺杂区的第一部分和第二部分的步骤可包括:

59.将第二掩模层沉积在所述光波导上;以及

60.穿过所述第二掩模层将所述第一掺杂剂引入到所述光波导。

61.可通过注入引入第一掺杂剂。具体地,为了形成第一掺杂区的第一部分和第二部分,可通过从水平线以小于90

°

的角度注入来引入第一掺杂剂(其中如上所述,水平线是位于与沿着box层的上表面的平面平行的任何平面内的方向)。在一些实施方案中,可通过相对于水平线以45

°

的角度注入来引入第一掺杂剂。

62.通过相对于水平线以小于90

°

注入,可在单个工艺步骤中在光波导中形成第一掺杂区的第一部分和第二部分,其中第一掺杂区的第一部分在第二掺杂区的顶部上水平地延伸,并且第一掺杂区的第二部分沿着第二掺杂区的横向侧竖直地延伸。

63.任选地,例如,第二掩模层可包括二氧化硅。例如,第一掩模层的厚度可以是大约20nm至50nm。

64.所述方法还可包括:

65.将波导掩模层沉积在所述soi晶片的所述硅器件层;以及

66.蚀刻所述soi晶片的所述硅器件层的一部分以形成所述光波导。

67.例如,波导掩模层可以是氮化硅或二氧化硅,并且可具有大约500nm的厚度。波导掩模层可提供图案以用于蚀刻硅器件层的一部分来形成光波导。

68.蚀刻硅器件层的一部分来形成光波导的步骤可在通过将第一掺杂剂引入到硅器件层来形成第一掺杂区的第三部分的步骤之后执行。在这些实施方案中,蚀刻硅器件层,使得得到的光波导包括第一掺杂区的第三部分,第一掺杂区的第三部分从光波导的上表面(即,脊区的上表面)竖直地向下突出。

69.可选地,蚀刻硅器件层的一部分来形成光波导的步骤可作为两阶段工艺来执行。具体地,在第一阶段,可蚀刻部分硅器件层的一部分以形成部分形成的光波导。部分形成的光波导可被蚀刻到小于光波导的最终深度的部分深度。

70.在这些实施方案中,然后可通过以下操作来执行形成第一掺杂区的第三部分的步骤:

71.将所述第一掩模层沉积在所述部分形成的光波导上;

72.在所述第一掩模层中形成通到所述部分形成的光波导的开口;以及

73.穿过所述第一掩模层中的所述开口将第一掺杂剂引入到所述部分形成的波导。

74.在将第一掺杂剂引入到部分形成的光波导之后,可执行第二蚀刻阶段以将光波导形成至其全深度。具体地,在该第二阶段,进一步蚀刻硅器件层的被蚀刻部分,使得从部分形成的光波导形成光波导。从部分形成的光波导的第一深度,将光波导蚀刻至其全深度。

75.以此方式,第一掺杂区的第三部分可从光波导的横向侧从不在光波导的脊部分的横向侧的相对端部的点水平地突出。这将导致第一掺杂区的共同的第一部分、第二部分和第三部分的“f”形状。

76.第二掺杂区可由soi晶片的硅器件层提供。因此,soi晶片的硅器件层可包含与第一掺杂区不同种类的掺杂剂。硅器件层可具有与第一掺杂区相反的掺杂类型。例如,在引入第一掺杂剂以形成第一掺杂区之前,硅器件层可以是p型或n型掺杂。

77.例如,soi晶片可以是3μm晶片。

78.任选地,所述方法还可包括:

79.在所述光波导的光传播区之外形成第一重掺杂区,所述第一重掺杂区包含与所述第一掺杂区相同种类的掺杂剂;以及

80.在所述光波导的所述光传播区之外形成第二重掺杂区,所述第二重掺杂区包含与所述第二掺杂区相同种类的掺杂剂。

81.在这些实施方案中,第一重掺杂区比第一掺杂区更重地掺杂(即,具有更高浓度的掺杂剂),并且第二重掺杂区比第二掺杂区更重地掺杂。例如,如果第一掺杂区是p型掺杂,则第一重掺杂区可以是p 掺杂,并且如果第二掺杂区是n型掺杂,则第二重掺杂区可以是n 掺杂。

82.任选地,形成第一重掺杂区的步骤可包括将第一掺杂剂引入到在光波导的光传播区之外的soi晶片的硅器件层的区。具体地,可将第一掺杂剂引入到光电子器件的平板区。可通过注入第一掺杂剂来引入第一掺杂剂。如上所讨论,第一掺杂剂可以是硼或磷。

83.形成第二重掺杂区的步骤包括将第二掺杂剂引入到在光波导的光传播区之外的soi晶片的硅器件层的区,第二掺杂剂与第一掺杂剂不同并且任选地具有相反的掺杂类型。具体地,可将第二掺杂剂引入到光电子器件的平板区。可通过注入第二掺杂剂来引入第二

掺杂剂。

84.例如,第二掺杂剂可以是磷或硼。在第一掺杂剂是硼的实施方案中,第二掺杂剂可以是磷。

85.所述方法还可包括对光波导进行退火。例如,可在1050℃至1100℃下将光波导退火10秒。

86.任选地,所述方法还可包括:

87.将钝化层沉积在所述光波导上;

88.穿过所述钝化层将第一电触点施加到所述第一重掺杂区;以及

89.穿过所述钝化层将第二电触点施加到所述第二重掺杂区。

90.例如,钝化层可包括二氧化硅。钝化层的厚度可以是500nm。例如,第一电触点和第二电触点可包括铝。

91.根据第三方面,提供了一种制造光电子波导的方法,所述光电子波导形成在绝缘体上硅晶片的硅器件层中,所述硅器件层提供半导体材料的第二掺杂区,其中所述方法包括以下步骤:

92.将所述绝缘体上硅晶片的所述硅器件层的一部分蚀刻至小于所述光波导的最终深度的第一深度,以形成部分形成的光波导;

93.在所述部分形成的光波导中形成第一掺杂区的第三部分,所述第一掺杂区包含与所述第一掺杂区不同种类的掺杂剂;

94.进一步蚀刻所述部分形成的光波导来以其全深度形成的所述光波导;

95.在所述光波导中形成所述第一掺杂区的第一部分,所述第一掺杂区的所述第一部分在所述第二掺杂区的顶部上水平地延伸;以及

96.在所述光波导中形成所述第一掺杂区的第二部分,所述第一掺杂区的所述第二部分沿着所述第二掺杂区的横向侧竖直地延伸,其中所述第一掺杂区的所述第三部分作为突出部从所述第一掺杂区的所述第一部分或所述第二部分突出到所述第二掺杂区中。

97.根据第四方面,提供了一种制造光电子波导的方法,所述光电子波导形成在绝缘体上硅晶片的硅器件层中,所述硅器件层提供半导体材料的第二掺杂区,所述方法包括以下步骤:

98.在所述硅器件层中形成第一掺杂区的第三部分,所述第一掺杂区包含与所述第一掺杂区不同种类的掺杂剂;

99.蚀刻所述硅器件层的一部分以形成所述光波导;

100.在所述光波导中形成所述第一掺杂区的第一部分,所述第一掺杂区的所述第一部分在所述第二掺杂区的顶部上水平地延伸;

101.在所述光波导中形成所述第一掺杂区的第二部分,所述第一掺杂区的所述第二部分沿着所述第二掺杂区的横向侧竖直地延伸,其中所述第一掺杂区的所述第三部分作为突出部从所述第一掺杂区的所述第一部分或所述第二部分突出到所述第二掺杂区中。

102.根据第五方面,提供了一种制造第一方面的光电子器件的方法。

103.根据第六方面,提供了一种可用作电光调制器的马赫-曾德尔干涉仪,所述干涉仪包括一对波导,每个波导包含根据第一方面所述的光电子器件。

104.本公开包括上述方面和任选特征的组合,除非这种组合是明显不允许的或明确避

免的。

附图说明

105.现在将参考附图通过示例的方式来描述本发明的实施方案,在附图中:

106.图1a至图1r描绘了根据本发明的第一实施方案的制造光电子器件的方法的步骤;

107.图2是根据图1a至图1r所描绘的方法制造的光电子器件的示意横截面;

108.图3a至图3f描绘了根据本发明的第二实施方案的制造光电子器件的方法的步骤;

109.图4是根据图3a至图3f所描绘的方法制造的光电子器件的示意横截面;并且

110.图5a和图5b示出了图2或图4的光电子器件的可能应用。

具体实施方式

111.下面结合附图阐明的详细描述意图作为根据本发明提供的光电子器件及其制造方法的示例性实施方案的描述,而不意图表示其中可构建或利用本发明的唯一形式。

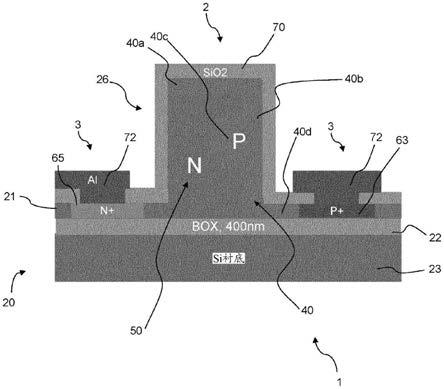

112.下面参考图1a至图1r描述根据第一实施方案的制造光电子器件的方法。在图2中示出所得制造的器件。所制造的光电子器件1包括具有脊区2和两个横向延伸的平板区3的脊形波导。光电子器件1包括soi晶片20。

113.如图1a所示,最初提供soi晶片20,所述晶片包括硅衬底23(即,硅基层)、掩埋氧化物(box)层22和硅器件层21(即,硅器件层)。soi晶片20是3μm晶片,并且box层22具有400nm的厚度,如从衬底23的上表面到box层22的上表面测量到。硅器件层21是n型掺杂的,并且将形成光电子器件1的p-n结的第二掺杂区。可选地,可提供未掺杂的硅器件层21,然后将该未掺杂的硅器件层掺杂n种掺杂剂。

114.在图1b中,将波导掩模25沉积在硅器件层21上。波导掩模25包括氮化硅、优选地si3n4,并且具有500nm的厚度。将波导掩模25图案化以限定光波导。具体地,沉积波导掩模25,并且使用光刻工艺将掩模图案化以限定光波导。使用标准沉积技术。

115.接下来,如图1c所示,执行两阶段蚀刻工艺的第一阶段。具体地,在硅器件层21中蚀刻部分形成的光波导16。在蚀刻部分形成的光波导16之前的硅器件层21的高度在图1c中被指示为h。在硅器件层21中将部分形成的光波导16蚀刻至深度h。深度h在0.5h至0.25d的范围内,其中d是如由掩模25限定的部分形成的光波导16的宽度。可使用标准图案化和蚀刻技术来蚀刻部分形成的光波导16。

116.在图1d中,将第一掩模层27沉积在部分形成的光波导16和soi晶片20的硅器件层21上。第一掩模层27包括二氧化硅并且具有大约500nm的厚度。

117.接下来,将光刻胶28置于第一掩模层27上(图1e)并进行图案化以在第一掩模层27中限定开口。光刻胶28具有贯穿其的窗口29,使得第一掩模层27的一部分被暴露。窗口29置于硅器件层21的具有减小的高度的一部分(即,硅器件层21的已经被蚀刻掉的一部分)上。以此方式,窗口29置于平板区3(硅器件层21的在光传播区之外的区)上。

118.在图1f中,在第一掩模层27中形成通到部分形成的光波导16的开口30。通过hf湿法蚀刻(即,使用氢氟酸的湿法蚀刻)形成第一掩模层27中的开口30。开口30延伸到部分形成的光波导16的横向侧31,因为湿法蚀刻有意过度蚀刻第一掩模层27。然后移除光刻胶28。

119.如图1g所示,第一掺杂剂(例如,硼)通过扩散穿过第一掩模层27中的开口30而被

引入到部分形成的光波导16,从而形成上述第一掺杂区40的第三部分40c。第一掺杂区40是p型掺杂。第一掺杂区40的第三部分40c水平地突出到由硅器件层21形成的第二掺杂区50中。第一掺杂区40的第三部分40c从光波导26的横向侧31突出大约0.5d(即,光波导16的宽度的一半)的距离。如图1g所示,一些第一掺杂剂还将向下朝向box层22扩散。该掺杂剂扩散区将向下延伸大约0.5d的距离。

120.在可选的实施方案中,不是通过扩散引入第一掺杂剂,而是可通过注入引入第一掺杂剂。

121.在图1h中,将第一掩模层27移除,但是波导掩模25保持在光波导16上。

122.接下来,执行第二蚀刻阶段,而不使用波导掩模25(图1i)。使用标准蚀刻技术将光波导26蚀刻至其全深度,其中相对于部分形成的波导自对准。具体地,进一步蚀刻硅器件层21的被蚀刻部分以从部分形成的光波导16将光波导26形成至其全深度。

123.在图1j中,将波导掩模25从光波导26移除。此外,将第二掩模层60沉积在光波导26和硅器件层21上。在该实施方案中,第二掩模层60包括二氧化硅并且具有20nm至50nm的厚度。

124.在图1k中,光刻胶61置于第二掩模层60上以将第一掺杂区40的第一和第二部分图案化。光刻胶61覆盖光波导26的一个横向侧26a,但使光波导26的顶表面74和另一横向侧26b暴露。具体地,光波导的暴露横向侧26b是光波导26的横向侧,第一掺杂区40的第三部分40c从该横向侧突出到第二掺杂区50中。

125.接下来,如图1l所示,通过经由第二掩模层60注入将硼90引入到光波导26的暴露顶表面74和暴露横向侧26b,从而形成第一掺杂区40的第一部分40a和第二部分40b。硼注入相对于水平线(即,位于与沿着box层22的上表面的平面平行的任何平面内的方向)成大约45

°

的角度。以此方式,第一掺杂区40的第一部分40a在第二掺杂区50的整个上表面的顶部上水平地延伸,并且第一掺杂区40的第二部分40b沿着第二掺杂区50的横向侧从第一掺杂区的第一部分40a的端部竖直地延伸到box层22。第一掺杂区40的第三部分40c从第一掺杂区40的第二部分40b的中点水平地延伸到第二掺杂区50中。因此,第一掺杂区40的第一部分40a、第二部分40b和第三部分40c共同类似于英文字母“f”(在该图中是倒f)。

126.硼注入还提供第一掺杂区40的延伸部40d。第一掺杂区40的延伸部40d从第一掺杂区40的第二部分40b、在soi晶片20的box层22的顶部上并与其邻接地水平延伸。

127.在图1m中,移除光刻胶61。

128.接下来,如图1n所示,光刻胶62置于第二掩模层60上。然后将光刻胶62图案化以限定第一重掺杂区63。具体地,在第一掺杂区40的延伸部40d中注入硼以形成p 区(第一重掺杂区63)。第一重掺杂区63是在光波导26的光传播区之外在平板区3中形成。使用标准注入技术。然后移除光刻胶62。

129.在图1o中,另一光刻胶64置于第二掩模层60上并进行图案化以限定第二重掺杂区65。具体地,将第二掺杂剂(与第一掺杂剂的掺杂类型或极性相反,但与硅器件层21的掺杂类型或极性相同)注入到soi晶片20的硅器件层21中、在光波导26的光传播区之外的区域中、在平板区3中。在该实施方案中,注入磷以形成n 区。使用标准注入技术,并且在执行掺杂之后将光刻胶64移除(图1p)。

130.接下来,在1050℃至1100℃下将光电子器件1退火10秒。

131.然后将钝化层70沉积在第二掩模层60的顶部上。钝化层70还可用作波导26的上包覆层,并且掩埋氧化物层22可用作波导26的下包覆层。在图1q所示的示例实施方案中,钝化层70包括二氧化硅并且具有大约500nm的厚度。钝化层70在两个开口67、68处分别被蚀刻直到第一重掺杂区63和第二重掺杂区65。使用标准蚀刻技术、使用光刻胶71来蚀刻开口67、68。然后移除光刻胶71。

132.最后,如图1r所示,穿过钝化层70来沉积电触点72(优选地由铝形成)以分别电连接到第一重掺杂区63和第二重掺杂区65。

133.在图2中示出得到的光电子器件1。第一掺杂区40和第二掺杂区50形成p-n结。在该示例实施方案中,第一掺杂区40是p型掺杂并且第二掺杂区50是n型掺杂。在可选的实施方案中,第一掺杂区可以是n型掺杂并且第二掺杂区可以是p型掺杂。第一掺杂区40由第一部分40a、第二部分40b、第三部分40c和延伸部40d形成。

134.第一掺杂区40的第一部分40a在光电子器件的脊区2中在第二掺杂区50的整个上表面的顶部上水平地延伸。第一掺杂区140的第二部分40b沿着第二掺杂区50的横向侧从第一掺杂区40的第一部分40a竖直地延伸到box层22。

135.第三部分40c作为突出部从第二部分40b的末端之间的点水平地突出到第二掺杂区50中,使得第三部分40c在除了一侧(即,它从第二部分40b延伸的那侧)之外的所有侧都被第二掺杂区50包围。因此,第一掺杂区40的第三部分40c形成延伸到光波导26的光传播区(即,脊部分2)中的第二掺杂区50中的半岛。换句话说,第二掺杂区50在第一掺杂区40的第三部分40c的顶部和下方以及沿着第一掺杂区40的第三部分40c的横向侧延伸。因此,第一掺杂区的所得第一区、第二区和第三区共同类似于英文字母“f”(绕竖直线旋转180

°

)。

136.光电子器件1还包括第一重掺杂区63,在该实施方案中,该第一重掺杂区是p 掺杂。第一重掺杂区63是在光波导26的光传播区之外在平板区3中形成,并且第一掺杂区40的延伸部40d从第一掺杂区40的第二部分40b延伸到第一重掺杂区63。具体地,延伸部40d从第一掺杂区40的第二部分40b到第一重掺杂区63、在box层22的顶部上并与其邻接地水平延伸。

137.光电子器件1还包括第二重掺杂区65,在该实施方案中,该第二重掺杂区是n 掺杂。第二重掺杂区65是在光波导26的光传播区之外在不同的平板区3中形成。

138.穿过钝化层70将电触点72分别设置到第一重掺杂区63和第二重掺杂区65。

139.下面参考图3a至图3f描述根据第二实施方案的制造光电子器件的方法。在图4中示出所得制造的器件。制造的光电子器件100包括具有脊区102和两个横向延伸的平板区103的脊形波导。光电子器件100包括soi晶片120。

140.如图3a所示,并且类似于图1a所示的步骤,最初提供soi晶片120,所述晶片包括硅衬底123、掩埋氧化物(box)层122和硅器件层121(即,顶部硅层)。soi晶片120是3μm晶片,如从衬底23的上表面到box层122的上表面测量到,并且box层122具有400nm的厚度。硅器件层121是n型掺杂,并且将形成光电子器件100的p-n结的第二掺杂区。可选地,可提供未掺杂的硅器件层121,然后将该未掺杂的硅器件层掺杂n种掺杂剂。

141.接下来,如图3b所示,将第一掩模层127沉积在soi晶片120的硅器件层121上。第一掩模层127包括二氧化硅并且具有大约500nm的厚度。在第一掩模层127中形成通到硅器件层121的开口130。开口130延伸到硅器件层121的将形成光波导的一部分。可使用标准图案

化和蚀刻技术来形成开口130。例如,光刻胶可置于第一掩模层127上并且进行图案化以限定穿过第一掩模层127的开口130。可通过hf湿法蚀刻形成开口,并且然后可移除光刻胶。

142.如图3c所示,第一掺杂剂(例如,硼)通过扩散穿过第一掩模层127中的开口130而被引入到硅器件层121,从而形成第一掺杂区140的第三部分140c,如上所讨论。将硼引入到硅器件层121的随后将形成光波导的一部分。第一掺杂区140是p型掺杂。第一掺杂区140的第三部分140c从硅器件层121的上表面朝向soi晶片120的box层122竖直地向下突出到由硅器件层121形成的第二掺杂区150中。

143.在可选的实施方案中,不是通过扩散引入第一掺杂剂,而是可通过注入引入第一掺杂剂。

144.然后移除第一掩模层127。如图3d所示,然后将波导掩模125沉积在硅器件层121上。波导掩模125包括二氧化硅并且具有500nm的厚度。将波导掩模125图案化以限定光波导。因此,沉积波导掩模125,并且使用光刻工艺将掩模图案化以限定光波导。得到的光波导包括第一掺杂区140的第三部分140c。使用标准沉积技术。

145.接下来,如图3e所示,在第二器件层121中蚀刻波导126。可使用标准图案化和蚀刻技术蚀刻波导126以将波导126蚀刻到其全深度。

146.在图3f中,将波导掩模125从光波导126移除,并且将第二掩模层160沉积在光波导126和硅器件层121上。在该示例实施方案中,第二掩模层160包括二氧化硅并且具有20nm至50nm的厚度。

147.该可选制造方法的剩余步骤与上面参考第一实施方案和图1k至图1r描述的那些步骤相同,除了第一掺杂区140的第三部分140c竖直地延伸到第二掺杂区150中,而不是水平地延伸到第二掺杂区150中。

148.因此,然后将光刻胶置于第二掩模层160上以将第一掺杂区140的第一部分140a和第二部分140b图案化。第一掺杂区140的第一部分140a和第二部分140b在图4中示出。光刻胶覆盖光波导126的一个横向侧,但使光波导的顶表面和另一横向侧暴露。

149.通过经由第二掩模层160注入将硼引入光波导126的暴露顶表面和暴露横向侧处,从而形成第一掺杂区140的第一部分140a和第二部分140b。硼注入相对于水平线(即,位于与沿着box层122的上表面的平面平行的任何平面内的方向)成大约45

°

的角度。以此方式,第一掺杂区140的第一部分140a在第二掺杂区150的整个表面的顶部上水平地延伸,并且第一掺杂区140的第二部分140b沿着第二掺杂区150的横向侧从第一掺杂区140的第一部分140a的端部竖直地延伸到box层122。第一掺杂区140的第三部分140c从第一掺杂区140的第一部分140a竖直向下(即,朝向box层122)延伸到第二掺杂区150中。因此,第一掺杂区的第一部分140a、第二部分140b和第三部分140c类似于英文字母“f”(旋转90

°

)。

150.硼注入还提供第一掺杂区140的延伸部140d(在图4中示出)。第一掺杂区140的延伸部140d从第一掺杂区140的第二部分140b、在soi晶片120的box层122的顶部上并与其邻接地水平延伸。然后移除光刻胶。

151.类似于图1n所示的步骤,然后将另一光刻胶置于第二掩模层160上。然后将该光刻胶图案化以限定第一重掺杂区163。具体地,在第一掺杂区140的延伸部140d中注入硼以形成p 区(第一重掺杂区163)。第一重掺杂区163是在光波导126的光传播区之外在平板区103中形成。使用标准注入技术并且然后移除光刻胶。

152.类似于图1o所示的步骤,然后将另一光刻胶置于第二掩模层160上并进行图案化以限定第二重掺杂区165。将第二掺杂剂(与第一掺杂剂的掺杂类型或极性相反,但与硅器件层121的掺杂类型或极性相同)注入到soi晶片120的硅器件层121中、在光波导126的光传播区之外的区域中(在平板区103中)。在该示例实施方案中,注入磷以形成n 区。使用标准注入技术,并且然后在执行掺杂之后将光刻胶移除。

153.然后在1050℃至1100℃下将光电子器件100退火10秒。

154.类似于图1q所示的步骤,然后将钝化层170沉积在第二掩模层160的顶部上。在图1q所示的示例实施方案中,钝化层170包括二氧化硅并且具有大约500nm的厚度。钝化层170在两个开口处分别被蚀刻直到第一重掺杂区163和第二重掺杂区165。使用标准蚀刻技术、使用光刻胶来蚀刻开口167、168。

155.最后,类似于图1r所示的步骤,穿过钝化层170来沉积电触点172(优选地由铝形成)以分别电连接到第一重掺杂区163和第二重掺杂区165。

156.在图4中示出得到的光电子器件100。第一掺杂区140和第二掺杂区150形成p-n结。在该示例实施方案中,第一掺杂区140是p型掺杂并且第二掺杂区150是n型掺杂,但在可选的实施方案中,第一掺杂区可以是n型掺杂区并且第二掺杂区是p型掺杂。第一掺杂区140由第一部分140a、第二部分140b、第三部分140c和延伸部140d形成。

157.第一掺杂区140的第一部分140a在第二掺杂区150的整个上表面的顶部上水平地延伸,并且第一掺杂区140的第二部分140b沿着第二掺杂区150的横向侧从第一掺杂区140的第一部分140a竖直地延伸到box层122。

158.第三部分140c作为突出部从第一部分140a的末端之间的点竖直地突出到第二掺杂区150中,使得第三部分140c在除了一侧(即,它从第一部分140a延伸的那侧)之外的所有侧都被第二掺杂区150包围。因此,第一掺杂区140的第三部分140c形成延伸到光波导126的光传播区中的第二掺杂区150中的半岛。换句话说,第二掺杂区150在第一掺杂区140的第三部分140c的下方并且在第一掺杂区140的竖直地延伸的第三部分140c的两个横向侧上延伸。因此,第一掺杂区的所得第一区、第二区和第三区共同类似于英文字母“f”(旋转90

°

)。

159.光电子器件100还包括第一重掺杂区163,在该实施方案中,该第一重掺杂区是p 掺杂。第一重掺杂区163是在光波导126的光传播区之外在平板区103中形成,并且第一掺杂区140的延伸部140d从第一掺杂区140的第二部分140b延伸到第一重掺杂区163。具体地,延伸部140d从第一掺杂区140的第二部分140b到第一重掺杂区163、在box层122的顶部上并与其邻接地水平延伸。

160.光电子器件100还包括第二重掺杂区165,在该实施方案中,该第二重掺杂区是n 掺杂。第二重掺杂区165是在光波导126的光传播区之外在不同的平板区103中形成。

161.穿过钝化层170将电触点172分别设置到第一重掺杂区163和第二重掺杂区165。

162.图5a示出了移相器,该移相器是图2和图4相应的光电子器件1、100的可能应用。可使用移相器来调制穿过光电子器件1、100的光波导26、126的光的相位。

163.图5b示出了图2和图4相应的光电子器件1、100的另一个可能应用。具体地,图5b示出了由马赫-曾德尔干涉仪实现的相位调制器(光调制器),其包括两个多模干涉(mmi)耦合器/分离器。

164.尽管已经结合上述示例性实施方案描述了本发明,但在给出本公开时,许多等效

修改和变化对于本领域技术人员将是显而易见的。因此,上面阐明的本发明的示例性实施方案应被认为是说明性的,而不是限制性的。在不脱离本发明的精神和范围的情况下,可对所描述的实施方案进行各种变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。