1.本发明涉及传输技术领域,具体涉及一种差分型电路结构的电流采集转换方法。

背景技术:

2.大部分惯性导航系统中采用的加速度计输出的是模拟电流信号,需要通过if转换后才能给导航计算机进行导航解算。

3.现有的电流采集转换,主要为传统型电流采集转换电路,主要包括电流积分器、逻辑判断与控制电路(由比较器和逻辑触发电路组成)、双极性开关电路、恒流源、频标和输出电路,其工作原理为:将加速度计输出的电流信号通过电荷平衡原理实现模拟信号转换为频率信号,通过频率计器的计数得到待测的加速度信号。

4.传统型电流采集转换电路具有信号连续,不丢失信号,接口简单方便等优点,但存在分辨率低、积分电容易受温漂影响,功耗大,体积大,生产调试不方便的缺点。

技术实现要素:

5.本发明是为了解决传统型电流采集转换电路分辨率低、易受温漂影响等问题,提供一种差分型电路结构的电流采集转换方法,以差分型电流采集转换方法代替传统积分电容采集电流转换方法,可满足电流采集信号连续不丢失、有效消除积分电容零位温漂、抗干扰能力强、分辨率高、电路结构简单体积小功率低,生产调试容易等要求。

6.本发明提供一种差分型电路结构的电流采集转换方法,包括以下步骤:

7.s1、将加速度计电流通道输出的电流信号依次通过差分转换电路和数字缓存器进行电容积分、差分转换的采样以及模数转换缓存后得到当前时刻正积分脉冲和当前时刻负积分脉冲,并随着时间累加得到累加正积分脉冲和累加负积分脉冲;

8.s2、数字缓存器判断采样时间是否达到预设时间,如果是,则进入步骤s3,如果否,则返回步骤s1;

9.s3、数字缓存器将累加正积分脉冲和累加负积分脉冲分别输出至a计数器、b计数器得到脉冲计数值a和脉冲计数值b,然后分别输出至减法器,减法器将脉冲计数值a与脉冲计数值b相减获得当前采样时间的电流c:c=a-b;

10.s4、返回步骤s1继续进行下一周期的采样,直至电流采集转换完毕。

11.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,步骤s1包括:

12.s11、加速度计的电流通道输出电流信号ix/iy/iz至差分转换电路;

13.s12、差分转换电路中与反向放大器并联的反馈电容将电流信号ix/iy/iz进行采样后进行电流积分,反馈电容两端的电压随着电流积分电荷累积发生变化,再经运算放大器比较,产生电平翻转,生成模拟脉冲信号输出至数字缓存器;

14.s13、数字缓存器将模拟脉冲信号转化为数字脉冲信号并缓存当前时刻正积分脉冲和当前时刻负积分脉冲;

15.s15、随着时间累加得到累加正积分脉冲和累加负积分脉冲。

16.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,步骤s1中,采样频率为1khz,采样间隔时间为0.001s。

17.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,步骤s3中,脉冲计数值a为所有采样到的加速度计电流值的差分正累加值,

18.a=pos_reg;

19.其中,pos_reg为当前时刻通过系统时钟从数字缓存器读到的差分正累加的脉冲计数值。

20.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,步骤s3中,脉冲计数值b为所有采样到的加速度计电流值的差分负累加值,

21.b=neg_reg;

22.其中,neg_reg为当前时刻通过系统时钟从数字缓存器读到的差分负累加的脉冲计数值。

23.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,电流采集转换方法使用的装置包括:加速度计,与加速度计的输出端电连接的差分转换电路,与差分转换电路的输出端分别电连接的数字缓存器,与数字缓存器分别电连接的a计数器、b计数器和与a计数器、b计数器均相连的减法器。

24.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,差分转换电路的输出端为2个。

25.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,差分转换电路包括与加速度计电连接的反向放大器,与反向放大器并联的反馈电容,与反向放大器和反馈电容的输出端均电连接的运算放大器,运算放大器与数字缓存器电连接。

26.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,运算放大器的输出端为2个。

27.本发明所述的一种差分型电路结构的电流采集转换方法,作为优选方式,数字缓存器为fpga。

28.本发明设计的差分型电流采集转换电路具有信号连续不丢失,差分电路结构,消除积分电容零位温漂、抗干扰能力强、分辨率高、电路结构简单功率低,生产调试容易等特点。

29.本发明的技术解决方案是:

30.一种差分型电路结构的电流采集转换方法,基于可编程逻辑器件实现,

31.步骤如下:

32.(1)对加速度计的电流通道进行电容积分差分采样转换;

33.(2)确定当前时刻的脉冲计数值a;

34.(3)确定当前时刻的脉冲计数值b;

35.(4)判断采样时间是否达到预设时间,如果没有达到预设时间,则返回步骤(1)继续采样,如果达到预设时间,则进入步骤(5);

36.(5)将当前时刻的脉冲计数值a与当前脉冲计数值b进行相减,得到当次采样预设时间的该通道电流转换结果c=a-b,则该次采样转换完成,返回步骤(1)继续采样。

37.所述步骤(1)对加速度计的电流进行周期采样,通过电容积分和差分运算放大器23转换,再经数字缓存模块进行模数转化。

38.对加速度计的电流进行采样时,采样频率为1khz,采样间隔时间为0.001s。

39.所述步骤(2)和(3)脉冲计数值a,b为所有采样到的加速度计的电流值的累加值,

40.c=a-b;

41.其中,a为当前时刻脉冲计数值,b为当前时刻脉冲计数值,c为该周期该通道加速度计的电流采集累加值。所述采样时间为0.001s。

42.本方法基本技术原理是基于带电容积分器的差分采集转换电路,通过采样周期内的数字脉冲采样缓存,产生相应的正负ab脉冲计数值,再通过a和b相减,得到该周期通道加速度计的电流采样累加值结果c。

43.本发明提出了一种适用于可编程逻辑器件实现的加速度计1电流差分型电流采集转换方法,以差分型电流采集转换方法,代替传统积分电容采集电流转换方法,可用于较高精度、较小体积和较低成本的fpga可编程器件,满足了惯导系统中加速度计的电流采集小型化、轻量化发展要求且处理信号较少的应用场合该方法包括了加速度计的电流差分采样转换、采集时间值预设、当前时刻的脉冲计数值a与b、根据判断采样时间,得到通道加速度计的电流采样累加值结果c。

44.本发明具有以下优点:

45.(1)本发明由于采用了差分型电流采集转换方法,以差分型电流采集转换方法,代替传统积分电容采集电流转换方法,满足加速度计1的电流信号连续不丢失的前提下,消除积分电容零位温漂,提高了系统抗干扰性和分辨率,降低了系统能耗;

46.(2)本发明由于采用了差分型电流采集转换方法,节约了电路芯片数目,以通过可编程逻辑器件fpga实现,降低了生产成本,满足了使用小型化、轻量化的需求。

附图说明

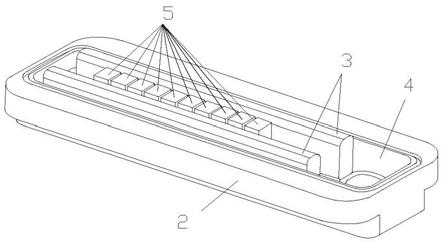

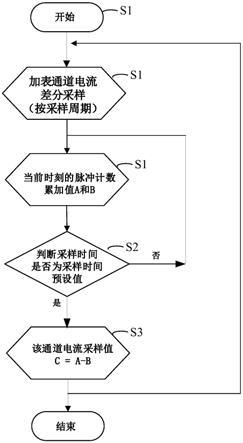

47.图1为一种差分型电路结构的电流采集转换方法流程图;

48.图2为一种差分型电路结构的电流采集转换装置结构示意图;

49.图3为一种差分型电路结构的电流采集转换方法电容积分差分转换电路图。

50.附图标记:

51.1、加速度计;2、差分转换电路;21、反向放大器;22、反馈电容;23、运算放大器;3、数字缓存器;4、a计数器;5、b计数器;6、减法器。

具体实施方式

52.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。

53.实施例1

54.如图1所示,一种差分型电路结构的电流采集转换方法,包括以下步骤:

55.s1、将加速度计1电流通道输出的电流信号依次通过差分转换电路2和数字缓存器3进行电容积分、差分转换的采样以及模数转换缓存后得到当前时刻正积分脉冲和当前时刻负积分脉冲,并随着时间累加得到累加正积分脉冲和累加负积分脉冲;

56.s11、加速度计1的电流通道输出电流信号ix/iy/iz至差分转换电路2;

57.s12、差分转换电路2中与反向放大器21并联的反馈电容22将电流信号ix/iy/iz进行采样后进行电流积分,反馈电容22两端的电压随着电流积分电荷累积发生变化,再经运算放大器23比较,产生电平翻转,生成模拟脉冲信号输出至数字缓存器3;

58.s13、数字缓存器3将模拟脉冲信号转化为数字脉冲信号并缓存当前时刻正积分脉冲和当前时刻负积分脉冲;

59.s15、随着时间累加得到累加正积分脉冲和累加负积分脉冲;

60.采样频率为1khz,采样间隔时间为0.001s;

61.s2、数字缓存器3判断采样时间是否达到预设时间,如果是,则进入步骤s3,如果否,则返回步骤s1;

62.s3、数字缓存器3将累加正积分脉冲和累加负积分脉冲分别输出至a计数器4、b计数器5得到脉冲计数值a和脉冲计数值b,然后分别输出至减法器6,减法器6将脉冲计数值a与脉冲计数值b相减获得当前采样时间的电流c:c=a-b;

63.脉冲计数值a为所有采样到的加速度计1电流值的差分正累加值,

64.a=pos_reg;

65.其中,pos_reg为当前时刻通过系统时钟从数字缓存器3读到的差分正累加的脉冲计数值;

66.脉冲计数值b为所有采样到的加速度计1电流值的差分负累加值,

67.b=neg_reg;

68.其中,neg_reg为当前时刻通过系统时钟从数字缓存器3读到的差分负累加的脉冲计数值;

69.如图2所示,电流采集转换方法使用的装置包括:加速度计1,与加速度计1的输出端电连接的差分转换电路2,与差分转换电路2的输出端分别电连接的数字缓存器3,与数字缓存器3分别电连接的a计数器4、b计数器5和与a计数器4、b计数器5均相连的减法器6;

70.差分转换电路2的输出端为2个;

71.如图3所示,差分转换电路2包括与加速度计1电连接的反向放大器21,与反向放大器21并联的反馈电容22,与反向放大器21和反馈电容22的输出端均电连接的运算放大器23,运算放大器23与数字缓存器3电连接;

72.运算放大器23的输出端为2个;

73.数字缓存器3为fpga。

74.实施例2

75.一种差分型电路结构的电流采集转换方法,包括以下步骤:

76.包括如下步骤:

77.如图1所示,(1)对加速度计1的电流进行采样;

78.对加速度计1的电流通过电容积分和差分运算放大器23转换,电容积分差分采样转换通过将反相放大器中的反馈电容,对输入加速度计1的电流进行电流积分,电容两端电压会随着电流积分电荷累积发生变化,经运算放大器23比较,产生电平翻转,生成脉冲信号,完成采集转换,再经数字缓存模块进行模数转化和采样周期内的数字脉冲采样缓存,对加速度计1的电流进行采样时,采样频率为1khz,采样间隔时间为0.001s。

79.(2)确定当前时刻的脉冲计数值a;

80.脉冲计数值a为所有采样到的加速度计1的电流值的差分正累加值,

81.a=pos_reg;

82.其中,pos_reg为当前时刻,通过系统时钟,从数据缓冲处理模块读到的差分正累加的脉冲计数值。

83.(3)确定当前时刻的脉冲计数值b;

84.脉冲计数值b为所有采样到的加速度计1的电流值的差分正累加值,

85.b=neg_reg;

86.其中,neg_reg为当前时刻,通过系统时钟,从数据缓冲处理模块读到的差分负累加的脉冲计数值。

87.(4)判断采样时间是否达到预设时间,如果没有达到预设时间,则返回步骤(1)继续采样,如果达到预设时间,则进入步骤(5);

88.(5)将当前时刻的脉冲计数值a与当前脉冲计数值b进行相减,得到当次采样预设时间的该通道电流转换结果c=a-b,则该次采样转换完成,返回步骤(1)继续采样。

89.数字缓存模块为fpga。

90.如图2所示,将加速度计输出的电流信号ix/iy/iz,通过电容积分和电荷平衡原理实现模拟信号转换为频率信号,信号转换通过差分采集电路进行差分转换,转换生成差分正端a或差分负端b的信号,该信号通过系统fpga时钟,根据系统时钟进行调制解调,最终通过数字缓存模块得到该时刻相应的正负ab脉冲计数值,再通过a和b相减,得到该周期通道加速度计1的电流采样累加值结果c。对加速度计1的电流进行采样时,采样频率为1khz,采样间隔时间为0.001s。具体电路如图3所示。

91.以上所述,仅为本发明较佳的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,根据本发明的技术方案及其发明构思加以等同替换或改变,都应涵盖在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。