1.本公开大体上涉及半导体装置,并且更具体地说,涉及横向扩散金属-氧化物半导体(ldmos)晶体管及其形成方法。

背景技术:

2.传统的半导体装置和半导体装置制造工艺是众所周知的。例如,金属氧化物半导体场效应晶体管(mosfet)通常用于各种不同的应用和电子产品-从缝纫机到洗衣机、从汽车到蜂窝电话等等。随着工艺技术的进步,这些半导体装置预期会在减小尺寸和成本的同时提高性能。然而,在平衡大小、成本、性能和长期可靠性方面存在挑战。

技术实现要素:

3.总的来说,提供一种晶体管,包括:沟槽,其在半导体衬底中形成;导电间隔物,其形成在所述沟槽中,所述导电间隔物从所述沟槽的第一侧壁偏移;电介质材料,其形成在所述沟槽中,所述电介质材料基本上包围所述导电间隔物;漂移区,其邻近于所述第一侧壁和所述沟槽的第二侧壁的第一部分形成在所述半导体衬底中,所述漂移区具有第一导电类型;漏极区,其形成在所述漂移区中,所述漏极区邻近于所述第二侧壁的第二部分;以及第一栅极区,其与所述漂移区的一部分重叠,所述第一栅极区与所述导电间隔物分离。所述晶体管可另外包括与所述第一栅极区间隔开并且形成在所述电介质材料上方的第二栅极区,所述第二栅极区与所述导电间隔物间隔开。所述晶体管可另外包括形成在所述第一栅极区与所述第二栅极区之间的所述漂移区和所述电介质材料上方的非导电层,所述非导电层与所述第一栅极区的一部分重叠。所述晶体管可另外包括借助于第一接触件导电连接到所述导电间隔物的第一导电迹线。所述晶体管可另外包括借助于第二接触件导电连接到所述第一栅极区的第二导电迹线,所述第二导电迹线连接到所述第一导电迹线。所述晶体管另外包括形成在所述半导体衬底中的源极区,所述第一栅极区在所述源极区与所述第一侧壁之间形成在所述半导体衬底上方。所述晶体管可另外包括邻近于所述漂移区形成在所述半导体衬底中的具有第二导电类型的主体区,所述源极区形成在所述主体区中。所述晶体管可另外包括借助于第三接触件导电连接到所述源极区的第三导电迹线,所述第三导电迹线连接到所述第一导电迹线。所述导电间隔物和所述第一栅极区可由多晶硅材料形成,所述导电间隔物和所述第一栅极区由不同的多晶硅材料层沉积形成。

4.在另一实施例中,提供一种方法,包括:在半导体衬底中蚀刻沟槽,所述沟槽具有第一侧壁和第二侧壁;以沉积在所述沟槽中的第一导电层形成基本上竖直的导电间隔物,所述导电间隔物接近于所述第一侧壁;沉积电介质材料以基本上填充所述沟槽,所述电介质材料基本上包围所述导电间隔物;在所述半导体衬底中形成邻近于所述第一侧壁和所述第二侧壁的第一部分的漂移区,所述漂移区具有第一导电类型;在所述漂移区中形成漏极区,所述漏极区邻近于所述第二侧壁的第二部分;以及以沉积在所述半导体衬底上方的第二导电层形成第一栅极区,所述第一栅极区与所述漂移区的一部分重叠。所述方法可另外

包括以所述第二导电层形成第二栅极区,所述第二栅极区形成在所述电介质材料上方。所述方法可另外包括在所述第一栅极区与所述第二栅极区之间的所述漂移区和所述电介质材料上方形成非导电层,所述非导电层与所述第一栅极区的一部分重叠。所述第一导电层和所述第二导电层可各自由多晶硅材料形成。所述方法可另外包括在所述半导体衬底中形成源极区,所述第一栅极区在所述源极区与所述第一侧壁之间形成在所述半导体衬底上方。所述方法可另外包括邻近于所述漂移区在所述半导体衬底中形成具有第二导电类型的主体区,所述源极区形成在所述主体区中。所述方法可另外包括在所述半导体衬底上方形成栅极电介质层,所述第二导电层沉积在所述栅极电介质层上。

5.在又一实施例中,提供一种方法,包括:在半导体衬底中蚀刻沟槽,所述沟槽具有第一侧壁、第二侧壁以及底表面;用导电材料在所述沟槽的所述第一侧壁、所述第二侧壁和所述底表面上沉积电介质层以形成栅极区;在所述电介质层上沉积第一导电层;选择性地蚀刻所述第一导电层以移除接近于所述第二侧壁和所述沟槽的所述底表面的所述第一导电层,由接近于所述第一侧壁的其余导电层形成导电间隔物;使电介质材料沉积以基本上填充所述沟槽,所述电介质材料基本上包围所述导电间隔物;在所述半导体衬底中形成邻近于所述第一侧壁和所述第二侧壁的第一部分的漂移区,所述漂移区具有第一导电类型;在所述漂移区中形成漏极区,所述漏极区邻近于所述第二侧壁的第二部分;以及以沉积在所述半导体衬底上方的第二导电层形成第一栅极区,所述第一栅极区与所述漂移区的一部分重叠。所述方法可另外包括在所述半导体衬底中邻近于所述漂移区形成主体区,所述主体区具有第二导电类型;以及在所述主体区中形成源极区,所述第一栅极区在所述源极区与所述第一侧壁之间形成在所述半导体衬底上方。所述方法可另外包括形成导电连接到所述导电间隔物的第一接触件;形成导电连接到所述第一栅极区的第二接触件;形成导电连接到所述源极区的第三接触件;以及将所述第一接触件与所述第二接触件或所述第三接触件互连。所述第一导电层和所述第二导电层可各自由多晶硅材料形成。

附图说明

6.本发明通过举例说明,并且不受附图限制,附图中相似标号指示类似元件。为简单和清晰性起见,示出了图式中的元件,并且所述元件不一定按比例绘制。

7.图1至图9以简化的横截面视图示出根据实施例的示例横向扩散金属-氧化物半导体(ldmos)晶体管的各个制造阶段。

8.图10a和图10b以简化的横截面视图和对应的平面视图示出根据实施例的示例导电间隔物布置。

9.图11a至图11c以简化的横截面视图和对应的平面视图示出根据实施例的替代性示例导电间隔物布置。

具体实施方式

10.总的来说,提供一种浅沟槽隔离(sti)横向扩散金属氧化物半导体(ldmos)晶体管。沟槽形成在ldmos晶体管的衬底的漂移区中。漏极区邻近于沟槽的第一侧壁形成在半导体衬底的表面处。在与沟槽的第二侧壁分离预定距离的半导体衬底的表面处形成源极区。导电间隔物接近于沟槽的第二侧壁在沟槽中形成。在形成导电间隔物之后,用电介质材料

填充沟槽。导电间隔物被配置成用于降低沟槽的第一侧壁处的碰撞电离,从而改进ldmos晶体管的总体可靠性。

11.图1至图9以简化的横截面视图示出根据实施例的示例横向扩散金属-氧化物半导体(ldmos)晶体管100的各个制造阶段。

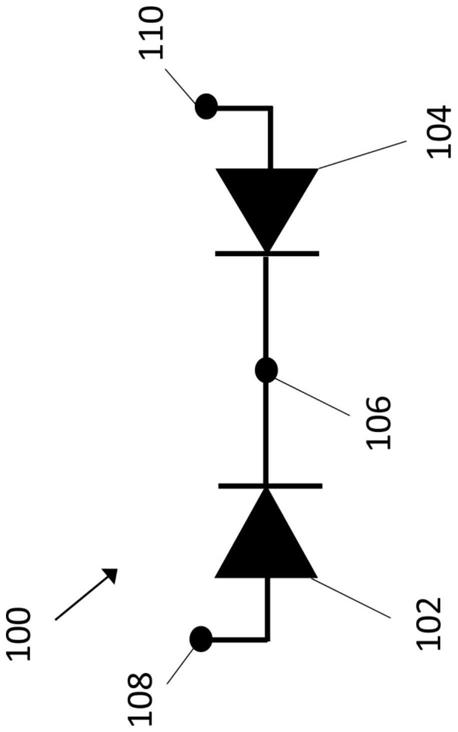

12.图1以简化的横截面视图示出根据实施例的在制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括基于硅的衬底102和形成在衬底102上方的硬掩模104。在此实施例中,衬底102形成为具有p型导电类型的p型掺杂硅衬底。衬底102可形成为具有n型外延层的p型掺杂硅衬底。例如,衬底102可替代地由其它合适的基于硅的衬底形成,所述基于硅的衬底例如砷化镓、锗化硅、绝缘体硅(soi)、硅、单晶硅等,以及其组合等。

13.在此实施例中,氮化物层106形成在上衬底102上,并且氧化物层108形成在氮化物层106上。将氮化物层/氧化物层一起图案化以形成硬掩模104。在其它实施例中,其它合适的材料和其组合可用于形成硬掩模104。

14.图2以简化的横截面视图示出根据实施例的在后续制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括形成在衬底102中的浅沟槽202和204。在此实施例中,沟槽202包括第一侧壁206、第二侧壁208以及底表面210。沟槽204包括第一侧壁212和底表面214。在此实施例中,沟槽202和204被蚀刻到大约0.3微米的预定深度。在其它实施例中,沟槽202和204可被蚀刻到除了大约0.3微米之外的深度。例如,可采用例如反应离子蚀刻(rie)之类的蚀刻技术以形成沟槽202和204。

15.图3以简化的横截面视图示出根据实施例的在后续制造阶段的示例ldmos晶体管100。在此阶段,晶体管100包括形成在衬底102上方的非导电层302。非导电层302可由例如原硅酸四乙酯(teos)之类的沉积氧化物层形成。在此实施例中,非导电层302形成为在沟槽202和204的侧壁处具有大约0.1微米的预定厚度。在其它实施例中,非导电层302可形成为不同于大约0.1微米的期望厚度。

16.图4以简化的横截面视图示出根据实施例的在后续制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括形成在非导电层302上的导电层402。导电层402可例如由沉积多晶硅材料形成。在此实施例中,导电层402形成为在沟槽202和204的侧壁处具有大约0.1微米的预定厚度。在其它实施例中,导电层402可形成为不同于约0.1微米的期望厚度。

17.图5以简化的横截面视图示出根据实施例的在后续制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括由导电层402形成的导电间隔物502、504和506。在此实施例中,导电层402借助于各向异性蚀刻工艺来蚀刻。结果,导电层402的部分保持在沟槽202和204的侧壁处,因此形成导电间隔物502、504和506。在该实施例中,导电间隔物502、504和506从相应侧壁212、206和208偏移大约等于非导电层302的厚度(例如,约0.1微米)的距离。

18.图6以简化的横截面视图示出根据实施例的在后续制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括在掩模和蚀刻工艺步骤之后剩余的导电间隔物504。在此实施例中,光致抗蚀剂材料602被图案化以遮蔽导电间隔物504。在掩模工艺步骤之后,蚀刻工艺步骤用于去除导电间隔物502和506。

19.图7以简化的横截面视图示出根据实施例的在后续制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括电介质材料702和704,所述电介质材料702和704被沉积以基本上填充沟槽202和204并且基本上包围导电间隔物504。例如,电介质材料702和704可由

例如teos之类的沉积氧化物层形成。在此实施例中,电介质材料702和704以及非导电层302由相同氧化物材料形成。在其它实施例中,电介质材料702和704以及非导电层302可由不同的材料形成。在用电介质材料702和704填充沟槽202和204之后,可执行热操作以使沉积的电介质材料702和704致密。然后执行平坦化操作以平整(level)晶体管100的顶表面。硬掩模104的氮化物层106充当用于平坦化操作的终止层。在此实施例中,平坦化操作可包括化学机械平坦化(cmp)工艺。在平坦化操作之后,借助于蚀刻工艺移除氮化物层106。

20.图8以简化的横截面视图示出根据实施例的在后续制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括形成在衬底102中的主体区802和漂移区804。在此实施例中,主体区802邻近于侧壁212和底表面214形成为衬底102中的p型阱掺杂剂注入区。主体区802可表征为p-(减)主体区。漂移区804邻近于侧壁206、208和底表面210形成为衬底102中的n型阱掺杂剂注入区。漂移区804可表征为n-(减)漂移区。在一些实施例中,漂移区804可由衬底102的n型外延层形成。

21.图9以简化的横截面视图示出根据实施例的在后续制造阶段中的示例ldmos晶体管100。在此阶段,晶体管100包括源极区902、漏极区904、栅极区908-910、栅极间隔物914、接触件918-924、导电迹线926-932以及夹层电介质(ild)区940。

22.在此实施例中,栅极电介质层912形成在衬底102的暴露顶表面938上。栅极电介质912可由任何合适的栅极电介质材料(例如,二氧化硅)形成。栅极电介质912可形成为生长层、沉积层或其组合。第一栅极区908和第二栅极区910形成在栅极电介质912上。例如,栅极区908和910可由例如多晶硅材料或金属材料之类的合适的导电材料形成。在此实施例中,栅极区908和910被配置并布置成充当例如ldmos晶体管100之类的栅极电极。在其它实施例中,栅极区908和910可由其它导电材料形成。栅极间隔物914在栅极区908与栅极区910之间形成在栅极电介质912上。栅极间隔物914的一部分与栅极区908的一部分重叠。栅极间隔物914由非导电层形成,所述非导电层被沉积并图案化以覆盖栅极区908与910之间的漂移区804和电介质材料702的部分。在此实施例中,栅极间隔物914可由例如氮化硅之类的合适的非导电层材料形成。在此实施例中,在形成栅极间隔物914的相同工艺步骤期间栅极侧壁间隔物916形成在栅极区908和910的外侧壁上。

23.在形成主体区802和漂移区804之后,注入n型掺杂剂以分别形成源极区902和漏极区904。源极区902和漏极区904可分别表征为n (加)源极区/漏极区。在主体区802中注入p型掺杂剂以形成主体连接区906,从而允许与主体区802的电连接性。主体连接区906可表征为p (加)主体连接区。在此实施例中,主体连接区906邻接源极区902。漏极区904邻近于侧壁208的一部分形成。随着横向距离942增加,晶体管100的对应击穿电压增加。在此实施例中,横向距离942被表征为与沟槽202的宽度相对应的漂移距离。例如,沟槽202的宽度可确定为侧壁206与208之间的距离。在一些实施例中,硅化物区(图中未示)可形成在源极区902和漏极区904以及主体连接区906的顶表面处。硅化物区可用于在源极区902和漏极区904以及主体连接区906的顶表面处形成高导电性接触区。

24.在此实施例中,ild区940形成在栅极区908和910、栅极间隔物914和侧壁间隔物916以及衬底102的暴露顶表面938上方。ild区940可由例如teos之类的一系列沉积氧化物层形成。例如,ild区940的第一氧化物层可被沉积、图案化和蚀刻以暴露栅极区908、源极区902和漏极区904以及导电间隔物504的部分。在图案化和蚀刻第一氧化物层之后,形成接触

件918-924。例如,接触件918-924可由例如铜、金、银、铝、镍、钨及其合金之类的任何合适的导电材料形成。接触件918-924分别提供到源极区902和主体连接区906、栅极区908、导电间隔物504以及漏极区904的导电连接。

25.在形成接触件918-924之后,导电层被沉积、图案化和蚀刻以形成导电迹线926-932。导电迹线926-932可由例如铜和铝之类的任何合适的导电材料形成。在此实施例中,可能需要将导电间隔物504连接到已知电压源,而不允许其浮动。例如,在一些实施例中,导电间隔物504可借助于互连件934(例如,示出为虚线)、导电迹线926和930以及相应接触件918和922互连到源极区902。在一些实施例中,导电间隔物504可借助于互连件934(例如,示出为虚线)、导电迹线928及930及相应接触件920及922互连到栅极区908。

26.图10a和图10b以简化的横截面视图和对应的平面视图示出根据实施例的示例导电间隔物布置1000。在图10a的简化平面视图中,示出了示例ldmos晶体管100的一部分,包括已填充的沟槽1002、导电间隔物1004以及接触件1006。图10b中描绘了沿着线a-a的对应横截面视图。例如,已填充的沟槽1002对应于图9的电介质材料填充的沟槽702,导电间隔物1004对应于图9的导电间隔物504,并且接触件1006对应于图9的接触件922。内侧壁1010对应于邻近于图9的漏极区904的侧壁208,并且外侧壁1008对应于图9的侧壁206。在本实施例中,多个接触件1006沿着导电间隔物1004的一部分形成。此处,接触件1006被布置成基本上与导电间隔物1004的顶边缘对齐,并且基本上与已填充的沟槽1002的顶表面平齐。

27.图11a至图11c以简化的横截面视图和对应的平面视图示出根据实施例的替代性示例导电间隔物布置1100。在图11a的简化平面视图中,示出了类似晶体管100的示例ldmos晶体管的一部分,包括已填充的沟槽1102、带有导电突片的导电间隔物1104以及接触件1106。图11b中描绘了沿着线b-b的对应横截面视图,图11c中描绘了沿着线c-c的横截面视图。在本实施例中,已填充的沟槽1102对应于图9的电介质材料填充的沟槽702,并且导电间隔物1104对应于图9的导电间隔物504。内侧壁1110对应于邻近于图9的漏极区904的侧壁208,并且外侧壁1108对应于图9的侧壁206。在此实施例中,导电突片与导电间隔物1104的形成一起形成。每个突片为接触件1106提供更广泛的登录或连接接口。突片形成并且沿着导电间隔物1104的一部分分布。此处,接触件基本上与突片的上边缘对齐,并且基本上与已填充的沟槽1102的顶表面平齐。因为突片比导电间隔物1104的厚度更宽(例如,约2x宽),所以当将接触件1106与突片对齐时存在更多的间距。

28.到目前为止应了解,提供一种sti ldmos晶体管。沟槽形成在ldmos晶体管的衬底的漂移区中。漏极区邻近于沟槽的第一侧壁形成在半导体衬底的表面处。在与沟槽的第二侧壁分离预定距离的半导体衬底的表面处形成源极区。导电间隔物接近于沟槽的第二侧壁在沟槽中形成。在形成导电间隔物之后,用电介质材料填充沟槽。导电间隔物被配置成用于降低沟槽的第一侧壁处的碰撞电离,从而改进ldmos晶体管的总体可靠性。

29.虽然本文中参考具体实施例描述了本发明,但是可以在不脱离如所附权利要求书中所阐述的本发明的范围的情况下进行各种修改和改变。因此,应在说明性而非限制性意义上看待本说明书和图式,并且预期所有此类修改都包括在本发明的范围内。并不意图将本文中关于具体实施例所描述的任何益处、优点或问题的解决方案理解为任何或所有权利要求的关键、必需或必不可少的特征或元件。

30.另外,如本文中所使用的,术语“一(a)”或“一个(an)”被限定为一个或多于一个。

而且,权利要求书中例如“至少一个”和“一个或多个”等介绍性短语的使用不应被解释为暗示由不定冠词“一(a)”或“一个(an)”引入的另一权利要求要素将含有此类引入的权利要求要素的任何特定权利要求限于仅含有一个此类要素的发明,甚至是在同一权利要求包括介绍性短语“一个或多个”或“至少一个”和例如“一(a)”或“一个(an)”等不定冠词时。这同样适用于定冠词的使用。

31.除非另外说明,否则例如“第一”和“第二”的术语用于任意地区分此类术语所描述的元件。因此,这些术语未必意图指示此些元件的时间上的优先级或其它优先级。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。