半导体封装

1.相关申请的交叉引用

2.该申请要求2020年9月23日向韩国知识产权局提交的韩国专利申请第10-2020-0122861号的优先权,其全部公开内容通过引用并入本文。

技术领域

3.本发明构思涉及半导体封装,更具体地涉及一种包括堆叠芯片结构的半导体封装。

背景技术:

4.近来在电子产品市场中,对便携式设备的需求迅速增加,因此对安装在此类电子产品中的电子部件的小型化和轻量化的兴趣不断增加。为了减小电子部件的尺寸和重量,安装在其上的半导体封装可以在进一步减小其体积的同时处理大容量数据。需要一种安装在这种半导体封装上的高集成度和单一封装的半导体芯片。

技术实现要素:

5.本发明构思的示例实施例提供了一种包括多个堆叠的半导体芯片的半导体封装。

6.根据示例实施例,提供了一种半导体封装。所述半导体封装包括包含第一半导体芯片的第一结构和在所述第一结构上的第二结构。所述第二结构包括第二半导体芯片、与所述第二半导体芯片水平地间隔开并位于所述第二半导体芯片的侧面上的半导体图案、所述第二半导体芯片与所述半导体图案之间的绝缘间隙填充图案、以及贯通电极结构。所述贯通电极结构中的至少一个贯穿所述第二半导体芯片的至少一部分或贯穿所述半导体图案。

7.根据示例实施例,提供了一种半导体封装。所述半导体封装包括包含第一半导体芯片的第一结构以及在所述第一结构上的第二结构。所述第二结构包括接合至第一半导体芯片的接合结构、所述接合结构上的第二半导体芯片、位于所述接合结构上并与所述第二半导体芯片水平地间隔开的半导体图案、以及位于所述接合结构上并在所述第二半导体芯片和所述半导体图案之间的绝缘间隙填充图案。所述第一半导体芯片包括第一半导体衬底与第一电路区,所述第二半导体芯片包括第二半导体衬底与第二电路区,并且所述第一电路区与所述第二电路区在所述第一半导体衬底与所述第二半导体衬底之间。

8.根据示例实施例,提供了一种半导体封装。所述半导体封装包括第一半导体芯片、所述第一半导体芯片上的第二半导体芯片、所述第一半导体芯片上并与所述第二半导体芯片水平地间隔开的半导体图案、以及所述第二半导体芯片与所述半导体图案之间的绝缘间隙填充图案。所述半导体图案与所述第二半导体芯片之间的距离为约0.5微米(μm)至约10微米,所述第二半导体芯片的厚度为约3微米至约10微米,所述第一半导体芯片的厚度大于所述半导体图案与所述第二半导体芯片之间的距离,并且所述第一半导体芯片的厚度大于所述半导体图案的厚度和所述第二半导体芯片的厚度。

附图说明

9.通过结合附图的以下详细描述,本公开的以上和其他方面、特征和优势将变得清楚明白,其中

10.图1a至图1c是示意性地说明根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的视图;

11.图2是示意性示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的分解透视图;

12.图3a是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性截面图;

13.图3b是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性截面图;

14.图3c是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性截面图;

15.图4a和图4b是示意性地示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的截面图;

16.图5a和图5b是示意性地示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的截面图;

17.图6和图7是示意性地示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的图;

18.图8是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性截面图;

19.图9是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性截面图;

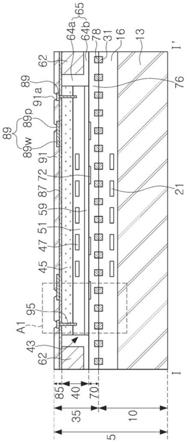

20.图10是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性截面图;

21.图11a和图11b是示意性地示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的图;

22.图12是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性平面图;

23.图13是示出根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的修改示例的示意性截面图;

24.图14是示出根据本发明构思的示例实施例的半导体封装件的示例的示意性截面图;

25.图15是根据本发明构思的示例实施例的半导体封装的另一示例的示意性截面图;

26.图16是根据本发明构思的示例实施例的半导体封装的另一示例的示意性截面图;以及

27.图17a至图19是示意性地示出根据本发明构思的示例实施例的制造半导体封装的堆叠芯片结构的方法的截面图。

具体实施方式

28.下文中将参考附图描述本发明构思的示例实施例。

29.根据本发明构思的示例实施例的半导体封装可以包括堆叠芯片结构。将参照图1a至图1c描述根据示例实施例的半导体封装的堆叠芯片结构的示例。图1a是示意性地说明根据本发明构思的示例实施例的半导体封装的堆叠芯片结构的示例的分解透视图,以及图1b是示出沿图1a的线i-i

′

截取的区域的示意性截面图。

30.参考图1a和图1b,根据示例实施例的半导体封装的堆叠芯片结构5可以包括第一结构10和在第一结构10上的第二结构35。

31.第一结构10可以包括第一半导体芯片。在这里的讨论中,第一结构10也可以称作第一半导体芯片10。例如,第一结构10的第一半导体芯片可以包括第一半导体衬底13和在第一半导体衬底13上的第一电路区16。第一电路区16可以包括第一电路器件21和可以电连接到第一电路器件21的第一接合焊盘31。

32.在一个实施例中,第一结构10可以称作第一半导体芯片。应当理解的是尽管这里可以使用术语第一、第二、第三等来描述各种元件,但是这些元件不应受这些术语的限制;相反,这些术语仅用于将一个元件与另一个元件区分开来。因此,在不脱离本发明构思的范围的情况下,所讨论的第一元件可以称作第二元件。

33.第二结构35可以包括中间结构40。在一个示例中,第二结构35还可以包括在中间结构40和第一结构10之间的接合结构70。第一电路区16可以设置在第一半导体衬底13和结合结构70之间。

34.在一个示例中,第二结构35还可以包括位于中间结构40上的背面结构85。中间结构40可以设置在背面结构85和接合结构70之间。背面结构85可以称作封盖结构。

35.中间结构40可以包括第二半导体芯片43、与第二半导体芯片43水平地间隔开(例如,在与第一半导体衬底13的上表面平行的方向上)的半导体图案62、以及在第二半导体芯片43和半导体图案62之间的绝缘间隙填充图案65。

36.在一个示例中,半导体图案62可以围绕(例如,在平面图中)第二半导体芯片43。应当理解,这里使用的“元件a围绕元件b”(或类似语言)意味着元件a至少部分地围绕元件b,但并不一定意味着元件a完全包围元件b。在一个示例中,半导体图案62和第二半导体芯片43之间的距离可以是约0.5μm至约10μm。在一个示例中,半导体图案62和第二半导体芯片43之间的距离可以是约1μm至约4μm。在一个示例中,半导体图案62和第二半导体芯片43之间的距离可以是约2.5μm至约3.5μm。

37.在一个示例中,第二半导体芯片43的厚度(例如,在与第一半导体衬底13的上表面竖直/垂直的方向上)可以是约3μm至约10μm。如本文所使用的,术语“和/或”包括一个或多个相关联的所列项目的任意和所有组合。

38.在一个示例中,第一结构10的厚度(例如,第一半导体芯片的厚度)可以大于半导体图案62和第二半导体芯片43之间的距离。在一个示例中,第一半导体芯片10的厚度可以大于半导体图案62和第二半导体芯片43中的每一个的厚度。

39.在一个示例中,第一半导体芯片10的宽度(例如,在水平方向上)可以大于第二半导体芯片43的宽度。在一个示例中,第二半导体芯片43的宽度可以大于半导体图案62的宽度。

40.第二半导体芯片43可以包括第二半导体衬底45、第二电路区51和保护绝缘层59。第二电路区51可以设置在第二半导体衬底45和接合结构70之间。第二电路区51可以包括第二电路器件47。保护绝缘层59可以在第二电路区51的与接合结构70相邻的表面上和/或覆盖该表面。保护绝缘层59可以接触接合结构70。

41.第一电路区16和第二电路区51可以设置在第一半导体衬底13和第二半导体衬底45之间。

42.在一个示例中,半导体图案62可以在第二半导体芯片43的侧表面上和/或围绕该侧表面。例如,半导体图案62可以具有四边环形状。半导体图案62的外侧表面可以与第一结构10和/或第一半导体芯片10的侧表面竖直地对齐。

43.半导体图案62可以由硅材料形成和/或可以形成在与第二电路区51相同的高度水平处(例如,水平线可以穿过半导体图案62的一部分和第二电路区51的一部分)。在一些实施例中,高度水平可以指相对于第一半导体衬底13的上表面的距离(例如,垂直距离)。在一些实施例中,半导体图案62可以不包括与第二电路区51在相同高度水平的半导体集成电路。例如,位于与第二半导体芯片43相同高度水平的半导体图案62的一部分可以不包括半导体集成电路。

44.在一个示例中,半导体图案62的厚度可以大于第二半导体芯片43的第二半导体衬底45的厚度。

45.绝缘间隙填充图案65可以包括诸如氧化硅等的绝缘材料。在一个示例中,绝缘间隙填充图案65可以包括设置在半导体图案62和第二半导体芯片43之间(例如,在水平方向上)的第一部分64a,以及设置在半导体图案62和第一结构10之间(例如,在竖直方向上)的第二部分64b。绝缘间隙填充图案65的第一部分64a和第二部分64b可以接触半导体图案62。

46.接合结构70可以包括绝缘层76;绝缘层76中的中间连接布线72,中间连接布线72可以电连接到第二电路器件47;以及第二接合焊盘78,第二接合焊盘78可以电连接到绝缘层76中的中间连接布线72。第二接合焊盘78可以在与第一结构10的第一接合焊盘31接触的同时接合。

47.第一接合焊盘31和第二接合焊盘78可以包括相同的金属材料。例如,第一接合焊盘31和第二接合焊盘78可以包括铜材料。

48.背面结构85可以包括背面绝缘层87、背面绝缘层87上的背面导电图案89以及具有暴露所述背面导电图案89的焊盘区域89p的开口91a的封盖绝缘层91,封盖绝缘层91位于背面导电图案89上。背面绝缘层87可以接触中间结构40。背面绝缘层87可以称作第一封盖绝缘层87,而封盖绝缘层91可以称作第二封盖绝缘层91。背面导电图案89也可以称作重分布导电图案89。

49.在背面导电图案89中,封盖绝缘层91覆盖的部分可以被定义为布线区89w或重分布区89w。背面绝缘层87可以包括诸如氧化硅的绝缘材料。背面导电图案89可以包括诸如铜或铝的金属材料。封盖绝缘层91可以包括诸如氮化硅或聚酰亚胺的材料。

50.在一个示例中,第二结构35还可以包括贯通电极结构95。贯通电极结构95中的至少一个可以贯穿第二半导体芯片43的至少一部分或半导体图案62。例如,贯通电极结构95中的至少一个可以贯穿第二半导体芯片43的至少一部分。

51.在一个示例中,第一结构10的第一半导体芯片10和第二结构35的第二半导体芯片

43中的至少一个可以是微处理器、图形处理器、信号处理器、网络处理器、芯片组、音频编解码器、视频编解码器、应用处理器或存储芯片。存储芯片可以是易失性存储芯片或非易失性存储芯片。例如,易失性存储器芯片可以包括动态随机存取存储器(dram)、静态ram(sram)、晶闸管ram(tram)、零电容ram(zram)或双晶体管ram(ttram)。此外,非易失性存储器芯片可以包括例如闪存、磁ram(mram)、自旋转移矩mram(stt-mram)、铁电ram(fram)、相变ram(pram)、电阻ram(rram)、纳米管rram、聚合物ram、纳米浮栅存储器、全息存储器、分子电子存储器或绝缘体电阻变化存储器。

52.在另一个示例中,第一结构10的第一半导体芯片10和第二结构35的第二半导体芯片43中的一个可以是易失性存储芯片或非易失性存储芯片,而另一个可以是用于驱动存储芯片的控制半导体芯片。

53.在另一个示例中,第一结构10的第一半导体芯片10和第二结构35的第二半导体芯片43中的一个可以是图像传感器芯片,且另一个可以是逻辑半导体芯片。

54.接下来,将参考图1c描述第一结构10和第二结构35的示例。图1c是表示图1b的“a1”所示部分的一个例子的局部放大截面图。

55.参考图1c,第一结构10的第一电路区16可以包括在第一半导体衬底13上限定第一有源区19a的第一隔离层19s、在第一有源区19a上的第一电路器件21、可以电连接到第一电路器件21的第一电路布线25、可以电连接到第一电路布线25的第一接合焊盘31、上表面与第一接合焊盘31的上表面共面并围绕第一接合焊盘31的侧表面的第一接合绝缘层29、以及设置在第一接合绝缘层29和第一半导体衬底13之间的第一绝缘结构27。

56.第一电路布线25可以包括第一绝缘结构27中的竖直部分25v和水平部分25h,并且可以将第一接合焊盘31和第一电路器件21电连接。

57.在一个示例中,第一电路器件21可以包括晶体管,所述晶体管包括在第一有源区19a上的栅极23g和第一有源区19a中在栅极23g两侧上的源极/漏极23sd。第一电路器件21不限于晶体管,并且可以包括构成半导体集成电路的各种器件。

58.第二半导体芯片43的第二电路区51可以包括在第二半导体衬底45下方限定第二有源区49a的第二隔离层49s、在有源区49a下方的第二电路器件47、可以电连接到第二电路器件47的第二电路布线55、以及第二绝缘结构57,其在保护绝缘层59和第二半导体衬底45之间。第二电路布线55可以包括水平部分55h和竖直部分55v,并且可以电连接到第二电路器件47。背面绝缘层87可以接触第二半导体衬底45的背面。

59.在一个示例中,第二电路器件47可以包括晶体管,所述晶体管包括在第二有源区49a下方的栅极53g和第二有源区49a中在栅极53g两侧的源极/漏极53sd。第二电路器件47不限于晶体管,并且可以包括构成半导体集成电路的各种器件。

60.每个贯通电极结构95可以包括贯通电极94a和在贯通电极94a的侧表面上和/或围绕该侧表面的绝缘间隔物94b。在一个示例,贯通电极结构95可以延伸穿过背面绝缘层87。例如,贯通电极结构95的贯通电极94a可以将背面导电图案89以及第二半导体芯片43的第二电路布线55电连接。

61.保护绝缘层59可以包括诸如氮化硅的绝缘材料。第二绝缘结构57可以在至少与保护绝缘层59接触的区域中包括诸如氧化硅的绝缘材料。

62.接合结构70可以包括可以在接触第一接合绝缘层29的同时接合的第二接合绝缘

层75、可以在接触第一接合焊盘31的同时接合的第二接合焊盘78、设置在第二接合绝缘层75和中间结构40之间的中间绝缘层74、以及包括竖直部分72v和水平部分72h的中间连接布线72,中间连接布线72在中间绝缘层74中并电连接到第二接合焊盘78。接合绝缘层75和中间绝缘层74可以是接合结构70的绝缘层76。

63.在一个示例中,第一接合绝缘层29和第二接合绝缘层75可以由绝缘材料形成,例如允许第一接合绝缘层29和第二接合绝缘层75彼此接触并且彼此接合的氧化硅。可以使第一接合绝缘层29和第二接合绝缘层75接合并接触的绝缘材料不限于氧化硅,而可以是其他绝缘材料。例如,第一接合绝缘层29和第二接合绝缘层75可以由sicn等形成。

64.中间连接布线72的竖直部分72v的一部分可以延伸到第二电路区51中以电连接至第二电路布线55。

65.在下文中,将结合附图重点描述堆叠芯片结构的修改或替换部分。另外,通过直接参考而不单独描述,将省略或与其他组件一起描述对堆叠芯片结构的实质上未修改部分的组件的描述。

66.接下来,将参考图2描述中间结构40的修改示例。图2是图1a的分解透视图中的中间结构(图1a中的40)的修改示例的分解透视图。

67.在修改示例中,参考图2,中间结构40a可以包括第二半导体芯片(图1a中的43)、半导体图案62a和绝缘间隙填充图案65a。半导体图案62a可以具有彼此平行的线条形状。第二半导体芯片43可以设置在半导体图案62a之间。绝缘间隙填充图案65a可以设置在半导体图案62a之间以围绕第二半导体芯片43的侧表面,并且可以设置在第二半导体芯片43的下表面和接合结构70之间以及在半导体图案62a的下表面和接合结构70之间。

68.接下来,将参考图3a描述中间结构40的另一个修改示例。图3a是示出图1b的截面图中的中间结构(图1b中的40)的修改示例的截面图。

69.在修改示例中,参考图3a,中间结构40b可以包括第二半导体芯片(图1a中的43)、半导体图案62b和绝缘间隙填充图案65b。绝缘间隙填充图案65b可以设置在第二半导体芯片43和半导体图案62b之间。半导体图案62b和绝缘间隙填充图案65b可以接触接合结构70。

70.接下来,将参考图3b描述中间结构40的另一个修改示例。图3b是示出图1b的截面图中的绝缘间隙填充图案65的修改示例的截面图。

71.在修改示例中,参考图3b,绝缘间隙填充图案65c还可以包括内部图案63。绝缘间隙填充图案65c的内部图案63可以设置在绝缘间隙填充图案65c的第一部分64a内,所述第一部分64a设置在半导体图案62和第二半导体芯片43之间。

72.在一个示例中,内部图案63可以是绝缘间隙填充图案65c的第一部分64a中的空隙或在空隙内。

73.在一个示例中,内部图案63从背面绝缘层87延伸到绝缘间隙填充图案65c的第一部分64a的内部(例如,内部部分),并且可以由与背面绝缘层87相同的材料形成。

74.接下来,将参考图3c描述中间结构40的另一个修改示例。图3c是示出图1b的截面图中的绝缘间隙填充图案65的修改示例的截面图。

75.在一个修改示例中,参考图3c,绝缘间隙填充图案65d可以包括第一部分64a和从第一部分64a延伸的第二部分64b

′

。绝缘间隙填充图案65d的第一部分64a可以设置在半导体图案62和第二半导体芯片43之间(例如,在水平方向上)。绝缘间隙填充图案65d的第二部

分64b

′

可以包括(例如,在竖直方向上)设置在半导体图案62和第一结构10之间的第一区域64b1以及(例如,在竖直方向上)设置在第二半导体芯片43和第一结构10之间的第二区域64b2。

76.接下来,将参考图4a和图4b描述在图1b和图1c中描述的贯通电极结构95的修改示例。图4a是示出图1b的截面图中的贯通电极结构95的修改示例的截面图,以及图4b是图4a中“a2”所表示部分的放大截面图,以说明图1c的局部放大视图中的贯通电极结构95的修改示例。

77.在一个修改示例中,参考图4a和图4b,堆叠芯片结构5a可以包括贯穿第二半导体芯片43的贯通电极结构95a。

78.每个贯通电极结构95a可以包括贯通电极94a和围绕贯通电极94a的侧表面的绝缘间隔物94b。贯通电极结构95a的贯通电极94a可以将接合结构70的中间连接布线72与背面导电图案89电连接。

79.接下来,将参考图5a和图5b描述图1b和图1c中描述的第一半导体芯片10、接合结构70和贯通电极结构95的修改示例。图5a是示出图1b的截面图的第一半导体芯片10、接合结构70、贯通电极结构95和背面结构85的修改示例的截面图,以及图5b是由“a3”表示的部分的放大图,并且是示出图1c的局部放大图中的第一半导体芯片10、接合结构70和贯通电极结构95的修改示例的截面图。

80.参考图5a和图5b,堆叠芯片结构5b可以包括通过使用电介质而接合的第一半导体芯片10a和接合结构70a。例如,第一半导体芯片10a的第一接合绝缘层29a和接合结构70a的第二接合绝缘层76a可以在彼此接触的同时接合。接合结构70可以包括设置在接合绝缘层76a和中间结构40之间的中间绝缘层74。

81.在一个示例中,第一接合绝缘层29a和第二接合绝缘层76a可以由绝缘材料形成,例如氧化硅,使得第一接合绝缘层29a和第二接合绝缘层76a可以在彼此接触的同时接合。如上所述,可以使第一接合绝缘层29a和第二接合绝缘层76a接触并接合的绝缘材料不限于氧化硅,而可以是其他绝缘材料。例如,第一接合绝缘层29a和第二接合绝缘层76a可以由sicn等形成。

82.堆叠芯片结构5b还可以包括输入/输出贯通电极结构95b和第一连接贯通电极结构96a,贯穿第二半导体芯片43和接合结构70a并延伸到第一半导体芯片10a中,以与第一半导体芯片10a的第一电路布线25电连接。堆叠芯片结构5b还可包括第二连接贯通电极结构96b,贯穿第二半导体芯片43的第二半导体衬底45并电连接至第二半导体芯片43的第二电路布线55。输入/输出贯通电极结构95b和第一连接贯通电极结构96a沿竖直方向具有实质上相同的长度,并且第二连接贯通电极结构96b沿竖直方向的长度可以小于第一连接贯通电极96a沿竖直方向的长度。输入/输出贯通电极结构95b、第一连接贯通电极结构96a和第二连接贯通电极结构96b中的每一个可以包括贯通电极94a和围绕贯通电极94a的侧表面的绝缘间隔物94b。

83.输入/输出贯通电极结构95b、第一连接贯通电极结构96a和第二连接贯通电极结构96b可以从贯穿第二半导体芯片43的部分延伸到背面结构85a中,并且可以贯穿背面结构85a的背面绝缘层87。

84.背面结构85a还可以包括可以电连接至输入/输出贯通电极结构95b的背面导电图

案89,以及将第一贯通电极结构96a和第二连接贯通电极结构96b电连接的连接导电图案89i。在背面导电图案89中,由封盖绝缘层91的开口91a暴露的区域可以是焊盘区域或输入/输出焊盘区域89p。连接导电图案89i的整个上表面可以被封盖绝缘层91覆盖。

85.再次,如参考图1a、图1b、图1c所述,贯通电极结构95可以与半导体图案62间隔开。然而本发明构思不限于此。在下文中,堆叠芯片结构还可以包括贯穿半导体图案62的外部贯通电极结构。在下文中,将描述还包括贯穿半导体图案62的外部贯通电极结构在内的堆叠芯片结构的示例。

86.参考图6和图7,将描述还包括贯穿半导体图案62的外部贯通电极结构在内的堆叠芯片结构的示例。图6是示出还包括贯穿半导体图案62的外部贯通电极结构在内的堆叠芯片结构的示例的平面图,并且图7是示出沿图6的线ii-ii’截取的区域的示意性截面图。

87.参照图6和图7,与图4a和图4b的堆叠芯片结构5a相比,堆叠芯片结构5a

′

还可以包括贯穿半导体图案62的外部贯通电极结构95a

′

。例如,外部贯通电极结构95a

′

可以由与图4a和图4b中的贯通电极结构95a实质上相同的材料形成,并且可以具有与贯通电极结构95a实质上相同的横截面结构面积。例如,图4a和图4b中的贯通电极结构95a贯穿第二半导体芯片43并向下延伸以延伸至接合结构70中,并且外贯通电极结构95a

′

可以贯穿半导体图案62并向下延伸以延伸至接合结构70中。

88.外部贯通电极结构95a

′

可以由与参考图4b描述的图4b的贯通电极结构95a实质上相同的材料形成,并且可以具有实质上相同的横截面结构面积。例如,外部贯通电极结构95a

′

和贯通电极结构95a可以电连接至背面导电图案89和中间连接布线72,类似于针对图4b中的贯通电极结构(参见图4b的95a)所描述的那样。

89.在一个示例中,贯通电极结构95a可以称作内部贯通电极结构。在另一示例中,在堆叠芯片结构5a

′

中,可以省略内部贯通电极结构95a。因此,堆叠芯片结构5a

′

可以包括外部贯通电极结构95a

′

。

90.接下来,参考图8,将描述还包括贯穿半导体图案62的外部贯通电极结构在内的堆叠芯片结构的示例。图8是示出沿图6的线ii-ii

′

截取的区域的示意性截面图。

91.在修改示例中,参考图8,除了图5a和图5b的堆叠芯片结构5b之外,堆叠芯片结构5b

′

还可以包括外部输入/输出贯通电极结构95b

′

。外部输入/输出贯通电极结构95b

′

可以贯穿半导体图案62和接合结构70a并延伸到第一半导体芯片10中。

92.外部输入/输出贯通电极结构95b

′

可以由与图5a和图5b中的输入/输出贯通电极结构95b实质上相同的材料形成,并且可以具有与输入/输出贯通电极结构95b实质上相同的横截面结构面积。例如,外部输入/输出贯通电极结构95b

′

和输入-输出贯通电极结构95a可以电连接第一半导体芯片10的背面导电图案89和第一电路布线25(参见图5b),类似于针对图5b中的输入/输出贯通电极结构(图5b的95b)所描述的那样。

93.在一个示例中,输入/输出贯通电极结构95b可以称作内部输入/输出贯通电极结构。在另一示例中,在堆叠芯片结构5b

′

中,可以省略内部输入/输出贯通电极结构95b。

94.接下来,分别参考图9和图10描述图1a至图8中的背面结构85的修改示例。图9是说明图4a中的背面结构85的修改示例的截面图,且图10是示出图9中的背面结构185的修改示例的截面图。

95.在修改示例中,参考图9,图1a至图8中描述的背面结构85中的至少一个可以用包

括第一背面器件183a在内的背面结构185代替。例如,图4a中的背面结构(图1b中的85)可以用包括第一背面器件183a在内的背面结构185代替。类似地,图1b、图2、图3a、图3b、图5a、图7和图8中的背面结构85和85a中的任何一个都可以用如图9中所示的包括第一背面器件183a在内的背面结构185代替。如上所述的背面结构185可以包括:第一背面器件183a,设置在第二半导体芯片43的第二半导体衬底45上;背面绝缘层187,在第一背面器件183a上和/或覆盖第一背面器件183a,背面绝缘层187在第二半导体芯片43和半导体图案62上;单层或多层背面导电图案189,设置在背面绝缘层187中;以及封盖绝缘层191,具有暴露背面导电图案189的焊盘区域189p的开口191a,封盖绝缘层191位于背面绝缘层187上。

96.第一背面器件183a可以与第二半导体芯片43竖直地交叠。背面导电图案189的一部分可以电连接至第一背面器件183a。应当理解的是,如本文所使用的“元件a与元件b竖直地交叠”(或类似语言)意味着存在与元件a和元件b两者都相交的至少一条竖直线。

97.贯通电极结构95a(如图4a所示的95a)可以电连接至背面导电图案189。因此,贯通电极结构95a中的至少一个可以将第一电路器件21和第二电路器件47的至少一个电连接至第一背面器件183a。诸如“至少其中之一”之类的表达在位于元件列表之前时修饰整个元件列表而不修饰该列表的单个元件。

98.在图9中,背面导电图案189示出为与图4a中的贯通电极结构95a电连接,但本发明构思不限于此。例如,如图4a所示的贯通电极结构95a可以用图5a和图5b所示的贯通电极结构95b、96a和96b、图7所示的贯通电极结构95a和95a

′

以及图8所示的贯通电极结构95b、95b

′

、96a、96b代替。因此,如图4a所示的贯通电极结构95a,如图1a和图1b所示的贯通电极结构95b、96a和96b,如图5a和图5b所示的贯通电极结构95b、96a和96b,如图7所示的贯通电极结构95a和95a

′

以及如图8所示的贯通电极结构95b、95b

′

、96a、96b可以电连接至如图9所示的背面导电图案189。

99.在修改示例中,参考图10,图9中所述的背面结构185还可以包括没置在半导体图案62上并被背面绝缘层187覆盖的第二背面器件183b。第二背面器件183b可以与半导体图案62交叠。

100.在一个示例中,第一背面器件(图9或图10中的183a)和第二背面器件183b中的至少一个可以包括有源器件、无源器件、图像传感器、光学连接单元、模拟器件和存储器件中的至少一个。例如,有源器件可以是晶体管,无源器件可以是电阻器、电容器或电感器。存储器件可以是易失性存储器件或非易失性存储器件。例如,存储器件可以是诸如mram的非易失性存储器件。

101.接下来,将参照图11a和图11b描述根据示例实施例的堆叠芯片结构。图11a是本发明构思的示例实施例的示意性平面图,以及图11b是沿图11a的线iii-iii

′

截取的示意性截面图。

102.参考图11a和图11b,根据示例实施例的半导体封装的堆叠芯片结构205可以包括第一结构210和第一结构210上的第二结构235。

103.第一结构210可以是第一半导体芯片。例如,第一结构210的第一半导体芯片可以包括第一半导体衬底213和第一半导体衬底213上的第一电路区216。第一电路区216可以包括第一半导体衬底213上的第一电路器件221以及可以电连接至第一电路器件221的第一接合焊盘231。

104.第二结构235可以包括中间结构240、在中间结构240和第一结构210之间的接合结构270以及在中间结构240上的背面结构285。中间结构240可以设置在背面结构285和接合结构270之间。

105.中间结构240包括在水平方向上彼此间隔开的多个半导体芯片243a和243b、围绕多个半导体芯片243a和243b的半导体图案262以及在多个半导体芯片243a和243b以及半导体图案262之间的绝缘间隙填充图案265。

106.多个半导体芯片243a和243b可以包括在第一结构(例如,第一半导体芯片210)上沿水平方向彼此间隔开的第二半导体芯片243a和第三半导体芯片243b。

107.多个半导体芯片243a和243b中的每一个可以包括第二半导体衬底245、第二电路区251和保护绝缘层259。第二电路区251可以设置在保护绝缘层259和第二半导体衬底245之间。第二电路区251可以包括第二电路器件247。保护绝缘层259可以接触接合结构270。

108.半导体图案262可以设置为围绕多个半导体芯片243a和243b中的每一个的侧表面。例如,半导体图案262可以包括:四边形环形部分262a和262b,四边形环形部分262a和262b的侧表面与第一结构210(例如,第一半导体芯片210)的侧表面对齐;以及中间部分262c,自环形部分262a和262b在多个半导体芯片243a和243b之间延伸。半导体图案262可以由硅材料形成。位于与多个半导体芯片243a和243b相同高度水平的半导体图案262的一部分可以不包括半导体集成电路。

109.在一个示例中,半导体图案262的厚度可以大于多个半导体芯片243a和243b的第二半导体衬底245的厚度。

110.绝缘间隙填充图案265可以包括诸如氧化硅的绝缘材料。绝缘间隙填充图案265包括设置在半导体图案262以及多个半导体芯片243a和243b之间的第一部分264a,以及设置在半导体图案262以及接合结构270之间的第二部分264b。

111.接合结构270可以包括绝缘层276、位于绝缘层276内的可以电连接至第二电路器件247的中间连接布线272以及位于绝缘层276中的可以电连接至中间连接布线272的第二接合焊盘278。第二接合焊盘278可以在接触第一结构210的第一接合焊盘231的同时进行接合。第一接合焊盘231和第二接合焊盘278可以包括相同的金属材料。例如,第一接合焊盘231和第二接合焊盘278可以包括铜材料。

112.第二结构235还可以包括贯通电极结构295a和295b。类似于图7,贯通电极结构295a和295b可以包括贯穿第二半导体芯片243a和第三半导体芯片243b并延伸到接合结构270中的第一贯通电极结构295a,以及贯穿半导体图案262并延伸到接合结构270中的第二贯通电极结构295b。

113.在一个示例中,在贯通电极结构295a和295b中可以省略第一贯通电极结构295a。在另一个示例中,在贯通电极结构295a和295b中可以省略第二贯通电极结构295b。在这种情况下,第一贯通电极结构295a可以与图1b和图1c的贯通电极结构95类似地形成。例如,第一贯通电极结构295a可以贯穿第二半导体芯片243a和第三半导体芯片243b的第二半导体衬底245并延伸到第二电路区251中。

114.背面结构285可以包括背面绝缘层287、背面绝缘层287上的背面导电图案289、以及背面导电图案289上的封盖绝缘层291,封盖绝缘层291具有暴露背面导电图案289的焊盘区域289p的开口291a。背面绝缘层287可以包括诸如氧化硅的绝缘材料。背面导电图案289

可以包括诸如铜或铝的金属材料。封盖绝缘层291可以包括诸如氮化硅或聚酰亚胺的材料。贯通电极结构295a和295b可以贯穿背面绝缘层287并且可以电连接至背面导电图案289。

115.在另一个示例中,背面结构285可以由包括如图9中的第一背面器件183a在内的背面结构(图9中的185)或者包括如图10中的第一背面器件183a和第二背面器件183b在内的背面结构(图10的185)代替。

116.接下来,将参考图12描述多个半导体芯片243a和243b的修改示例。图12是示出图11a的平面图中的多个半导体芯片243a和243b的尺寸的修改示例的平面图。

117.在修改示例中,参考图12,多个半导体芯片243a和243b

′

中的至少两个可以具有不同的尺寸。例如,多个半导体芯片243a和243b

′

可以包括第二半导体芯片243a和具有比第二半导体芯片243a更小的宽度或更小的平面尺寸的第三半导体芯片243b

′

。

118.围绕多个半导体芯片243a和243b

′

的半导体图案262

′

可以包括形成环形的环形部分262a

′

和262b

′

,以及自环形部分262a

′

和262b

′

在第二半导体芯片243a和第三半导体芯片243b’之间延伸的中间部分262c

′

。

119.接下来将参考图13说明图11b的第一结构210的修改示例。图13是示出图11b中的第一结构210的修改示例的截面图。

120.在修改示例中,参考图13,根据示例实施例的半导体封装的堆叠芯片结构305可以包括能够替代图11b中的第一结构210的第一结构310以及参考图11b描述的第二结构235。.

121.第一结构310可以包括多个下半导体芯片343a和343b、下半导体图案362、下绝缘间隙填充图案365和下接合结构370。

122.下半导体芯片343a和343b可以包括在水平方向上彼此间隔开的第一下半导体芯片343a和第二下半导体芯片343b。

123.下半导体图案362可以具有与相应的下半导体芯片343a和343b相邻和/或围绕相应的下半导体芯片343a和343b的形状。例如,下半导体图案362可以具有与第二结构235的半导体图案262相同或相似的形状。例如,下半导体图案362可以包括环形部分362a和362b以及自环形部分362a和362b在下半导体芯片343a和343b之间延伸的中间部分362c。

124.下绝缘间隙填充图案365可以包括(例如,在水平方向上)设置在下半导体图案362以及下半导体芯片343a和343b之间的第一部分364a以及(例如,在竖直方向上)设置在下半导体图案362和下接合结构370之间的第二部分364b。

125.下半导体芯片343a和343b中的每一个可以包括下半导体衬底345、下电路区351和下保护绝缘层359。下电路区351可以设置在保护绝缘层359和下半导体衬底345之间。在下半导体芯片343a和343b中的每一个中,下电路区351可以设置在下半导体衬底345和下接合结构370之间,并且可以包括下电路器件347。下保护绝缘层359可以接触下接合结构370。

126.第一结构310还可以包括在多个下半导体芯片343a和343b、下半导体图案362和下绝缘间隙填充图案365的下表面上和/或覆盖这些下表面的下绝缘层387。

127.下接合结构370可以包括下绝缘层376、可以电连接至下绝缘层376中的下电路器件347的下中间连接布线372、以及可以电连接至下绝缘层376中的下中间连接布线372的第一接合焊盘378。第一接合焊盘378可以在接触第二结构235的第二接合焊盘278的同时进行接合。

128.接下来,参考图14、图15和图16,将描述包括如上参照图1a至图13描述的堆叠芯片

结构5、5a、5b、5a

′

、5b

′

、205和305中的任一个在内的半导体封装的各种示例。图14、图15和图16是示出根据本发明构思的示例实施例的包括堆叠芯片结构在内的半导体封装的截面图。

129.首先,将参考图14描述包括如上参考图1a至图13描述的堆叠芯片结构5、5a、5b、5a

′

、5b

′

、205和305中的任一个在内的半导体封装的各种示例。

130.在一个例子中,参考图14,根据示例实施例的半导体封装件500a可以包括衬底400a以及安装在衬底400a上的如上参照图1a至图13描述的堆叠芯片结构5、5a、5b、5a

′

、5b

′

、205和305中的任何一个。例如,参考图4a和图4b描述的堆叠芯片结构5a可以安装在衬底400a上。

131.堆叠芯片结构5a的第二结构35可以面向衬底400a。

132.半导体封装500a还可以包括将衬底400a与芯片堆叠结构5a电连接的导电凸块450a、填充在衬底400a与堆叠芯片结构5a之间并围绕导电凸块450a的侧面的底部填充材料层460以及在衬底400a上的位于堆叠芯片结构5a上和/或覆盖堆叠芯片结构5a的模制层470。

133.在一个示例中,衬底400a可以是诸如印刷电路板之类的封装衬底。衬底400a不限于印刷电路板,并且可以是各种形式,例如诸如重分布衬底之类的封装衬底。例如,衬底400a可以包括封装体410a、设置在封装体410a的上部并电连接至导电凸块450a的上焊盘415a、设置在封装体410a下部的下焊盘420a、将封装体410a中的上焊盘415a和下焊盘420a电连接的内部布线425a、以及设置在下焊盘420a下方以与下焊盘420a接触的下焊球430a。

134.在一个示例中,模制层470可以包括环氧基模制树脂或聚酰亚胺基模制树脂。例如,模制层470可以包括环氧模制化合物(emc)或高k环氧模制化合物。

135.在另一个示例中,参考图15,根据示例实施例的半导体封装500b可以包括衬底400b以及通过引线接合安装到衬底400b上的如上参照图1a至图13描述的堆叠芯片结构5、5a、5b、5a

′

、5b

′

、205和305中的任一个。例如,参考图4a和图4b描述的堆叠芯片结构5a可以安装在衬底400b上,例如,封装衬底。

136.堆叠芯片结构5a的第一结构10可以面向衬底400b。

137.半导体封装500b还可以包括将衬底400b与堆叠芯片结构5a电连接的接合布线450b,以及位于衬底400b与堆叠芯片结构5a之间的粘合层460

′

,以及衬底400b上的位于堆叠芯片结构5a与接合布线450b上和/或覆盖堆叠芯片结构5a与接合布线450b的模制层470’。

138.在一个示例中,衬底400b可以是诸如印刷电路板或重分布板之类的封装衬底。例如,衬底400b可以包括封装体410b、设置在封装体410b的上部并电连接至接合布线450b的上焊盘415b、设置在封装体410b的下部的下焊盘420b、将封装体410b内部的上焊盘415b和下焊盘420b电连接的内部布线425b、以及设置在下焊盘420b下方以与下焊盘420b接触的下焊球430b。

139.在一个示例中,接合布线450b可以将堆叠芯片结构5a的第二结构35的焊盘区域89p和衬底400b的上焊盘415b电连接。

140.在另一个示例中,参考图16,根据示例实施例的半导体封装900可以包括封装衬底800、封装衬底800上的连接衬底700、设置在连接衬底700上的堆叠芯片结构600a、以及在连

接衬底700上的与堆叠芯片结构600a水平地间隔开的一个或多个半导体芯片结构600b和600c。堆叠芯片结构600a可以与如上参考图1a至图13描述的堆叠芯片结构5、5a、5b、5a

′

、5b

′

、205和305中的任一个相同或相似。

141.堆叠芯片结构600a可以包括彼此堆叠的第一结构10和第二结构35,并且第二结构35可以设置在第一结构10和连接衬底700之间。

142.半导体封装900还可以包括设置在封装衬底800和连接衬底700之间以将封装衬底800和连接衬底700电连接的中间连接导电凸块760、设置在连接衬底700和堆叠芯片结构600a之间以将连接衬底700与堆叠芯片结构600a电连接的第一连接导电凸块610a、以及设置在连接衬底700与一个或多个半导体芯片结构600b和600c之间以将所述连接衬底700与所述一个或多个半导体芯片结构600b和600c电连接的第二连接导电凸块610b与610c。

143.半导体封装900还可以包括:第一底部填充材料层615a,在连接衬底700与堆叠芯片结构600a之间并围绕第一连接导电凸块610a的侧表面;以及第二底部填充材料层615b和615c,在连接衬底700与所述一个或多个半导体芯片结构600b和600c之间并围绕第二连接导电凸块610b和610c的侧表面的。

144.封装衬底800可以包括封装体810、设置在封装体810的上部中并电连接至连接导电凸块760的上焊盘820、设置在封装体810的下部中的下焊盘830、将封装体810内的上焊盘820和下焊盘830电连接的内部布线835、以及设置在下焊盘830下方以接触下焊盘830的下焊球840。

145.连接衬底700可以是中介衬底或重分布衬底。中介衬底700可以包括半导体衬底710、通孔720、布线区730和钝化层750。

146.连接衬底700可以包括:下焊盘740,设置在连接衬底700的下表面上并与连接导电凸块760电连接且接触;以及上焊盘745,设置在连接衬底700的上表面上并与第一连接导电凸块和第二连接导电凸块610a、610b和610c电连接且接触。

147.半导体衬底710可以由诸如硅之类的半导体材料形成。

148.通孔720可以是在竖直方向上贯穿半导体衬底710的硅通孔(tsv)。例如,每个通孔720可以包括在竖直方向上贯穿半导体衬底710的导电通孔图案以及围绕导电通孔图案的侧表面的绝缘通孔间隔物。

149.布线区730可以设置在半导体衬底710上。布线区730可以包括绝缘层732和掩埋在绝缘层732中的连接线735a和735b。

150.在连接衬底700中,连接线735a和735b可以包括第一连接线735a和第二连接线735b。

151.第一连接线735a可以将一些上焊盘745电连接至通孔720。第二连接线735b可以将与堆叠芯片结构600a电连接的一些上焊盘745电连接至与一个或多个半导体芯片结构600b与600c电连接的一些上焊盘745,以将堆叠芯片结构600a电连接至一个或多个半导体芯片结构600b与600c。钝化层750可以设置在连接衬底700的底面或背面上。

152.在一个示例中,堆叠芯片结构600a可以包括如图1a至图13所述的多个半导体芯片,并且堆叠芯片结构600a的多个半导体芯片中的至少一个可以包括逻辑芯片,例如中央处理单元(cpu)、图形处理单元(gpu)、现场可编程门阵列(fpga)、数字信号处理器(dsp)、密码处理器、微处理器、微控制器、模数转换器或专用ic(asic)。例如,在堆叠芯片结构600a

中,第一结构10的第一半导体芯片可以是处理器芯片,而第二结构35的第二半导体芯片可以是模拟芯片。

153.在一个示例中,一个或多个半导体芯片结构600b和600c中的至少一个可以包括诸如动态ram(dram)或静态ram(sram)之类的易失性存储器件,诸如相变ram(相变ram)、磁性ram(mram)、电阻式ram(rram)或闪存设备之类的非易失性存储器件(pram),或诸如高带宽存储器(hbm)或混合存储立方体(hmc)的高性能存储设备。

154.接下来,将参照图17a至图19描述根据示例实施例的制造半导体封装的方法的示例。

155.参考图17a,可以形成第一半导体晶片9。形成第一半导体晶片9可以包括在第一半导体衬底13上形成包括第一电路器件21在内的第一电路区16,以及形成掩埋在第一电路区16的表面中的第一接合焊盘31。

156.参考图17b,可以形成多个半导体芯片43。形成多个半导体芯片43可以包括形成第二半导体晶片并通过执行锯切工艺将第二半导体晶片划分为多个半导体芯片43。形成第二半导体晶片可以包括在第二半导体衬底45上形成包括第二电路器件47在内的第二电路区51,以及在第二电路区51上形成保护绝缘层59以保护第二电路区51。因此,多个半导体芯片43的每一个可以包括第二半导体衬底45、第二电路区51和保护绝缘层59。

157.参考图18a,可以形成载体衬底60。形成载体衬底60可以包括准备半导体衬底并部分地蚀刻半导体衬底的表面以形成彼此间隔开的多个凹入区域60a。半导体衬底的围绕多个凹入区域60a的部分可以被定义为突出部61。载体衬底60可以是硅衬底。

158.参考图18b,多个半导体芯片43可以分别插入到载体衬底60的凹入区域60a中,并且绝缘间隙填充图案65可以被形成为填充在突出部61和多个半导体芯片43之间并位于多个半导体芯片43和突出部61上和/或覆盖多个半导体芯片43和突出部61。

159.在一个示例中,可以执行平坦化工艺以平坦化绝缘间隙填充图案65直到暴露多个半导体芯片43的上表面为止。在多个半导体芯片43中,保护绝缘层59可以保护第二电路区51免受平坦化工艺。平坦化工艺可以是化学机械抛光(cmp)工艺。

160.在一个示例中,在多个半导体芯片43的厚度大于凹入区60a的深度的情况下,绝缘间隙填充图案65的一部分可以保留在突出部61上。因此,绝缘间隙填充图案65可以包括:在突出部61和多个半导体芯片43之间的第一部分64a、以及在突出部61的上表面上和/或覆盖突出部61的上表面的第二部分64b。

161.随后,可以形成接合结构70。接合结构70可以包括电连接至多个半导体芯片43的第二电路区51的第二电路器件47的中间连接线72、覆盖中间连接布线72的绝缘层76、以及掩埋在绝缘层76中并具有与绝缘层76的上表面共面的上表面的第二接合焊盘78。

162.因此,可以形成包括载体衬底60、多个半导体芯片43、绝缘间隙填充图案65和接合结构70在内的第二半导体晶片34。

163.参考图18c,可以执行晶片接合工艺(wb)以将第一半导体晶片9和第二半导体晶片34接合从而形成初级接合晶片4。例如,通过晶片接合工艺(wb),第一半导体晶片9的第一接合焊盘31和第二半导体晶片34的第二接合焊盘78可以在彼此接触的同时接合。第一接合焊盘31和第二接合焊盘78可以由铜材料形成。因此,可以形成将第一半导体晶片9和第二半导体晶片34接合的初级接合晶片4。

164.参考图18d,可以执行减小初级接合晶片4厚度的厚度减小工艺以形成具有减小厚度的接合晶片4a。例如,可以通过研磨工艺或抛光工艺从初级接合晶片4去除其中设置有载体衬底60的部分,并且可以减小多个半导体芯片43的半导体衬底45的厚度,从而形成接合晶片4a。在这种情况下,载体衬底60的突起部得以保留,并且可以形成为半导体图案62。

165.半导体图案62的表面和多个半导体芯片43的半导体衬底45的表面可以形成共面表面。

166.参考图19,可以形成背面结构85和贯通电极结构95。例如,背面结构85和贯通电极结构95的形成可以包括:在接合晶片4a的半导体图案62的表面和多个半导体芯片43的半导体衬底45的表面上和/或覆盖上述表面形成背面绝缘层87,形成贯穿背面绝缘层87并延伸至接合晶片4a中的贯通电极结构95a,在背面绝缘层87上形成与贯通电极结构95a电连接的背面导电图案89,在背面绝缘层87上形成覆盖背面导电图案89的封盖绝缘层91,以及对封盖绝缘层91进行图案化以形成暴露背面导电图案89的焊盘区89p的开口91a。

167.随后,通过执行锯切工艺,对背面结构85和接合晶片4a进行切割以形成多个堆叠芯片结构5a。

168.根据示例实施例,可以提供一种包括半导体封装的电子装置或电子系统,所述半导体封装包括图1a至图13中描述的堆叠芯片结构中的任一个。

169.如上所述,根据本发明构思的示例实施例,通过形成多个半导体芯片,掩埋载体半导体晶片的多个半导体芯片,执行将其中掩埋多个半导体芯片的载体半导体晶片与通过单独半导体工艺形成的半导体晶片接合以形成一个接合晶片的晶片接合工艺,并执行用于切割所述接合晶片的锯切工艺,可以形成包括在竖直方向上堆叠的半导体芯片在内的堆叠芯片结构。在如上所述形成的堆叠芯片结构的情况下,可以减小尺寸或体积,同时堆叠芯片结构具有改善的可靠性。因此,可以减小其上安装有这种堆叠芯片结构的半导体封装的体积,并且还可以改善该半导体封装的可靠性。

170.尽管以上已经说明和描述了本发明构思的示例实施例,但是对于本领域技术人员来说显而易见的是在不脱离由所附权利要求限定的本发明构思的范围的情况下可以进行修改和变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。