1.本公开通常与使用多个通信电子芯片或小芯片的电子装置有关。

背景技术:

2.电子系统和电子装置在数据处理方面正变得更通用和高效以跟上对于数据的更快处理的不断增长的推动。一些数据处理系统可以包括电子装置,所述电子装置包括被通信耦合以执行数据处理任务的多个电子芯片和小芯片。数据处理任务中的多个芯片或小芯片可以是可编程逻辑器件、专用集成电路、处理器、收发器或者能够数字通信的任何其他电子电路部件。

3.前面提及的数字通信电路部件可以将不同的接口用于与其他电路部件的连接和通信。这样的数字通信电路部件可以使用具有用于数据的传输和接收的相应接口的互连方案的不同集合。各种互连方案的使用可以是由于由协议施加的、诸如除了别的以外还有不同的速率、电压电平、数据编码和解码方法以及物理布局的各种通信规则集导致的。然而,就具有不同通信能力的数字通信电路部件的接口而言,需要更多的通用性。例如,数字通信电路部件的不同芯片或小芯片可以使用不同数量的输入/输出(i/o)端口进行通信。

4.在具体数字部件(例如芯片或小芯片)中使用具体接口对于芯片或小芯片设计而言可能是最佳的。一些小芯片可以使用高数据带宽接口进行通信,而其他小芯片可以使用具有更低的数据带宽的接口进行通信。此外,按比例缩放的数据处理系统可以使用各种芯片或小芯片,所述各种芯片或小芯片各自使用不同数量的i/o端口。将高数据带宽通信接口用于这样的按比例缩放的数据处理系统的所有小芯片的数字通信可能是昂贵且低效的。例如,按比例缩放的数据处理系统可以包括具有高带宽的一个小芯片,而其他通信的小芯片包括具有更低的数据带宽的电路系统。

5.这部分是用来向读者介绍可与下面描述和/或请求保护的本公开的各个方面有关的技术的各个方面。相信这个讨论有助于向读者提供背景信息以促进对本公开的各个方面的更好理解。因此,应当理解,要就此而论来阅读这些陈述,而不是要作为对现有技术的承认来阅读这些陈述。

附图说明

6.在阅读下面详细的描述并且在参考附图时,公开的优势可变得明显,其中:图1描绘了根据实施例的具有高级接口总线2.0(aib 2.0)或高级接口总线-o(aib-o)的小芯片;图2描绘了根据实施例的aib 2.0方案和aib-o方案的输入/输出(i/o);图3描绘了根据实施例的图1的aib 2.0和aib-o的透视图;图4描绘了根据实施例的使用aib-o方案和aib 2.0方案接口通信耦合的第一和第二小芯片;图5描绘了根据实施例的使用aib-o方案接口通信耦合的第一和第二小芯片;以及

图6描绘了根据实施例的耦合在图1的封装的小芯片之间的传送器电路系统和接收器电路系统。

具体实施方式

7.下面将描述一个或多个具体实施例。在努力提供这些实施例的简明描述的过程中,并非所有的实际实现的特征都在说明书中被描述。可以意识到,在任何这样的实际实现的开发中,如在任何工程或者设计项目中那样,必须做出许多特定于实现的决策以实现诸如遵守系统相关的约束和商业相关的约束的、可从一个实现到另一实现变化的开发者的具体目标。此外,可以意识到,这样的开发努力可能是复杂且耗时的,但是对于受益于本公开的普通技术人员而言将仍然是设计、制作和制造的例行工作。

8.当介绍本公开的各种实施例的元件时,冠词“a”、“an”和“所述”是用来指存在有元件当中的一个或多个元件的。术语“包括”、“包含”和“具有”规定为是包括的并且指可能存在有除列示的元件之外的附加元件。另外,应当理解,提及本公开的“一个实施例”或者“实施例”意图不是被解释为排除也结合了所记载的特征的附加实施例的存在。此外,短语a“基于”b是用来指a至少部分基于b的。

9.下面阐述了与最初请求保护的公开在范围上相当的某些方面。应当理解,呈现这些方面仅仅用来向读者提供公开可能采取的某些形式的简要概述,并且这些方面不是用来限制公开的范围的。确实,公开可以包括可能没有在下面阐述的各种各样的方面。

10.描述了用于缩放管芯到管芯通信的方法和系统。数据处理系统可受益于来自小芯片接口的附加通用性以促进具有不同带宽能力的小芯片之间的通信。例如,备选的接口可以与具有多个不同数据带宽的通信小芯片一起被使用来促进与其他小芯片的通信。下面描述了不同的实施例以促进具有不同数据带宽的小芯片之间的有效通信。小芯片可以至少包括管芯、接口层和封装。接口层可以促进管芯和其他小芯片或芯片之间的数字通信。可以使用物理层来实现接口层以提供高数据带宽,或者可以使用不同的物理层来实现接口层以提供更低的数据带宽。物理层的数据带宽密度可取决于物理层内的导电迹线的数量和接近度。处理系统中的小芯片的应用(例如基于小芯片或芯片的系统内的其他管芯的通信能力)可以施加对于接口层的数据带宽要求。像这样,可以将管芯与接口层一起封装,所述接口层包括高密度物理层以提供高数据带宽或者包括低密度物理层以提供更低的数据带宽。

11.将相同管芯与具有不同数据带宽的不同接口层一起封装可以促进通用且可缩放的处理系统设计。然而,这样的接口层可以使用相同的通信协议。也就是,与具有不同数据带宽的这样的接口层的物理层相关联的互连方案可以促进利用类似协议的数据通信。

12.即便如此,芯片或小芯片的系统可以包括多个标准化的小芯片接口以促进可缩放系统设计。例如,处理系统可以使用高数据带宽密度接口技术(例如嵌入式多管芯互连桥接器(emib))连同低数据带宽密度接口技术。像这样,在使用相同通信协议的同时,可以使用具有高数据带宽和更低的数据带宽的不同的接口层来降低系统设计的复杂度。描述了用于将管芯到管芯接口缩放用于高互连密度emib/内插器到低互连密度封装迹线的方法和系统。

13.可以出于各种各样的目的来使用用于实现具有有机衬底的高数据带宽密度小芯片的辅助封装技术。一些小芯片接口可以针对高级封装。例如,在不同的实施例中,连同其

他小芯片接口技术一道,小芯片可以使用嵌入式多管芯互连桥接器(emib)、硅内插器或者有源内插器。然而,这样的高级封装技术可能具有用于提供高功能性的更多的相关成本,对于一些应用而言可能不需要所述高功能性/所述高功能性可能不可用于一些应用。例如,除了别的以外还有一些模数转换器(adc)、数模转换器(dac)以及收发器可能仅需要由具有这样的高级封装技术的小芯片接口提供的数据带宽密度的一小部分。

14.可缩放封装技术可以用来提供与不同小芯片或芯片应用中的设计要求相当的足够的功能性。这样的可缩放封装技术可以在为系统设计实现保留小芯片的功能性并且提供有成本效益的解决方案的同时提供小芯片的系统之间的有成本效益的通信解决方案。

15.如将会意识到的,不同的小芯片接口(或互连)层可以使用不同的制造过程和/或不同的材料。接口层可以包括再分布层(rdl)、多个凸块和衬底,所述衬底包括导电迹线以使能与其他小芯片或芯片的外部通信。像这样,与相应的小芯片、芯片或芯片的系统的实现相关联的成本可以基于与小芯片一起使用来促进数据通信的接口层而变化。例如,一些小芯片可以使用在由有机材料构成的衬底上实现的高级接口总线1.0(aib 1.0)互连。衬底内的迹线的相对小的密集度以及在接口层的凸块和rdl上实现的相对小的带宽密度规定了将有机材料与aib 1.0一起使用。此外,aib 1.0可以使用第一通信协议来促进通信。

16.在另一方面,利用相应接口层中聚集的rdl和凸块(高密度)以及相应衬底内高度聚集的迹线,高级接口总线2.0(aib 2.0)可以包括高数据带宽。然而,高度聚集的接口层使用rdl内更密集且更细的连接、更细的凸块大小以及更复杂的衬底材料来促进更细的接口以及与其他小芯片的互连。像这样,可以使用诸如硅的更昂贵的衬底或凸块材料来实现aib 2.0。此外,aib 2.0可以使用与第一通信协议不同的第二通信协议来促进通信。

17.一些高级小芯片可以与通信系统内的具有高数据带宽的其他高级小芯片通信。这样的通信系统可以受益于使用高级接口总线2.0(aib 2.0)互连技术。然而,一些其他通信系统可以使用高级小芯片通信(使用aib 2.0)与具有更低的数据带宽密度的另一小芯片(使用aib 1.0)之间的通信。由于由aib 1.0和aib 2.0使用不同的通信协议导致这样的通信可能是不可行的。aib 2.0可以促进高级小芯片和另一小芯片之间的通信。然而,将aib 2.0用于能够充分使用更低带宽接口执行的小芯片由于使用更昂贵的衬底(例如硅)结合的高密度接口而增加了系统的成本。

18.在下文中描述了aib-o,所述aib-o用于使用可与aib 2.0协议一起使用(并且类似于aib 2.0协议)的通信协议来促进通信,同时在小芯片的接口层(包括rdl和凸块)中包括密度更小的导体并且在衬底中包括更小的密度。aib-o可以将有机材料用于接口层和衬底以降低成本来促进高级小芯片和另一小芯片(具有更小的数据带宽)之间的通信。在类似的覆盖区(footprints)上使用类似的通信协议(例如互连方案)的同时,aib-o可以包括与aib 2.0一起使用的凸块的一小部分。

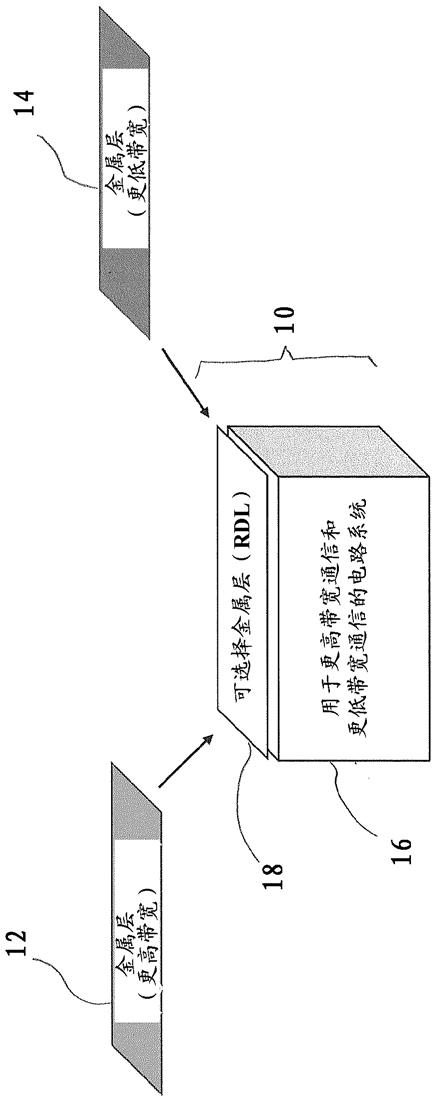

19.现在参考图1,小芯片10可以包括aib 2.0层12或aib-o层14。尽管下面讨论了aib 2.0和aib-o,但是类似的技术可应用于类似的高密度和低密度协议和/或层。如将会意识到的,在制造小芯片10时,将aib 2.0层12或aib-o层14与小芯片10结合可以是可选择的。小芯片10可以包括相应的管芯16。管芯16可以包括诸如逻辑层或晶体管层的处理元件的多个层并且可以使用不同的数据带宽进行通信。例如,管芯16可以是促进除了别的以外还有现场可编程门阵列(fpga)、数字信号处理器(dsp)、专用集成电路(asic)、硬逻辑、软逻辑。然而,

管芯16可以经由被结合在可选择层18上的、诸如aib 2.0层12或aib-o层14的接口层与一个或多个其他小芯片通信。

20.小芯片10可以使用可结合接口层的可选择层18与其他管芯、小芯片或芯片通信。在一些实施例中,可选择层18可以包括小芯片10的一个或多个顶部金属层以促进管芯16和外部电路系统之间的互连方案。像这样,小芯片10可以包括与可选择层18一起封装的管芯16以使用数据通信协议来提供数据通信。数据通信协议可以包括具体的数据速率、频率、带宽密度等。在不同的实施例中,可以使用不同的材料(例如硅、有机材料)来制造可选择层18以促进使用相应的接口层(例如aib 2.0层12或aib-o层14)与另一管芯的数据通信。

21.可选择层18可包括除了别的以外还有rdl层和凸块。rdl层和凸块可以促进经由衬底的、管芯16和其他小芯片之间的数据通信。在具体实施例中,为了促进与其他小芯片的数字通信,当小芯片10正在使用aib 2.0层12或aib-o层14时,管芯16可以使用相同的通信协议。此外,因为aib 2.0层12或aib-o层14可以使用相同的通信协议来促进通信,所以管芯16可以利用aib 2.0方案或aib-o方案与其他小芯片通信。

22.与使用相同覆盖区的aib 2.0层12相比,在使用相同通信协议的同时,aib-o层14可以包括数据带宽的一小部分(例如1/2、1/3、1/4等)。例如,管芯16可以被通信耦合至具有高数据带宽的另一小芯片。像这样,可以使用aib 2.0层12来实现管芯16以促进高数据带宽。然而,在另一示例中,管芯16可以被通信耦合至具有相对更低的数据带宽密度的不同小芯片。像这样,可以使用aib-o层14来实现管芯16以促进相对更低的数据带宽。在两个示例中,管芯16可以使用相同的通信协议与其他小芯片通信。在具体实施例中,aib-o层14可以包括在相同覆盖区(例如可选择金属层18)上与aib 2.0方案一起使用的凸块的一小部分(例如1/2、1/3、1/4等)。像这样,aib-o层14的物理层的带宽密度(包括rdl和凸块)可以是aib 2.0层12的物理层的带宽密度的一小部分。在其他实施例中,aib-o层14可以被参数化,并且与aib 2.0层12相比,制造商可以使用不同的比率(例如8:1、4:1、2:1和1:1)来为小芯片10提供aib-o层14。

23.然而,当使用aib 2.0层12或aib-o层14时,可选择层18可以包括不同的物理性质。也就是,因为与相同覆盖区上的aib 2.0层12相比,aib-o层14包括凸块的一小部分,所以可以使用更多种类的材料来制造与aib-o层14结合的小芯片10。例如,aib-o层14可包括用于rdl层和凸块的有机材料,而aib 2.0层12可包括具有rdl层和凸块的硅以结合具有更精细设计和实现的高密度层。应当意识到,在具体实施例中,管芯16可使用aib 2.0层12、aib-o层14或者相同覆盖区(例如可选择金属层18)的不同部分(例如不同的i/o组)上的两个接口层的组合来进行通信以促进数据通信。

24.在第一实施例中,小芯片10可以将管芯16与aib 2.0层12一起使用来与具有高数据带宽(例如256 gbps)的一个或多个其他小芯片通信。aib 2.0层12可以使用包括物理层中的高数据带宽密度的高级电路系统材料来促进这样的数据通信。例如,aib 2.0层12可以使用利用硅衬底材料实现的微凸块(μbump)。在具体实施例中,微凸块可以将45毫米(mm)或另一测量用于间距大小。此外,微凸块或硅衬底可增加与小芯片10相关联的制造成本。然而,在受益于与管芯16相关联的其他功能性的同时,管芯16的一些应用可以具有带更低的数据带宽密度的足够带宽。例如,小芯片10可以与具有比aib 2.0规范低的数据带宽密度能力的一个或多个其他小芯片通信。

25.在第二实施例中,小芯片10可以将管芯16与aib-o层14一起使用来使用更低的数据带宽(例如56 gbps)与一个或多个其他小芯片通信。第二实施例可以被用在与第一实施例不同的应用中。具体地,当具有更低的数据带宽能力的通信足以与一个或多个其他小芯片通信时,可以使用第二实施例。aib-o层14可以在相应的物理层中使用更低的数据带宽密度来提供小芯片10(例如高成本的管芯或小芯片)和在物理层(例如edl层和凸块)中使用更低的数据带宽密度的更低成本的管芯或小芯片之间的接口。

26.如前面所注意到的,与aib 2.0层相比,在保留管芯16的其他功能性(例如相同的通信协议)的同时,aib-o层14可以提供的数据通信带宽的一小部分。与aib 2.0层12相比,aib-o层14还可以包括在小芯片10的顶层中使用的一小部分数量的凸块。在具体实施例中,aib-o层14可以使用c4凸块来促进数据通信,并且aib 2.0层12可以使用微凸块来促进数据通信。与微凸块相比,c4凸块可以更宽并且可以在小芯片10的顶层上占据更多的空间。与微凸块相比,用于管芯到管芯通信接口的c4凸块的实现可以允许将更多种类的材料用于制造凸块。例如,管芯可以使用aib-o层14来通过有机材料衬底与其他管芯通信。像这样,aib-o层14可以提供与使用更低的数据通信带宽密度的其他小芯片的可缩放的通信,同时保留管芯16的其他功能性(例如频率、数据速率等)。

27.aib-o层14与管芯16的一起使用可以降低相关联的制造成本,同时通过减少每单位周长的边缘数据带宽来使能可缩放的设计。像这样,aib-o层14和aib 2.0层12可以通过解释用于管芯到管芯通信的数据带宽密度和通过使用相同管芯16来提供不同的小芯片的实现成本之间的权衡来促进可缩放的系统设计。

28.在一些实施例中,可以使用aib-o层14来实现fpga。取决于应用和应用的带宽密度,可以通过使用相同的fpga来用aib-o 14代替aib 2.0层12来降低系统实现的成本。也就是,可以使用具有aib-o层14的第一金属层或者使用使用了aib 2.0层12的第二金属层(使用不同的封装技术)来实现fpga。结果,可以使用相同管芯来制造两个不同版本的fpga。在其他实施例中,asic或其他处理块可以使用aib-o层14。

29.考虑到前述的内容,图2描绘了与aib 2.0层12相关联的i/o端口20和与aib-o层14相关联的i/o端口22。诸如片上系统的处理系统或者其他计算部件可以包括小芯片10。小芯片10的第一实施例可以使用具有aib 2.0 i/o端口20的aib 2.0层12,并且小芯片10的第二实施例可以使用具有aib-o i/o端口22的aib-o层14。就小芯片10而言,第一实施例和第二实施例可以使用相同的管芯(例如图1的管芯16)。像这样,可以使用相同覆盖区(小芯片10的顶部金属层)上的包括aib 2.0 i/o端口20的aib 2.0层12或者包括aib-o i/o端口22的aib-o层14来实现接口层(图1的可选择层18)。在具体示例中,可使用微凸块来实现aib 2.0 i/o端口20,并且可使用c4凸块来实现aib-o i/o端口22。

30.在图2中,如将会意识到的,aib-o i/o端口22可在相同覆盖区上包括如aib 2.0 i/o端口20的i/o的数量的一小部分。例如,可以使用更细的间距大小来实现微凸块,而可以使用更宽的间距大小来实现c4凸块。像这样,与aib-o i/o端口22相关联的更小数量的i/o端口可以促进小芯片10上的(每周长)更低的数据带宽密度。例如,与包括aib 2.0 i/o端口20(使用微凸块)的aib 2.0方案相比,包括aib-o i/o端口22(使用c4凸块)的aib-o方案可以促进使用数据带宽的一小部分的数据通信,同时促进管芯(例如图1的管芯16)与使用和aib 2.0方案相同的通信协议的其他小芯片的通信。像这样,虽然aib-o方案可以包括具有

更低的带宽密度的物理层(包括aib-o i/o端口22),但是管芯和其他小芯片(使用aib 2.0方案或aib-o方案)之间的接口可以保持一致。

31.在关于图2的具体实施例中,与aib 2.0 i/o端口20相比,aib-o i/o端口22可包括四分之一数量的i/o端口。例如,每个c4凸块(被用来促进aib-o i/o端口22)可以更宽,并且与微凸块(被用来促进aib 2.0 i/o端口20)相比,每个c4凸块可以占据更多的空间。在这些实施例中,可以在管芯和其他通信小芯片之间使用/分配更少的数据通信路由。例如,aib-o层14可以使用具有aib-o i/o端口22的具体rdl,所述具体rdl将管芯i/o重新连接到小芯片10的c4凸块以促进数据通信。此外,一致的通信协议可以促进使用小芯片10的管芯并且使用使用了具有aib 2.0方案的aib 2.0 i/o端口20或者具有aib-o方案的aib-o i/o端口22的其他小芯片来促进小芯片的系统中的可缩放的设计的数据传输和接收。

32.如上面所描述的,aib-o i/o端口22可以使用小芯片10(和相应的管芯)的全带宽密度的一小部分来促进数据通信。在具体实施例中,aib-o i/o端口22可以促进使用小芯片10的全带宽密度的一小部分来将设计可缩放性提供给使用小芯片10的系统设计。例如,管芯可以与需要管芯的全带宽密度的一小部分的一个或多个其他小芯片通信。此外,可以仅使用小芯片10的一个或多个通道来实现这样的通信。与aib-o层14相关联的小芯片10的rdl层可以促进管芯和aib-o i/o端口22之间的通信的路由选择。

33.aib 2.0 i/o端口20可以包括除了别的以外还有功率i/o部分24a、功率i/o部分24b和通信i/o部分26。功率i/o部分24a和功率i/o部分24b可以包括具有用于小芯片10的输入功率引脚或输出功率引脚的i/o端口。通信i/o部分26可以包括用于经由小芯片10的管芯的数据通信的i/o端口。在一些实施例中,功率i/o部分24a、功率i/o部分24b和通信i/o部分26可以是用户可配置的。此外,在不同的实施例中,aib 2.0 i/o 20可以包括不同的i/o部分或i/o部分的组合。

34.aib-o i/o端口22可以包括功率i/o部分28a、功率i/o部分28b和通信i/o部分30。功率i/o部分28a和功率i/o部分28b可以与小芯片10的输入功率引脚或输出功率引脚相关联。通信i/o部分26可以包括用于经由小芯片10的管芯的数据通信的i/o端口。在一些实施例中,功率i/o部分28a、功率i/o部分28b和通信i/o部分30可以是用户可配置的。此外,在不同的实施例中,aib-o i/o端口22可以包括不同的i/o部分或i/o部分的组合。

35.如图2所描绘的并且如上面所描述的,与aib 2.0 i/o端口20相比,包括功率i/o 28a、功率i/o 28b和通信i/o 30的aib-o i/o端口22可以包括i/o端口的数量的一小部分。可以使用诸如有机材料的更多种类的制造材料来实现aib-o层14。像这样,aib-o层14可以促进用于使用aib-o i/o端口22(利用aib-o方案)或者aib 2.0 i/o端口20(利用aib 2.0方案)与其他小芯片通信的可缩放且有成本效益的系统设计。

36.现在参考图3,在透视图中将与aib 2.0层12和aib-o层14相关联的i/o引脚叠加在小芯片10的顶部金属层上以用于比较。如上面所提及的,在不同的实施例中,小芯片10的诸如图1的管芯16的管芯的一个或多个顶部层可以将一种或其他的接口总线技术(aib 2.0或aib-o)用于与其他管芯的数据通信。图3的叠加透视图提供了aib 2.0层12和aib-o层14的相应i/o引脚之间的说明性比较。应当注意到,图3可以仅描绘小芯片10的一部分。

37.在图3中,使用微凸块来实现与aib 2.0层12相关联的多个i/o引脚并且使用c4凸块来实现与aib-o层14相关联的其他i/o引脚。在一些实施例中,微凸块可使用具有更窄的

间距(例如45毫米)的间距凸块,而c4凸块可使用相对更宽的间距凸块。像这样,可设置在aib-o层12上的c4凸块的数量可以是可设置在aib 2.0层12上的微凸块的一小部分。在具体实施例中,可以使用硅衬底来实现微凸块以用于在更复杂的设计中实现高数据带宽密度。可以使用具有更多种类的衬底材料的、在更低的数据带宽是足够的时候可使能在应用中使用管芯的衬底来实现c4凸块。例如,由于在物理层中使用的更小的带宽密度,可使用有机材料实现c4凸块。如上面所描述的,微凸块可以与aib 2.0层相关联,并且可以与emib技术一起使用微凸块,而c4凸块可以被用来利用aib-o方案来实现aib-o层14。

38.每个描绘的i/o组可以包括多个i/o引脚以促进小芯片10和其他小芯片之间的数据通信。在一些实施例中,每个i/o组可以与在制造时确定的管芯的一个或多个功能块相关联。备选地,i/o组在制造过程之后可以是用户可配置的。然而,在不同的实施例中,每个i/o组可以与多个微凸块或c4凸块相关联。如上面所描述的并且如图3的实施例中所描绘的,当将微凸块与aib 2.0层12一起使用时,每个i/o组可以使用第一数量的引脚,或者当将c4凸块与aib-o层14一起使用时,每个i/o组可以使用第一数量的引脚的一小部分。凸块的不同数量部分地是由于与不同的凸块技术一起使用的不同的间距大小导致的。像这样,当与c4凸块相比而使用微凸块(aib 2.0层12和aib-o层14)时,每个i/o组可以使用具有更高的数据带宽密度的物理接口层进行通信。

39.应当注意到,微凸块和c4凸块的使用是关于具体实施例的,并且其他实施例可以将其他凸块与小芯片10一起使用。例如,在aib-o方案中,与aib 2.0方案相比,小芯片10可以使用凸块(或i/o引脚)的一小部分(例如四分之一),这允许aib-o层14由于更低的设计限制而使用各种凸块技术。也就是,aib-o层14不限于c4凸块。

40.此外,小芯片10的顶部金属层可以包括用于将i/o引脚路由到管芯上的相应端口的一个或多个层或子层。例如,当使用aib 2.0层12时,小芯片10可以包括用于将微凸块引导至管芯的相应部分/端口的rdl。类似地,当使用aib-o层14时,小芯片10可以包括用于将c4凸块连接到管芯的相应部分的另一rdl。

41.考虑到前述的内容,在一些实施例中,与aib 2.0层12的rdl类似,aib-o层14可以在小芯片10的顶部金属层上使用rdl。在这样的实施例中,因为与aib 2.0层12相比,aib-o层14可以使用凸块的一小部分,所以可以不使用管芯的一个或多个i/o引脚。在其他实施例中,与aib-o层14相关联的rdl可以包括用于使aib-o层14凸块与管芯i/o端口兼容的不同的路由选择电路系统。像这样,与aib-o层14相关联的rdl可以通过不使用多个管芯i/o端口或重新布线管芯i/o端口来促进相同覆盖区上的管芯16的减小的数据带宽密度。

42.制造商可以使用aib 2.0层12、aib-o层14或者两者的组合(例如在不同的i/o组上)来实现小芯片10的顶部层。在一些实施例中,小芯片10可以包括封装的不同通道或者不同侧上的不同接口。在一些其他实施例中,第一小芯片可以包括使用aib 2.0层12的一个或多个接口,并且第二小芯片可以包括使用aib-o层14的一个或多个接口。管芯可以将aib 2.0层12用于与使用高数据带宽的高级小芯片通信或者将aib-o层14用于与具有更低的数据带宽的小芯片通信。在任一实施例中,管芯可以包括被连接到aib 2.0层12或aib-o层14的相同处理电路系统(例如逻辑电路系统、晶体管层等)。当管芯在使用与aib 2.0方案相同的协议的同时与具有更低的数据带宽的其他管芯通信时,由aib-o层14实现的aib-o方案可以促进类似的功能性和减小的数据带宽密度。像这样,系统设计可受益于使用aib-o层14和

aib 2.0层12的可缩放的设计。

43.图4描绘了示例通信系统40。通信系统40可以包括第一小芯片42和第二小芯片44。可以经由衬底46通信耦合第一小芯片42和第二小芯片44。第一小芯片42和第二小芯片44可以各自包括fpga、专用集成电路(asic)等中的一个。第一小芯片42可以使用aib 2.0层12通信耦合至衬底46,并且第二小芯片44可以使用aib-o层14通信耦合至衬底46。

44.与第一芯片42相关联的aib 2.0层12可以包括通道48。通道48a至48g可以各自作为传送器或接收器通道进行通信。例如,通道48a、48c、48e和48g可以被配置成将通信数据传送到第二小芯片44,而通道48b、48d和48f可以被配置成从第二小芯片44接收通信数据。

45.类似地,与第二芯片44相关联的aib-o层14可以包括通道50。通道50a至50g可以各自作为传送器或接收器通道进行通信。例如,通道50a、50c、50e和50g可以被配置成将通信数据传送到第一小芯片42,而通道50b、50d和50f可以被配置成从第一小芯片42接收通信数据。应当注意到,在其他实施例中,第一小芯片42和第二小芯片44可以包括不同数量的通道并且可以使用通道的不同配置(例如传送器通道和接收器通道)进行通信。

46.在一些实施例中,与第一小芯片42相关联的边带52以及与第二小芯片44相关联的边带54可以包括通道配置数据。例如,边带52可以存储与通道48的架构相关联的配置数据,并且边带54可以存储与通道50的架构相关联的配置数据。边带52和边带54可以传送相应的配置数据,以配置相应的aib 2.0层12和aib-o层14,从而促进相应的i/o引脚的分配。

47.aib 2.0层12可以包括与通道50a至50g相关联的物理层上的高数据带宽密度。aib 2.0层12可以包括微凸块。aib-o层14可以包括与通道50a至50g相关联的物理层上的更小的数据带宽密度。aib-o层14可以包括c4凸块。如前面所注意到的,与aib-o层14相关联的c4凸块可以是与aib 2.0凸块相关联的微凸块的一小部分。然而,在没有aib 2.0层12和aib-o层14之间的转换电路系统的情况下,第一小芯片42和第二小芯片44可以使用相同的通信协议进行通信。像这样,第一小芯片40和第二小芯片42可以使用相同的计时、初始化、自调谐和边带架构进行通信,所述边带架构将会跨变化的数据宽度进行缩放以促进跨多种物理技术使用相同的生态系统。

48.与aib 2.0层相比,aib-o层14可具有不同的物理特性。由于更小数量的凸块,第二小芯片44可以将更小的带宽密度用于相应的接口层。此外,衬底46可以包括具有更小的物理密度的更小数量的迹线。例如,aib-o层14的更小数量的凸块可以限制用于第一小芯片42和第二小芯片44之间的数据通信的衬底46内的迹线的数量以及迹线的密度和密集度。像这样,可以将更多种类的制造材料(例如有成本效益的材料)用于衬底46。然而,这个aib-o层14可使用类似的计时、初始化、自调谐和边带架构进行通信。像这样,aib-o层12可以跨具有不同数据宽度的不同小芯片进行缩放以促进跨具有不同带宽密度的多种物理技术的小芯片的生态系统。

49.现在参考图5,第一小芯片62和第二小芯片64可以使用通信系统60中的aib-o层14进行通信。在不同的实施例中,第一小芯片62或第二小芯片64可以是fpga、asic或其他处理部件。与图4的衬底46类似,衬底66可以促进第一小芯片62和第二小芯片64之间的通信。例如,第一小芯片62和第二小芯片64可以各自包括多个(例如22个)c4凸块(图5中未示出)从而以对应的速率(例如4 gbps)传递数据。

50.在所描绘的实施例中,第一小芯片62可以包括通信通道68,所述通信通道68包括

传输通道68a和接收器通道68b。通信通道68可以使用aib-o层14提供数据以用于传输。aib-o层14可以在第一小芯片62和第二小芯片64当中的每一个中使用aib-o方案来促进数据通信。关于图5的通信系统描述了与aib-o层14相关联的电路系统的示例实施例。

51.aib-o层14中的每一个可以包括aib-o i/o块70和aib-o物理层72。aib-o i/o块70可以包括如关于图3描述的c4凸块或者其他可行的凸块技术。aib-o i/o块70可包括对于关于图2所描述的aib-o i/o端口22的凸块架构。aib-o物理层72可与rdl相关联并且提供了处理和路由选择电路系统以促进数据通信。在一个实施例中,aib-o物理层72可以使用本文中以及关于图5所描述的功能块来促进数据通信。

52.aib-o物理层72可以包括配置数据74、数据路径块76、先进先出寄存器(fifo)78、时钟80和复位82。然而,应当意识到,在不同的实施例中,aib-o物理层72可以包括不同的电路系统和电路块。配置数据74可以包括指示aib-o物理层72的架构的数据。例如,诸如图4的边带54的边带可以提供配置数据74。数据路径块76可以包括fifo 78、时钟80和复位82以促进在通信通道68和aib-o i/o块70之间的数据的路由选择。在一些实施例中,相应的rdl层可以结合数据路径块76。在不同的实施例中,fifo 78可以接收和传送数据以用于传输或接收。时钟80可促进fifo 78可传送数据的速率。复位82可以被控制信号触发以重新配置数据路径块76。例如,配置数据74可以提供这样的触发信号。

53.如图6所示,数据处理系统90可以包括结合了本文中讨论的灵活的接口技术的一个或多个可编程逻辑器件92。数据处理系统90包括处理器98、存储器和/或存储电路系统96以及网络接口94。数据处理系统90可以呈现可以利用aib-o方案(即aib-o层14)的实施例。数据处理系统90可以包括更多或更少的部件(例如电子显示器、用户接口结构、专用集成电路(asic))。处理器98可以包括诸如intel

®ꢀ

xeon

®

处理器或精简指令处理器(例如精简指令集计算机(risc)、高级risc机器(arm)处理器)的、可以管理对数据处理系统90的数据处理请求(例如,以执行机器学习、视频处理、语音识别、图像识别、数据压缩、数据库搜索排名、生物信息学、网络安全模式识别、空间导航等等)的任何合适的处理器。存储器和/或存储电路系统96可以包括随机存取存储器(ram)、只读存储器(rom)、一个或多个硬盘驱动器、闪速存储器等等。存储器和/或存储电路系统96可以被认为是可编程逻辑器件92的外部存储器并且可以保存要被数据处理系统90处理的数据。在一些情况下,存储器和/或存储电路系统96还可以存储用于给可编程逻辑器件92编程的配置程序(例如比特流)。网络接口94可以使得数据处理系统90能够与其他电子装置通信并且可以通过aib-o方案(使用aib-o层14)或aib 2.0方案(例如,使用aib 2.0层12)的方式来执行通信。此外,处理器98、可编程逻辑器件92和/或存储器和/或存储电路系统96可以利用不同的通信特征并且可以受益于aib-o层或aib 2.0层。位于数据处理系统90的功能块之间的aib-o层或aib 2.0层的使用除了别的以外还可以使能使用功能块的可缩放的设计并且可以降低电路实现的成本。

54.在一个示例中,数据处理系统90可以是处理各种不同请求的数据中心的一部分。例如,数据处理系统90可以经由网络接口94接收数据处理请求以执行机器学习、视频处理、语音识别、图像识别、数据压缩、数据库搜索排名、生物信息学、网络安全模式识别、空间导航或一些其他专门的任务。处理器98可以促使可编程逻辑器件92的可编程逻辑结构被编程有与请求的任务有关的特定加速器。例如,处理器98可以命令存储在存储器和/或存储电路系统96上的或者高速缓存在可编程逻辑器件92的扇区对齐(sector-aligned)存储器中的

配置数据(比特流)被编程进可编程逻辑器件92的可编程逻辑结构中。配置数据(比特流)可以表示与请求的任务相关的特定加速器功能的电路设计。由于可编程逻辑结构的高密度、大量的扇区对齐存储器与可编程逻辑结构的接近度、或者这里描述的可编程逻辑器件92的其他特征,可编程逻辑器件92可以快速帮助数据处理系统90执行请求的任务。确实,在一个示例中,加速器可以通过使用扇区对齐存储器快速访问和处理加速器中的大量数据来帮助小于几毫秒(例如微秒量级)的语音识别任务。

55.可以静态执行其中计算和存储器具有三维空间局部性的空间架构中的计算和存储器的放置。另外或备选地,可编程逻辑器件92可以在这样的空间架构上动态分配、重定位和解除分配计算和存储器。这些技术使用这样的架构来使能系统的静态映射和动态管理。此外,使用灵活的分配方案使得可编程逻辑器件92能够在静态设置中以静态设置的已知序列发现并支持计算与存储器的最佳共同放置以及在计算和存储器的分配先验未知时在动态设置中发现并支持计算与存储器的最佳共同放置。在三维空间局部性中的静态和/或动态放置的这样的用法提供了扩展编译的能力以支持空间计算与空间分布的存储器的同时合成、放置和路由选择,从而使得用户能够利用具有更加丰富的存储器子系统的架构。对于计算和存储器的动态管理的支持允许用户/管理员为用于可编程逻辑器件92的空间架构构建动态运行时系统。

56.此外,aib-o层14消除了使用某些通信部件之间的转换电路系统的转换,以提供将不同技术用于数据处理系统90的灵活性。例如,数据处理系统90可以使用aib-o层14来使用相同的协议与不同的接口硬层容易地通信,以用于每个子部件的减少的上市时间。例如,在没有使用其他技术重新设计预先存在的装置或者设计具有其中结合的不同接口兼容性的新技术的情况下,可以将新技术与其他技术(例如介质相关的接口(mdi))一起使用。这样的兼容性可以使能处理器98(例如intel xeon

®

)和/或可编程逻辑器件92之间的一致通信,同时与备选的瓦片(tile)互连方法相比降低了数据处理系统90的系统实现成本。

57.本文中呈现和请求保护的技术被引用并且应用于可证明地改进了本技术领域并且因此不是抽象的、无形的或纯粹理论的实际性质的具体示例和实物。此外,如果附加到本说明书的末尾的任何权利要求包含被指定为“用于[执行]

…

[功能]

…

的部件”或“用于[执行]

…

[功能]

…

的步骤”的一个或多个元素,则意图是要在35 u.s.c. 112(f)下解释这样的元素。然而,对于包含以任何其他方式指定的元素的任何权利要求,意图是不要在35 u.s.c. 112(f)下解释这样的元素。

[0058]

示例实施例示例实施例1. 一种半导体装置,所述半导体装置包括:接口,所述接口包括:电路系统的物理布局,所述电路系统的物理布局被配置成与管芯之间的高速协议兼容;以及多个凸块,所述多个凸块具有比为所述高速协议指定的密度更小的密度并且适合于低速协议,其中所述接口被配置成使用所述高速协议进行通信。

[0059]

示例实施例2. 根据示例实施例1所述的半导体装置,所述半导体装置包括经由再分布层被通信耦合至管芯到管芯接口的一个或多个管芯。

[0060]

示例实施例3. 根据示例实施例1所述的半导体装置,其中第一管芯经由所述接口

被通信耦合至第二小芯片。

[0061]

示例实施例4. 根据示例实施例3所述的半导体装置,其中所述第一管芯和所述第二小芯片被配置成使用高级接口总线(aib)2.0协议进行通信。

[0062]

示例实施例5. 根据示例实施例4所述的半导体装置,其中所述接口被配置成具有是所述aib 2.0协议吞吐量的一小部分的吞吐量。

[0063]

示例实施例6. 根据示例实施例5所述的半导体装置,其中所述吞吐量等于或小于每秒64千兆位。

[0064]

示例实施例7. 根据示例实施例5所述的半导体装置,其中所述接口的所述吞吐量小于或等于为aib 2.0指定的四分之一。

[0065]

示例实施例8. 根据示例实施例5所述的半导体装置,其中所述吞吐量被参数化并且能够由所述半导体装置的制造商来配置。

[0066]

示例实施例9. 根据示例实施例1所述的半导体装置,所述半导体装置包括由有机材料构成的衬底,所述多个凸块被耦合至所述衬底。

[0067]

示例实施例10. 根据示例实施例1所述的半导体装置,其中所述凸块具有比45毫米宽的间距。

[0068]

示例实施例11. 根据示例实施例1所述的半导体装置,其中所述凸块包括c4凸块。

[0069]

示例实施例12. 一种小芯片,所述小芯片包括:具有第一通信通道的管芯;以及与所述第一通信通道相关联的第一接口,其中所述接口包括:被配置成支持高级接口总线2.0(aib 2.0)协议连接的电路系统;以及多个凸块,所述多个凸块具有比为所述aib 2.0协议指定的密度更小的密度,其中所述第一接口被配置成使用所述aib 2.0协议进行通信。

[0070]

示例实施例13. 根据示例实施例12所述的小芯片,所述小芯片包括再分布层,所述再分布层促进所述多个凸块和所述管芯之间的连接。

[0071]

示例实施例14. 根据示例实施例13所述的小芯片,其中所述小芯片经由所述接口被通信耦合至第二小芯片。

[0072]

示例实施例15. 根据示例实施例12所述的小芯片,其中所述接口被配置成具有是与所述aib 2.0协议相对应的吞吐量的一小部分的吞吐量。

[0073]

示例实施例16. 根据示例实施例12所述的小芯片,其中所述凸块包括c4凸块。

[0074]

示例实施例17. 根据示例实施例12所述的小芯片,其中所述管芯包括第二通道,所述第二通道包括第二接口,所述第二接口包括具有为所述aib 2.0协议指定的密度的附加的多个凸块,并且其中所述第二接口被配置成使用所述aib 2.0协议进行通信。

[0075]

示例实施例18. 一种芯片,所述芯片包括:顶部金属层;以及再分布层,其中所述再分布层被配置成选择性地将具有第一通信架构的第一接口层或者具有第二通信架构的第二接口层用作所述顶部金属层,其中所述第一接口层包括所述第二接口层的多个凸块的一小部分,其中所述第一通信架构和所述第二通信架构被配置成使用相同的通信协议进行通信。

[0076]

示例实施例19. 根据示例实施例18所述的芯片,其中所述相同的通信协议包括高

级接口总线(aib)。

[0077]

示例实施例20. 根据示例实施例18所述的芯片,其中所述第一接口层包括微凸块并且所述第二接口层包括c4凸块。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。