1.本发明涉及显示技术领域,特别涉及一种阵列基板及液晶显示面板。

背景技术:

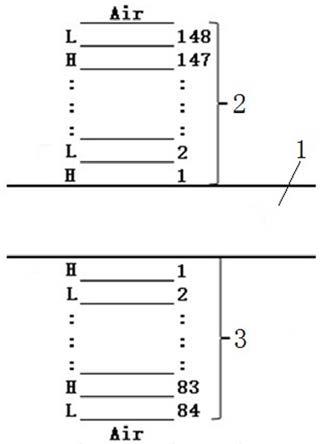

2.8畴像素架构,在保持原有cof(覆晶薄膜)数量的前提下,实现va(垂直配向)显示模式的视角优化。而现存量产的8畴像素架构中又分为3t像素架构(图1)和3t plus像素架构(图2和图3),8畴像素架构发展的前期,液晶显示面板所使用的像素架构均为3t像素架构,参照图1,主区薄膜晶体管t

main

的栅极连接扫描线gate,源极连接数据线data,漏极分别连接主区存储电容c

st_main

的一端和主区液晶电容c

lc_main

一端,主区存储电容c

st_main

的另一端连接阵列公共电极acom,主区液晶电容c

lc_main

的另一端连接cf公共电极cfcom;次区薄膜晶体管t

sub

的栅极连接扫描线gate,源极连接数据线data,漏极分别连接次区存储电容c

st_sub

的一端和次区液晶电容c

lc_sub

的一端,次区存储电容c

st_sub

的另一端连接阵列公共电极acom,次区液晶电容c

lc_sub

的另一端连接cf公共电极cfcom;共享薄膜晶体管t

cs

的栅极连接数据线gate,源极连接次区薄膜晶体管t

sub

的漏极,漏极连接阵列公共电极acom。

3.但是由于3t像素架构改善视角的主要手段为将次像素电极(sub pixel)的电压通过共享薄膜晶体管t

cs

分享到阵列公共电极acom上,因为阵列公共电极acom和次像素电极存在一个次区存储电容c

st_sub

,所以会因为阵列公共电极acom电压的不稳定引发横向串扰的问题。

4.为了解决串扰的问题,3t plus像素架构应运而生,在3t plus像素架构中主要是在保持阵列公共电极acom与次像素电极间次区存储电容c

st_sub

不变的情况下设置第二个阵列公共电极acom2(share bar,共享公共电极),将次像素电极的电压分享到acom2上,但又因为现有3t plus像素架构中acom2会纵向穿过显示区(参照图3和图3a),即,acom2会穿过主像素电极(main pixel)和次像素电极,即穿过显示区,所以会导致像素电极的开口率降低,进而导致穿透率降低。

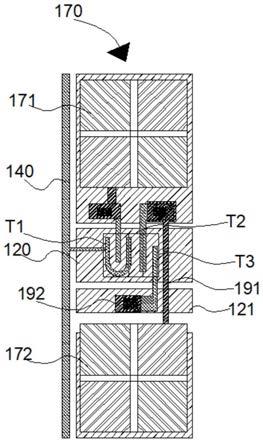

技术实现要素:

5.本发明目的在于,解决现有3t plus像素架构会导致像素电极开口率降低的问题。

6.为实现上述目的,本发明提供一种阵列基板,其特征在于,包括:底板;第一金属层,设置于所述底板上,所述第一金属层包括:栅极扫描线,阵列公共电极和共享公共电极,所述共享公共电极与所述栅极扫描线和所述阵列公共电极平行间隔排布;像素电极层,与所述第一金属层异层设置于所述底板上,所述像素电极层包括呈阵列排布的多个子像素电极,所述子像素电极包括主像素电极和次像素电极;第一薄膜晶体管,所述第一薄膜晶体管的漏极与所述主像素电极电连接;第二薄膜晶体管,所述第二薄膜晶体管的漏极与所述次像素电极电连接;第三薄膜晶体管,所述第三薄膜晶体管的源极与所述第二薄膜晶体管的漏极电连接,所述第三薄膜晶体管的漏极与所述共享公共电极电连接。

7.可选的,所述阵列基板还包括:栅极绝缘层,设置于所述底板上并覆盖所述第一金

属层;第二金属层,设置于所述栅极绝缘层上,所述第二金属层包括所述第一薄膜晶体管的源极和漏极、第二薄膜晶体管的源极和漏极、以及第三薄膜晶体管的源极和漏极;有机层,设置于所述第二金属层上,所述有机层表面开设有暴露部分所述共享公共电极和暴露部分所述第三薄膜晶体管的所述源极或所述漏极的第一过孔,所述像素电极层设置于所述第一过孔外侧的所述有机层上;导电膜层,沉积于所述第一过孔,所述导电膜层至少覆盖所述共享公共电极和所述第三薄膜晶体管的部分所述源极或部分所述漏极,所述第三薄膜晶体管的所述漏极通过所述导电膜层与所述共享公共电极电连接。

8.可选的,所述第一过孔开设于位于所述主像素电极与所述次像素电极之间的所述有机层表面。

9.可选的,靠近所述共享公共电极一侧的所述第一过孔的内径小于靠近所述有机层一侧的所述第一过孔的内径。

10.可选的,所述第一过孔暴露所述第三薄膜晶体管的所述漏极的侧壁。

11.可选的,所述第一过孔暴露所述第三薄膜晶体管的所述漏极的侧壁和所述漏极远离所述共享公共电极一面的部分表面。

12.可选的,所述阵列基板还包括:栅极绝缘层,设置于所述底板上并覆盖所述第一金属层,所述栅极绝缘层表面开设有暴露部分所述共享公共电极的第二过孔;所述第三薄膜晶体管的所述漏极通过所述第二过孔与所述共享公共电极电连接。

13.可选的,所述共享公共电极位于所述栅极扫描线和所述次像素电极对应的所述阵列公共电极之间。

14.本发明还提供一种液晶显示面板,包括:如前所述的阵列基板;彩膜基板,与所述阵列基板相对设置;液晶层,设置于所述阵列基板与所述彩膜基板之间。

15.本发明的有益效果在于,本发明提供一种阵列基板及液晶显示面板,所述阵列基板通过将共享公共电极与栅极扫描线同层设置,并通过开设第一过孔以暴露部分共享公共电极和第三薄膜晶体管的部分漏极,将第三薄膜晶体管的漏极通过导电膜层与共享公共电极电连接,从而使得共享公共电极只存在于主像素电极与次像素电极之间的非显示区,共享公共电极无需穿过主像素电极和次像素电极,增大像素电极的开口率,增大穿透率。

附图说明

16.下面结合附图,通过对本发明的具体实施方式详细描述,将使本发明的技术方案及其它有益效果显而易见。

17.图1是现有3t像素架构的电路示意图;

18.图2是现有3t plus像素架构的电路示意图;

19.图3是现有3t plus像素架构的子像素俯视图;

20.图3a是图3的局部结构示意图;

21.图4是本发明一示例性实施例的阵列基板的子像素的俯视图;

22.图4a是图4的局部结构示意图;

23.图5是本发明一示例性实施例的阵列基板中像素架构的电路示意图;

24.图6是图4a的a-a向剖视图;

25.图7是本发明一示例性实施例的液晶显示面板的结构示意图;

26.图8是本发明另一示例性实施例的阵列基板的结构示意图;

27.图9是本发明又一示例性实施例的阵列基板的子像素的俯视图;

28.图9a是图9的局部结构示意图;

29.图10是图9a的b-b向剖视图。

30.其中,图6和图10中未体现数据线。

31.图中部件编号如下:

32.1、液晶显示面板,100、100’、阵列基板,110、底板,120、栅极扫描线,121、共享公共电极,130、栅极绝缘层,131、第一开孔,140、数据线,150、钝化层,151、151’、第二开孔,160、有机层,161、色阻层,1611、1611’、第三开孔,162、平坦化层,1621、第四开孔,163、连接孔,170、子像素,171、主像素电极,172、次像素电极,181、181’、第一过孔,182、第二过孔,191、连接膜层,192、导电膜层,200、彩膜基板,210、衬底基板,220、黑矩阵层,230、彩膜电极层,300、液晶层。

具体实施方式

33.下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

34.本发明所提供的阵列基板,通过将共享公共电极与扫描线同层设置,并通过开设第一过孔以暴露部分共享公共电极和第三薄膜晶体管的部分漏极,将第三薄膜晶体管的漏极通过导电膜层与共享公共电极电连接,从而使得共享公共电极只存在于主像素电极与次像素电极之间的非显示区,共享公共电极无需穿过主像素电极和次像素电极,增大像素电极的开口率,增大穿透率。作为典型应用,所述阵列基板可用于液晶显示面板上,所述液晶显示面板可被应用于显示终端上,例如薄膜晶体管-液晶显示器(tft-lcd)。

35.本发明的一个实施例中,参照图4~6以及图4a,阵列基板100包括层叠设置的底板110、第一金属层m1(图中未示出)、栅极绝缘层130、第二金属层m2(图中未示出)、钝化层150、有机层160和像素电极层(图中未示出)。有机层160包括层叠设置的色阻层161和平坦化层162。钝化层150设置于栅极绝缘层130上并覆盖第二金属层m2。像素电极层包括呈阵列排布的多个子像素170,每个子像素170包括主像素电极171和次像素电极172。子像素阵列中,每一行子像素170对应设置一条栅极扫描线120,栅极扫描线120位于主像素电极171和次像素电极172之间,一列子像素对应一条数据线140,主像素电极171电连接第一薄膜晶体管t1的漏极,次像素电极172电连接第二薄膜晶体管t2的漏极。主像素电极171和次像素电极172分别对应4个畴的液晶分子,形成子像素170的8畴像素结构。

36.其中,参照图4,本实施例中所述第一薄膜晶体管t1为u型(u type)薄膜晶体管,第二薄膜晶体管t2和第三薄膜晶体管t3分别为i型(i type)薄膜晶体管。

37.参照图5,第一薄膜晶体管t1的栅极连接栅极扫描线120,其源极连接数据线140,其漏极分别连接主区存储电容cst1的一端和主区液晶电容clc1的一端,所述主区存储电容cst1的另一端连接阵列公共电极acom,主区液晶电容clc1的另一端连接cf公共电极cfcom;第二薄膜晶体管t2的栅极连接栅极扫描线120,其源极连接数据线140,其漏极与第三薄膜

晶体管t3的源极连接,第二薄膜晶体管t2的漏极分别连接次区存储电容cst2的一端和次区液晶电容clc2的一端,所述次区存储电容cst2的另一端连接阵列公共电极acom,次区液晶电容clc2的另一端连接cf公共电极cfcom;第三薄膜晶体管t3的源极与第二薄膜晶体管t2的漏极连接,第三薄膜晶体管t3的栅极连接栅极扫描线120,其漏极t3d电连接共享公共电极121。

38.有机层160上还设置有连接孔163,所述有机层160的表面设置有连接膜层191,连接膜层191与像素电极层同层设置于所述有机层160表面,所述连接膜层191的一端通过连接孔163与所述第二薄膜晶体管t2的漏极电连接,所述连接膜层191的另一端与次像素电极172电连接。

39.在本实施例中,第一薄膜晶体管t1的栅极、第二薄膜晶体管t2的栅极、第三薄膜晶体管t3的栅极、栅极扫描线120以及共享公共电极121同层设置,形成所述第一金属层m1,参照图4a,共享公共电极121与栅极扫描线120平行间隔排布,共享公共电极121在底板110上的正投影紧靠着次像素电极172在底板110上的正投影外侧,具体地,共享公共电极121在底板110上的正投影位于栅极扫描线120在底板110上的正投影和次像素电极172在底板110上的正投影之间,图中也可见,共享公共电极121位于栅极扫描线120和次像素电极172对应的阵列公共电极之间区域位置。第一金属层m1设置于底板110上,栅极绝缘层130覆盖所述第一金属层m1,参照图6,靠近所述第三薄膜晶体管t3的漏极t3d的所述栅极绝缘层130表面开设有暴露部分共享公共电极121的第一开孔131。

40.数据线140、第一薄膜晶体管t1的源极和漏极、第二薄膜晶体管t2的源极和漏极以及第三薄膜晶体管t3的源极和漏极同层设置,形成所述第二金属层m2,第二金属层m2设置于所述栅极绝缘层130上,有机层160设置于所述钝化层150上,具体地,所述有机层160的色阻层161设置于钝化层150上,参照图6,所述钝化层150表面开设有与第一开孔131连通的第二开孔151,所述色阻层161上开设有与所述第二开孔151连通的第三开孔1611,所述第二开孔151暴露所述第三薄膜晶体管t3的漏极t3d的侧壁,对应地,所述第三开孔1611暴露所述第三薄膜晶体管t3的漏极t3d的侧壁,平坦化层162开设有与第三开孔1611连通的第四开孔1621,所述第一开孔131、第二开孔151、第三开孔1611和第四开孔1621依次连通形成第一过孔181,第三开孔1611靠近第一开孔131一端的内径小于第四开孔1621远离第三开孔1611一端内径。

41.第一过孔181内设置有导电膜层192,导电膜层192覆盖暴露于第一开孔131的共享公共电极121和暴露于第三开孔1611的第三薄膜晶体管t3的漏极t3d,形成共享公共电极121与第三薄膜晶体管t3的漏极t3d之间的电连接。参照图6,导电膜层192通过第一过孔181覆盖暴露于第一开孔131的共享公共电极121和暴露于第三开孔1611的第三薄膜晶体管t3的漏极t3d,形成共享公共电极121与第三薄膜晶体管t3的漏极t3d之间的电连接,由于共享公共电极121所在的第一金属层m1和第三薄膜晶体管t3的漏极t3d所在的第二金属层m2异层设置,具体地,第二金属层m2在第一金属层m1上方,因此此种连接方式被称为深浅孔连接方式。

42.所述连接膜层191、导电膜层192的上端平面以及像素电极层同层设置于有机层160表面,通过图案化ito(氧化铟锡)膜层,分别形成所述连接膜层191、所述导电膜层192以及所述像素电极层。

43.本实施例中,将共享公共电极121由第二金属层m2转移至第一金属层m1,并与栅极扫描线120和阵列公共电极acom平行间隔排布,并通过导电膜层192实现共享公共电极121和第三薄膜晶体管t3的漏极t3d之间的电连接,避免共享公共电极121穿过主像素电极171和次像素电极172所在的显示区,共享公共电极121在非显示区(主像素电极171与次像素电极172之间)即可与第三薄膜晶体管t3的漏极t3d电连接,将次像素电极172的电压分享(share)至共享公共电极121上,而且共享公共电极121与次像素电极172异层设置且平行间隔排布,具体地,共享公共电极121在底板110上的正投影位于次像素电极172在底板110上的正投影外侧,故而共享公共电极121与次像素电极172之间不会形成电容,解决横向串扰问题,而且共享公共电极121设置于非显示区,未穿过主像素电极171和次像素电极172,也不会影响像素电极层的子像素170的开口率,反而会提升开口率,进而提升光穿透率。

44.其中,在色阻层161和平坦化层162的制程中,对色阻层161进行开孔形成第三开孔1611,由于色阻属于有机物且比较厚,所以第三开孔1611需求的面积较大,对开口率仍有损失,但相对于将共享公共电极121设置于第二金属层m2且纵向穿过显示区的设计相比,开口率仍有改善。

45.同时,本发明还提供一种液晶显示面板1,参照图7,所述液晶显示面板1包括所述阵列基板100、彩膜基板200和液晶层300,阵列基板100和彩膜基板200相对设置,液晶层300设置于阵列基板100和彩膜基板200之间,彩膜基板200包括衬底基板210、设置于衬底基板210上的黑矩阵层220和设置于黑矩阵层220上的彩膜电极层230,所述彩膜电极层230与所述像素电极层相对设置,彩膜电极层230包括多个所述cf公共电极cfcom。

46.在本发明另一实施例中,参照图8,开设于阵列基板100’的所述钝化层150的第二开孔151’除暴露所述第三薄膜晶体管t3的漏极t3d的侧壁外,还暴露第三薄膜晶体管t3的漏极t3d的部分表面(即漏极t3d远离栅极绝缘层130一面的部分表面),对应地,开设于所述色阻层161的第三开孔1611’除暴露所述第三薄膜晶体管t3的漏极t3d的侧壁外,还暴露第三薄膜晶体管t3的漏极t3d的部分表面(即漏极t3d远离栅极绝缘层130一面的部分表面),形成阶梯状结构,从而增加导电膜层192与第三薄膜晶体管t3的漏极t3d的接触面积,保证共享公共电极121与第三薄膜晶体管t3的漏极t3d之间电连接的稳定性,同时可保证第三薄膜晶体管t3的漏极t3d对导电膜层192的稳定支撑,所述第一开孔131、第二开孔151’、第三开孔1611’和第四开孔1621依次连通形成第一过孔181’。

47.在本发明又一实施例中,参照图9、图9a和图10,阵列基板100”包括层叠设置的底板110、第一金属层m1(图中未示出)、栅极绝缘层130、第二金属层m2(图中未示出)、钝化层150、有机层160和像素电极层(图中未示出)。有机层160包括层叠设置的色阻层161和平坦化层162。像素电极层包括呈阵列排布的多个子像素170,每个子像素170包括主像素电极171和次像素电极172。子像素阵列中,每一行子像素170对应设置一条栅极扫描线120,所述栅极扫描线120位于主像素电极171和次像素电极172之间,一列子像素对应一条数据线140,主像素电极171电连接第一薄膜晶体管t1的漏极,次像素电极172电连接第二薄膜晶体管t2的漏极,第三薄膜晶体管t3的源极与所述第二薄膜晶体管t2的漏极电连接,所述第三薄膜晶体管t3的漏极t3d与所述共享公共电极121电连接。

48.第一薄膜晶体管t1的栅极、第二薄膜晶体管t2的栅极、第三薄膜晶体管t3的栅极、栅极扫描线120以及共享公共电极121同层设置,形成所述第一金属层m1,共享公共电极121

与栅极扫描线120和阵列公共电极acom平行间隔排布,第一金属层m1设置于底板110上,栅极绝缘层130覆盖所述第一金属层m1。参照图10,与所述第三薄膜晶体管t3的漏极t3d相对应的所述栅极绝缘层130表面开设有第二过孔182,所述第二过孔182暴露部分所述共享公共电极121,所述第三薄膜晶体管t3的漏极t3d通过第二过孔182与共享公共电极121电连接。

49.具体方法为利用光罩在栅极绝缘层130表面形成所述第二过孔182,然后在栅极绝缘层130上形成第二金属层m2,第二金属层m2的第三薄膜晶体管t3的漏极t3d通过第二过孔182与共享公共电极121电连接,从而可以避免对色阻层161进行开孔,而且栅极绝缘层130开孔形成第二过孔182所需求面积会远小于在色阻层161上开口所需面积,所以会进一步增加像素电极开口率,进而增大穿透率。

50.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出多个改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。