半导体装置

1.相关申请的引用

2.本技术以由2020年9月9日申请的在先的日本国专利申请第2020-151299带来的优先权的利益为基础,并且要求该优先权的利益,在先申请的内容整体通过引用而包含于此。

技术领域

3.本发明的实施方式涉及半导体装置。

背景技术:

4.大规模集成电路(lsi)等半导体装置具备芯片层叠体,该芯片层叠体具有层叠于布线基板上的多个半导体芯片。芯片层叠体通过接合线与布线基板电连接。

技术实现要素:

5.一个实施方式提供抑制了信号质量降低的半导体装置。

6.实施方式的半导体装置具备:布线基板,包含与信号端子电连接的第一接合焊盘、与电源端子电连接的第二接合焊盘及与接地端子电连接的第三接合焊盘;芯片层叠体,包含阶梯地层叠于布线基板之上的多个半导体芯片,半导体芯片分别具有第一连接焊盘、第二连接焊盘及第三连接焊盘,多个第一连接焊盘经由多个第一接合线而串联连接并且与第一接合焊盘串联连接由此形成第一传输路径,多个第二连接焊盘经由多个第二接合线而串联连接并且与第二接合焊盘串联连接由此形成第二传输路径,多个第三连接焊盘经由多个第三接合线而串联连接并且与第三接合焊盘串联连接由此形成第三传输路径;以及至少一个终端电阻,从由与第一传输路径以及第二传输路径连接的第一终端电阻以及与第一传输路径以及第三传输路径连接的第二终端电阻构成的组中选择,并且设置于芯片层叠体之上。

7.根据上述结构,能够提供抑制了信号质量降低的半导体装置。

附图说明

8.图1是用于说明半导体装置的构造例的剖视示意图。

9.图2是用于说明半导体装置的构造例的俯视示意图。

10.图3是图2的一部分的放大图。

11.图4是用于说明半导体装置的其他构造例的示意图。

12.图5是用于说明半导体装置的其他构造例的示意图。

13.图6是半导体存储装置的等效电路图。

14.图7是表示经由信号端子而输入输出的信号的eye图案的例子的图。

15.图8是用于说明半导体装置的其他构造例的剖视示意图。

16.图9是用于说明半导体装置的其他构造例的俯视示意图。

17.图10是图9的一部分的放大图。

18.图11是用于说明半导体装置的其他构造例的示意图。

19.图12是用于说明半导体装置的其他构造例的示意图。

20.图13是用于说明第一布线和第二布线的其他平面形状的示意图。

21.图14是用于说明半导体装置的其他构造例的示意图。

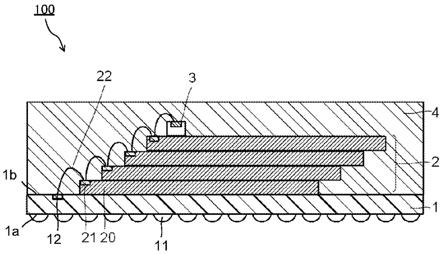

22.图15是用于说明半导体装置的其他构造例的示意图。

具体实施方式

23.以下,参照附图对实施方式进行说明。附图中记载的各构成要素的厚度与平面尺寸的关系、各构成要素的厚度的比率等有时与实物不同。另外,在实施方式中,对实质上相同的构成要素标注相同的附图标记并适当省略说明。

24.在本说明书中,“连接”除了特别指定的情况之外,不仅包括物理连接,还包括电连接。

25.(第一实施方式)

26.以下对半导体装置的构造例进行说明。图1是用于说明半导体装置的构造例的剖视示意图。图2是用于说明半导体装置的构造例的俯视示意图。半导体装置100具备布线基板1、芯片层叠体2、多个终端电阻3和绝缘树脂层4。

27.布线基板1具有设置于第一表面1a的多个外部连接端子11和设置于第一表面的相反侧的第二表面1b的多个接合焊盘12。布线基板1的例子包括印刷布线板(pwb)。

28.多个外部连接端子11包括信号端子、电源端子以及接地端子。外部连接端子11使用例如金、铜、焊料等形成。外部连接端子11例如也可以使用锡-银系、锡-银-铜系的无铅焊料来形成。另外,也可以使用多个金属材料的层叠来形成外部连接端子11。另外,在图1中,使用导电性球形成外部连接端子11,但也可以使用凸块来形成外部连接端子11。

29.多个接合焊盘12经由布线基板1的内部布线与多个外部连接端子11连接。多个接合焊盘12包含与信号端子电连接的第一接合焊盘121、与电源端子连接的第二接合焊盘122、以及与接地端子电连接的第三接合焊盘123。多个接合焊盘12含有例如铜、银、金、或镍等金属元素。例如,也可以通过利用电解镀法或电解镀法等形成包含上述材料的镀膜来形成多个接合焊盘12。另外,也可以使用导电性膏形成多个接合焊盘12。

30.芯片层叠体2包含多个半导体芯片20。半导体芯片20的例子包括存储器芯片。多个半导体芯片20阶梯地层叠于布线基板1的第二表面1b之上。换言之,多个半导体芯片20相互局部地重叠。多个半导体芯片20例如夹着芯片粘贴膜等粘接层而相互粘接。图1所示的芯片层叠体2具有4个半导体芯片20,但半导体芯片20的数量并不限定于图1所示的数量。

31.多个半导体芯片20分别具有多个连接焊盘21。多个半导体芯片20经由多个接合线22而连接。多个连接焊盘21包括第一连接焊盘211、第二连接焊盘212和第三连接焊盘213。多个接合线22包括多个第一接合线221、多个第二接合线222、以及多个第三接合线223。

32.多个半导体芯片20中的多个第一连接焊盘211经由多个第一接合线221而串联连接并且与第一接合焊盘121串联连接,由此形成第一传输路径。

33.多个半导体芯片20中的多个第二连接焊盘212经由第二接合线222而串联连接并且与第二接合焊盘122串联连接,由此形成第二传输路径。

34.多个半导体芯片20中的多个第三连接焊盘213经由第三接合线223而串联连接并

且与第三接合焊盘123串联连接,由此形成第三传输路径。

35.接合线22含有例如金、银、铜、铝等金属元素。

36.多个终端电阻3设置于芯片层叠体2之上。多个终端电阻3包括第一芯片电阻器31和第二芯片电阻器32。这些芯片电阻器例如经由粘接层安装于芯片层叠体2之上。第一芯片电阻器31与第一传输路径及第二传输路径连接。第二芯片电阻器32与第一传输路径及第三传输路径连接。通过使用上述芯片电阻器,例如能够减小终端电阻3的面积。终端电阻3的电阻值没有特别限定,例如为50ω以上。

37.图3是图2的一部分的放大图。第一芯片电阻器31具有与第一传输路径连接的第一电极焊盘311及与第二传输路径连接的第二电极焊盘312。第二芯片电阻器32具有与第一传输路径连接的第一电极焊盘321及与第三传输路径连接的第二电极焊盘322。

38.半导体装置100只要具有至少一个终端电阻3即可。图4以及图5是用于说明半导体装置100的其他构造例的示意图。半导体装置100的其他结构例如图4所示那样不具有第一芯片电阻器31,或者如图5所示那样不具有第二芯片电阻器32。对于这些不同点以外的部分,可以适当引用图1及图2所示的半导体装置100的说明。

39.绝缘树脂层4覆盖芯片层叠体2、接合线22及终端电阻3。绝缘树脂层4含有氧化硅(sio2)等无机填充材料,例如使用将无机填充材料与有机树脂等混合而成的密封树脂,通过传递模塑法、压缩模塑法、注射模塑法等模塑法形成。

40.在本实施方式的半导体装置中,通过将第一芯片电阻器31的电阻值、第二芯片电阻器32的电阻值、或者第一芯片电阻器31以及第二芯片电阻器32的并联合成电阻值与第一传输路径的特性阻抗相匹配,由此抑制经由信号端子的信号的反射波。

41.在此,为了说明终端电阻3对反射波的抑制效果,参照图6以及图7对半导体存储装置的存储器与存储器控制器的连接结构与信号质量降低之间的关系进行说明。图6是半导体存储装置的等效电路图。图7是表示经由信号端子输入输出的信号的eye图案的例子的图。

42.半导体存储装置具备由芯片层叠体2构成的存储器及存储器控制器5。芯片层叠体2具有电容成分c1和电感成分l1。存储器控制器5具有电容成分c2和电感成分l2。芯片层叠体2与存储器控制器5经由布线基板1电连接。这些要素形成上述第一传输路径。

43.在半导体存储装置中,例如在读出时经由第一传输路径而产生信号的反射波。由此,例如信号的偏差变大,eye图案6变形。芯片层叠体2与存储器控制器5之间的传输速度越高,上述现象越显著。

44.与此相对,如图6所示,在第一传输路径上连接终端电阻3、并将终端电阻3的电阻值与第一传输路径的特性阻抗进行匹配,由此能够抑制信号的反射波。由此,能够抑制eye图案6的变形。因此,能够抑制信号质量降低。

45.在现有的半导体装置之一中,已知在与单一的半导体芯片连接的信号线上连接终端电阻的装置。但是,如本实施方式的半导体装置那样,在层叠多个半导体芯片的情况下,如果不使由将半导体芯片间电连接的导体和半导体芯片的连接焊盘构成的传输路径的特性阻抗与终端电阻的电阻值匹配,则难以抑制信号的反射波。

46.另外,作为现有的半导体装置的另一个,已知有使用在半导体芯片内的包括输入元件的输入电路中内置终端电阻的片内端接(on-die termination;odt)的装置。然而,odt

为,在由将半导体芯片之间电连接的导体和半导体芯片的连接焊盘构成的传输路径的特性阻抗小到10数ω的情况下,odt的电路尺寸变大,半导体芯片的尺寸变大。另外,关于odt,如果在电路设计的阶段没有装入终端方式的切换电路、以及odt的电阻值的调整电路,则无法进行终端方式的切换以及odt的电阻值的调整,因此在电路设计后无法进行灵活的变更。

47.与此相对,在本实施方式的半导体装置中,通过在芯片层叠体之上设置与包含将多个半导体芯片连接的接合线在内的第一传输路径连接的终端电阻,由此各半导体芯片无需具有任何终端电阻。由此,能够提高半导体芯片的电路设计的自由度。

48.(第二实施方式)

49.以下对半导体装置的其他结构例进行说明。图8是用于说明半导体装置的其他构造例的剖视示意图。图9是用于说明半导体装置的其他构造例的俯视示意图。半导体装置100具备布线基板1、芯片层叠体2、多个终端电阻3以及绝缘树脂层4。关于布线基板1、芯片层叠体2以及绝缘树脂层4,与第一实施方式的半导体装置的布线基板1、芯片层叠体2以及绝缘树脂层4相同,因此省略说明,能够适当引用第一实施方式的说明。

50.多个终端电阻3设置于芯片层叠体2之上。多个终端电阻3包括第一布线33及第二布线34。这些布线通过例如溅射或镀敷等方法形成于芯片层叠体2的表面。布线包含例如金、银、铜、钛、铬等材料。第一布线33与第一传输路径以及第二传输路径连接。第二布线34与第一传输路径以及第三传输路径连接。通过使用上述布线,例如能够容易地调整终端电阻3的电阻值。

51.图10是图9的一部分的放大图。第一布线33具有与第一传输路径连接的一端和与第二传输路径连接的另一端。第二布线34具有与第一传输路径连接的一端和与第三传输路径连接的另一端。

52.半导体装置100只要具有至少一个终端电阻3即可。图11以及图12是用于说明半导体装置100的其他构造例的示意图。半导体装置100的其他构造例如图11所示那样不具有第一布线33,或者如图12所示那样不具有第二布线34。关于这些不同点以外的部分,能够适当引用图8以及图9所示的半导体装置100的说明。

53.图9至图12所示的第一布线33以及第二布线34的平面形状具有环形状,但第一布线33以及第二布线34的平面形状没有特别限定。图13是用于说明第一布线33及第二布线34的其他平面形状的示意图。第一布线33及第二布线34的其他平面形状具有曲折形状。由此,能够容易地增加终端电阻3的电阻。

54.图14以及图15是用于说明半导体装置100的其他构造例的示意图。半导体装置100的其他构造例,如图14所示那样不具有具有曲折形状的第一布线33,或者如图15所示那样不具有具有曲折形状的第二布线34。关于这些不同点以外的部分,能够适当引用图8以及图9所示的半导体装置100的说明。

55.在本实施方式的半导体装置中,通过将第一布线33的电阻值、第二布线34的电阻值、或者第一布线33以及第二布线34的并联合成电阻值与第一传输路径的特性阻抗进行匹配,从而抑制经由信号端子的信号的反射波。因此,能够抑制信号质量降低。

56.另外,在本实施方式的半导体装置中,通过在芯片层叠体之上设置与包含将多个半导体芯片连接的接合线在内的第一传输路径连接的终端电阻,由此各半导体芯片无需具有任何终端电阻。由此,能够提高半导体芯片的电路设计的自由度。

57.对本发明的几个实施方式进行了说明,但这些实施方式是作为例子进行提示的,并不意图限定发明的范围。这些新的实施方式能够以其他各种方式实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式及其变形包含在发明的范围及主旨中,并且包含在权利要求书所记载的发明及其等同的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。