1.本文的实施方式涉及与固态纳米孔传感器一起使用的流动池及其制造方法。

背景技术:

2.固态纳米孔传感器已经成为一种低成本、易运输且快速处理的生物聚合物(例如,dna或rna)测序技术。生物聚合物链的固态纳米孔测序典型地包括通过一个或多个纳米级大小的开口(即,纳米孔)将生物聚合物链易位,每个开口的直径为在约0.1nm与约100nm之间。在单孔传感器中,纳米孔穿过膜片层设置,所述膜片层将两个导电流体贮存器分开。要测序的生物聚合物链,例如特征性带负电荷的dna或rna链,被引入两个导电流体贮存器中的一者,并且然后通过在两者间提供电位来将其拉过纳米孔。在生物聚合物链行进穿过纳米孔时,该生物聚合物链的不同单体单元,例如dna或rna链的蛋白质碱基,堵塞纳米孔的不同百分比,从而改变从中流过的离子电流。所得的电流信号模式可用于确定生物聚合物链中的单体单元的序列,诸如dna或rna链中的蛋白质序列。一般来讲,单孔传感器缺乏用于减慢生物聚合物链通过纳米孔的易位速率而同时仍然在两个贮存器之间提供足够的电位以优化在所得的电流信号模式中的信噪比的机制。

3.有益地,双孔传感器通过在该双孔传感器的两个纳米孔中共捕获生物聚合物链来提供用于控制生物聚合物链的易位速率的机制。典型的双孔传感器具有由壁分开的两个流体贮存器、共同流体腔室和将共同流体腔室与流体贮存器中的每一者分开的膜片,膜片层具有从中穿过设置的两个纳米孔。要测序的生物聚合物链通过第二纳米孔从第一流体贮存器行进到共同腔室并从该共同腔室行进到第二流体贮存器。理想地,两个纳米孔彼此足够接近,以允许共捕获生物聚合物链。当生物聚合物链由两个纳米孔共捕获时,在每个纳米孔上施加竞争电位以产生“拔河”,其中生物聚合物链的相对两端被拉向相反行进方向上。有益地,可调整在竞争电位之间的差异以控制生物聚合物链通过纳米孔的易位速率以及因此一种或多种由此产生的电信号电流信号模式的分辨率。

4.通常,双纳米孔传感器是使用两个基板形成的。典型地,第一基板由非晶非单晶材料(诸如玻璃)形成,该第一基板被图案化以形成两者间设置有壁的第一流体贮存器和第二流体贮存器。第二基板由单晶硅形成,并且包括膜片层的多层堆叠物形成在其表面上。然后,将第二基板的膜片层阳极结合到第一基板的图案化表面,从多层堆叠物去除硅基板,并且在多层堆叠物中蚀刻开口以形成共同腔室。然后,使用聚焦离子束(fib)钻孔工艺穿过设置在壁的任一侧上的膜片层的相应部分形成纳米孔。

5.不幸地,上述制造方法一般与将双孔传感器从研发实验室转移到公共市场所需的大批量制造、质量、可重复性和成本要求不相容。此外,上述制造方法一般将在两个纳米孔之间的最小间距限制为约550nm,这因此限制了由此形成的双孔传感器对相对较短的生物聚合物链进行测序的能力。

6.因此,本领域中需要形成双孔传感器的改善的方法和通过该方法形成的改善的双孔传感器。

技术实现要素:

7.本公开内容的实施方式提供了可用于生物聚合物测序的固态双孔传感器及其制造方法。

8.在一个实施方式中,一种形成双孔传感器的方法包括在基板的表面中提供图案。一般来讲,所述图案具备由分隔壁分开的两个流体贮存器。所述方法进一步包括:将牺牲材料层沉积到所述两个流体贮存器中;沉积膜片层,穿过所述膜片层图案化两个纳米孔;从所述两个流体贮存器去除所述牺牲材料;和图案化一个或两个流体端口和共同腔室。

9.在另一个实施方式中,一种双孔传感器具备:基板,所述基板具有图案化表面,所述图案化表面包括由分隔壁间隔开的两个凹陷区域;和膜片层,所述膜片层设置在所述图案化表面上。所述膜片层、所述分隔壁以及所述两个凹陷区域中的每一者的一个或多个表面共同地限定第一流体贮存器和第二流体贮存器。第一纳米孔穿过所述膜片层的设置在所述第一流体贮存器上方的部分设置,并且第二纳米孔穿过所述膜片层的设置在所述第二流体贮存器上方的部分设置。在本文中,所述分隔壁的相对表面倾斜,以各自与所述膜片层的相应的面向贮存器的表面形成小于90

°

的角度。

附图说明

10.为了可详细地理解本公开内容的上述特征,可参考实施方式来得到以上简要地概述的本公开内容的更特别的描述,实施方式中的一些示出在附图中。然而,需注意,附图仅仅示出了本公开内容的典型的实施方式,并且因此不应当被视为对其范围的限制,并且本公开内容可允许其他等效实施方式。

11.图1a是示意性地示出使用本文描述的实施方式的一个或多个组合形成的双孔传感器的一部分的特写截面图。

12.图1b示意性地示出了硅基板的各向异性蚀刻表面。

13.图2是根据一个或多个实施方式的阐述形成双孔传感器的方法的流程图。

14.图3a至图3k示意性地示出了图2阐述的方法的结果的各种方面。

15.图3l示意性地示出了图2阐述的方法的替代实施方式的结果的一个方面。

16.图4a至图4b示意性地示出了图2阐述的方法的替代实施方式的结果的各种方面。

17.图5是根据一个实施方式的在其上形成多个双孔传感器的基板的平面图。

具体实施方式

18.本公开内容的实施方式提供了可用于生物聚合物测序的固态双孔传感器及其制造方法。

19.一般来讲,本文描述的双孔传感器通过在单晶硅基板或单晶硅基板表面中各向异性蚀刻开口以形成至少两个流体贮存器来形成,这两个流体贮存器由设置在两者间的分隔壁彼此分开。阻挡壁的宽度限制了双孔传感器的两个纳米孔可彼此间隔开多近,并且因此决定了可被共捕获在两者间的生物聚合物链的最小长度。

20.典型地,各向异性地蚀刻两个流体贮存器形成横截面为三角形或梯形的分隔壁,参见例如图3d示出的分隔壁314的梯形横截面,其中分隔壁的基部宽于其场(上)表面。换句话说,分隔壁的相对表面倾斜以与基板的场表面的平面形成小于90

°

的角度。在分隔壁的相

对两侧上的倾斜表面如所期望地在传感器的制造期间提高分隔壁的稳定性。与由玻璃基板形成的传感器相比,提高的稳定性允许分隔壁的场表面的宽度更窄,并且流体贮存器更深。这是因为使用常规方法在玻璃基板中形成的分隔壁将沿其高度的至少一部分具有竖直侧面(即,相同的壁厚度)。因此,使用常规方法形成的窄分隔壁将随着其高宽比(高度与宽度比)的增大而发生不期望的屈曲和断裂,这限制了形成更窄的壁和更深的贮存器的制造能力。

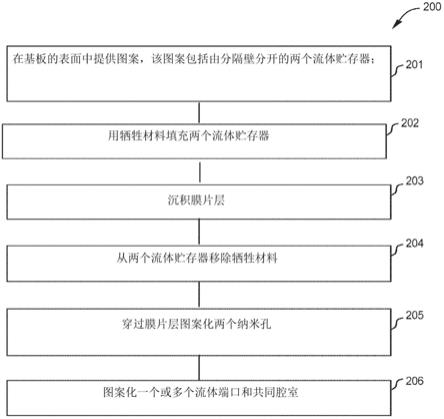

21.有益地,通过本文阐述的方法可实现的分隔壁的更窄的场表面允许两个纳米孔的更紧密的间距,并且因此允许更短的生物聚合物链的测序。此外,通过本文阐述的方法可实现的更深的贮存器提供了更大的横截面积,并且因此提供了对从中流过的离子电流的如所期望地更小的阻力。

22.可用于形成本文的双孔传感器的合适的基板的示例包括通常用于半导体器件制造的那些,诸如n型或p型掺杂单晶硅晶片,或形成未掺杂单晶硅的基板(即,本征单晶硅晶片)。在一些实施方式中,基板是掺杂或未掺杂硅晶片,其上形成有未掺杂单晶硅的外延层。在一些实施方式中,基板具备硅、电绝缘材料(诸如蓝宝石或氧化硅)和硅(通称为绝缘体上硅(soi)基板或soi晶片)的分层堆叠物。当使用时,与由掺杂硅基板形成的传感器相比,未掺杂硅基板、未掺杂硅外延层和soi基板有益地减少由其形成的双孔传感器中的不期望的寄生电容。

23.图1a是示意性示出根据本文描述的实施方式形成的双孔传感器的一部分的特写截面图,该双孔传感器可用于对生物聚合物链进行测序。这里,双孔传感器100具有两个流体贮存器102a、102b和共同腔室104,在使用中,这两个流体贮存器中的每一者具有设置在其中的导电流体,诸如电解液。两个流体贮存器102a、102b由设置在两者间的分隔壁105彼此流体隔离。这里,分隔壁105由下面的单晶硅基板106或单晶基板表面的连续部分形成,该单晶基板表面进一步包括氧化表面层108和设置在氧化表面层108上的氮化硅层110。典型地,图案化下面的单晶硅基板106形成三角形或梯形横截面,诸如图3示出的分隔壁314的梯形横截面。在本文中,氧化表面以形成氧化表面层108消耗来自单晶硅基板的硅的至少一部分。因此,在分隔壁形成为具有梯形横截面形状的实施方式中,氧化单晶硅表面可产生图1a示出的下面的单晶硅基板106的连续部分的三角形横截面形状。在一些实施方式中,氧化表面层108没有深入到单晶硅表面足够远以形成三角形横截面形状。在一些实施方式中,单晶硅表面没有被热氧化,但是在其上可能形成一些原生氧化物。

24.共同腔室104通过膜片层112与两个贮存器102a、102b分开,该膜片层具有从中穿过形成的两个纳米级开口,这里,即第一纳米孔114a和第二纳米孔114b。第一纳米孔114a穿过膜片层112的将第一贮存器102a与共同腔室104分开的部分设置。第二纳米孔114b穿过膜片层112的将第二贮存器102b与共同腔室104分开的部分设置,并且分隔壁将第一贮存器102a和第二贮存器102b彼此分开。

25.与共同腔室的接地电位相比,分别设置在流体贮存器102a、102b中的每一者的源电极116a、116b和设置在共同腔室104中的共同接地电极118用于向流体贮存器102a、102b中的每一者施加单独的电压电位v1、v2,以促进对单个生物聚合物链120的共捕获。一旦通过第一纳米孔114a和第二纳米孔114b实现对生物聚合物链120的共捕获,则在第一纳米孔114a和第二纳米孔114b上、即分别在该第一纳米孔和第二纳米孔的电极116a、116b与共同

接地电极之间施加竞争电压118分别用于在生物聚合物链从第一贮存器102a行进到第二贮存器102b时在该生物聚合物链上形成拔河。通过纳米孔114a、114b中的每一者独立地测量离子电流,并且所得的电流信号模式可用于确定生物聚合物链的单体单元的序列。

26.图1b示意性地示出了使用各向异性蚀刻工艺形成在单晶硅基板122中的梯形横截面形状的开口121和设置在该单晶硅基板的表面上的图案化掩模层128。当暴露于各向异性蚀刻剂时,各向异性蚀刻工艺对基板的硅材料使用固有不同的蚀刻速率,如在该基板的{100}平面表面124和{111}平面表面126之间那样。硅基板122到{100}平面124和{111}平面126中的实际不同的蚀刻速率取决于水性溶液中蚀刻剂的浓度、水性溶液的温度和基板中掺杂剂(如果有的话)的浓度。

27.在一些实施方式中,蚀刻工艺被控制为使得{111}平面表面126和{100}平面表面的蚀刻速率具有在约1:10与约1:200之间的比率,诸如在约1:10与约1:100之间,例如在约1:10和1:50之间或在约1:25和1:75之间)。本文的合适的各向异性湿蚀刻剂的示例包括氢氧化钾(koh)、乙二胺和邻苯二酚(epd)、氢氧化铵(hn4oh)、肼(n2h4)或四甲基氢氧化铵(tmah)的水性溶液。

28.典型地,在单晶硅基板表面处的{100}平面将与基板本体中的{111}平面相汇,以形成54.74

°

的角度α。因此,在本文阐述的实施方式中,在单晶硅基板中限定各向异性地蚀刻的开口的侧壁将与基板的场表面的平面形成约54.74

°

的角度。

29.图2是根据实施方式的阐述形成双孔传感器的方法的流程图。图3a至图3l示意性地示出了根据一个或多个实施方式的方法200的各种活动。

30.在活动201处,方法200包括在基板的表面中提供图案。这里,该图案具备从表面的场凹陷的两个流体贮存器,其中这两个流体贮存器由基板的非凹陷或部分地凹陷部分所形成的阻挡壁分开。在一个实施方式中,在基板表面的表面中提供图案包括在基板的表面上形成图案化掩模层并且使用各向异性蚀刻工艺将蚀刻掩模的图案转移到下面的基板表面。图3a和图3b示出了基板302,该基板上设置有图案化掩模层304。图3a是基板和在其上的掩模的示意性平面图。图3b是沿线a-a截取的图3a的一部分的截面图。

31.这里,图案化掩模层304由与下面的单晶硅基板相比对各向异性蚀刻有选择性的材料形成。合适的掩模材料的示例包括氧化硅(si

x

oy)或氮化硅(si

x

ny)。在本文中,掩模层304具有约100nm或更小的厚度,诸如约50nm或更小或约30nm或更小。这里,掩模层304材料使用光刻和材料蚀刻图案化方法的任何合适的组合来图案化。该图案具备穿过掩模层304设置的第一开口306a和第二开口306b,该第一开口和第二开口彼此间隔开以限定设置在两者间的掩模壁308。这里,开口306a、306b限定一般被掩模材料包围并由掩模壁308分隔的凹陷图案的两个侧面,以及掩模材料的散布在相应的凹陷部中的单独的大体上圆柱形岛状物310。

32.在图3a中,两个开口306a、306b形成大体上对称的“h”形图案,其被掩模壁308分叉。在其他实施方式中,图案可以是任何合适的对称或不对称形状,例如“x”形图案、“ ”形图案、“k”形图案或其中要形成的贮存器将密切地接近以形成具有期望的宽度的分隔壁的任何其他期望的图案。

33.在图3b中,岛状物310a由线a-a一分为二,以横截面示出,岛状物310b在由线a-a限定的区段之后。在基板302的场(上)表面处的掩模壁308的宽度x1和在后续各向异性蚀刻工

艺期间从111平面去除的材料量决定了双纳米孔传感器的两个纳米孔之间的最小间距。这里,宽度x1小于约300nm,诸如小于约250nm、小于约200nm,或者例如小于约180nm。掩模层304进一步包括多个非连续特征作为掩模材料的单独台面或岛状物310,分布在由开口306a、306b中的每一者的壁限定的边界内。

34.将掩模图案转移到基板302的表面典型地包括通过穿过掩模层304的开口306a、306b将其场表面暴露于蚀刻剂来各向异性地蚀刻其单晶硅。在一个实施方式中,各向异性地蚀刻基板302包括将基板表面暴露于各向异性湿蚀刻剂以形成第一贮存器312a和第二贮存器312b(如图3c至图3d所示),每个贮存器具有从基板的场表面凹陷到期望深度d的基部表面。这里,第一贮存器312a和第二贮存器312b中的每一者将在所得的双纳米孔传感器中形成相应流体连接体积。在基板表面被图案化之后,可使用任何合适的方法(诸如通过暴露于磷酸水性溶液)从其去除掩模层304。

35.图3c是基板302的图案化表面的示意性平面图,掩模层304被去除。图3d是沿线b-b截取的图3c的示意性截面图。这里,基板302的图案化表面具备由分隔壁314彼此间隔开的两个流体贮存器312a、312b。流体贮存器312a、312b各自具有在正交于基板302的场表面的方向上测量的最大深度d1。典型地,最大深度d1大于0.1μm,诸如大于0.5μm或大于约1μm,例如在约0.5μm与约2μm之间。在本文中,图案化表面进一步包括对应于上述多个岛状物310的位置的多个支撑结构316。多个支撑结构316中的每一者具有截锥形或棱锥形,其横截面形成梯形,其中支撑结构316的场表面比其基部更窄。这里,单独的支撑结构316在其场表面处的宽度w2在约0.1μm与约5μm之间的范围内,诸如在约0.5μm与约2.5μm之间。多个支撑结构316中的单独的支撑结构316与第一开口306a和第二开口306b的壁间隔开并且彼此间隔开一定距离,该距离适合支撑将跨越贮存器312a、312b的要形成膜片层的部分。在一些实施方式中,支撑结构具有10μm或更小的中心-中心间距,诸如约7.5μm或更小,或者例如约5μm或更小。

36.这里,分隔壁314具有梯形横截面形状,使得其相对表面倾斜以与图案化基板302的场表面的平面形成54.74

°

的角度α。分隔壁314在基板302的场表面处的宽度w1为约200nm或更小,诸如180nm或更小、约160nm或更小、约140nm或更小、约120nm或更小或约100nm或更小。在一些实施方式中,宽度w1在约60nm与约140nm之间的范围内,例如在约80nm与约120nm之间。在其他实施方式中,形成流体贮存器312a、312b的开口被蚀刻,直到分隔壁314具有三角形横截面形状。

37.这里,方法200进一步包括通过热氧化单晶硅表面或通过在该单晶硅表面上沉积介电材料中的一者或两者来在基板302的图案化表面上形成介电层。例如,在一些实施方式中,方法200进一步包括热氧化基板的表面以形成氧化物层,在本文中,即第一介电层318(如图3e所示)。在一些实施方式中,氧化硅表面以提供第一介电层318,该第一介电层的厚度大于约5nm,诸如大于约10nm、大于约20nm或大于约30nm。在一些实施方式中,氧化硅表面以提供第一介电层318,该第一介电层的厚度在约20nm与约80nm之间。典型地,热氧化包括使基板302在约800℃与约1200℃之间的温度下暴露于炉中的蒸汽或分子氧(o2)。由于热氧化物结合了从基板302消耗的硅与供应的氧,因此第一介电层318的约44%的厚度将位于原始硅表面下方,并且第一介电层318的约56%的厚度将在该原始硅表面上方延伸。因此,热氧化硅表面以形成第一介电层318将使壁的宽度增大超过所得的热氧化物的厚度的约1.12

倍。在一些实施方式中,硅表面被热氧化到形成分隔壁的部分具有三角形横截面形状的深度。在一些实施方式中,硅表面被热氧化到形成分隔壁的部分保持其梯形横截面形状的深度。

38.在一些实施方式中,方法200包括在图案化表面上沉积介电材料,诸如第二介电层320(图3e)以覆盖两个流体贮存器312a、312b和场的表面并使其一致。在本文中,第二介电层320包含任何合适的介电材料,诸如氧化硅(si

x

oy)、氮化硅(si

x

ny)、氮氧化硅(sio

x

ny)或iii族、iv族的氧化物、氮化物或氮氧化物、镧系元素、它们的组合或其中两者或更多者的层状堆叠物。例如,在一些实施方式中,第二介电层320包含氧化铝(al2o3)、氮化铝(aln)、氧化钛(tio)、氮化钛(tin)、氧化钽(ta2o5)、氮化钽(tan)或它们的组合。在一些实施方式中,第二介电层320包含非晶硅。

39.有益地,在高频核苷酸检测期间,第二介电层320防止或显著地减少电荷在单晶硅基板302中积聚。因此,第二介电层320显著地减小不期望的背景噪声以提高双孔传感器的检测分辨率。这里,第二介电层320沉积到小于约100nm的厚度,诸如小于约80nm、小于约60nm,或者例如在约20nm与约100nm之间。沉积第二介电层320使壁的宽度增大了第二介电层320的厚度的多于约2倍。

40.典型地,设置在分隔壁314的相对两侧上的第一介电层318或第二介电层320的倾斜表面将与其上设置有介电层318、320中的一者或两者的基板的场表面的平面形成角度θ。这里,角度θ可与约54.74

°

的角度α相同,或者可变化以解决基板302的非均匀氧化来形成第一介电层318和/或第二介电层320的非保形沉积。例如,在一些实施方式中,第一介电层318或第二介电层320的倾斜表面形成在约54.74

°

/-5

°

、或约54.74

°

/-2.5

°

、或约54.74

°

/-1

°

范围内的角度θ。

41.第二介电层320可在后续平面化操作中用作cmp停止层,并且/或者将流体贮存器312a、312b中的导电流体与设置在其下方的单晶硅基板302电绝缘。在一些实施方式中,方法200包括氧化基板302的图案化表面以进行以下一者而非两者:形成第一介电层318或沉积第二介电层320。例如,在一些实施方式中,单晶硅基板302的图案化表面在第二介电层320沉积在其上之前不被热氧化,但是预期发生至少一定程度原生氧化物生长。在不包括沉积第二介电层320的实施方式中,第一介电层318可在后续平面化操作中用作cmp停止层。

42.在活动202处,方法200包括用牺牲材料322填充两个流体贮存器312a、312b。在一些实施方式中,用牺牲材料322填充两个流体贮存器312a、312b包括将牺牲材料层322沉积到图案化基板302上,例如沉积到第一介电层318或第二介电层320(图3f)上。在那些实施方式中,该方法进一步包括从第二介电层320的场表面上方去除牺牲材料322(图3g)以使第二介电层320在分隔壁中的每一者上方的部分暴露。典型地,从第二介电层320的场表面去除牺牲材料322包括使用化学机械平面化(cmp)工艺平面化基板的表面。基板的平面化表面,包括设置在流体贮存器312a、312b(图3e中所示)中的牺牲材料322的平面化表面,将为后续沉积的膜片层提供结构支撑。合适的牺牲材料对下面的第二介电层320有高蚀刻速率和cmp去除速率选择性,并且对要在其上要形成的膜片层112的材料具有高蚀刻速率选择性。合适的牺牲材料的示例包括磷硅酸盐玻璃(psg)、硼磷硅酸盐玻璃(bpsg)、多晶硅、非晶si、铝、碳基膜和聚合物(诸如聚酰亚胺)。

43.在活动203处,方法200包括沉积膜片层324。这里,膜片层324沉积在第二介电层

320的场表面上并沉积到设置在流体贮存器312a、312b中的平面化牺牲材料322上。在一些实施方式中,膜片层324由氮化硅形成。在其他实施方式中,膜片层由另一种合适的介电材料形成,诸如以上阐述的适用于第二介电层320的任何材料。典型地,膜片层324沉积到小于约200nm的厚度,诸如小于约100nm、小于约60nm,例如小于约50nm,或者在约10nm与约50nm之间,诸如在约20nm与约40nm之间。

44.在活动205处,方法200包括从两个流体贮存器312a、312b去除牺牲材料322。在一个实施方式中,去除牺牲材料322包括图案化膜片层324以形成从中穿过的多个排气开口326并且通过多个排气开口326去除牺牲材料322。可使用光刻和材料蚀刻图案化方法的任何合适的组合来图案化膜片层324,诸如在膜片层324上方形成可图案化掩模层、使用光刻技术图案化掩模层以形成在大小和位置上与排气开口的位置对应的开口326并然后蚀刻膜片层324的由穿过掩模层的开口暴露的部分,以形成穿过膜片层324的排气开口326。

45.这里,多个排气开口326中的单独的排气开口具有小于约500nm、小于约100nm或例如小于约50nm的直径。在一些实施方式中,多个排气开口326中的单独的排气开口的直径在约1nm与约500nm之间,诸如在约1nm与约100nm之间、在约1nm与约50nm之间,或者例如在约10nm与约40nm之间。在一些实施方式中,多个排气开口326中的单独的排气开口与其相邻地设置的排气开口326的中心-中心间距小于约500nm,诸如小于约300nm或小于约100nm。多个排气开口326可来自适合在后续牺牲材料去除步骤中排放设置在流体贮存器312a、312b中的挥发或溶解的牺牲材料322的任何期望图案,包括图3h示出的不规则间隔图案。

46.在一个实施方式中,使用基于等离子体的干法蚀刻工艺通过排气开口326去除牺牲材料322。例如,在一个实施方式中,牺牲材料322通过多个排气开口326暴露于合适的蚀刻剂的等离子体激活的自由基物种,诸如卤素基气体(例如。氟或氯基气体)的自由基物种。可用于从流体贮存器312a、312b去除牺牲材料322的示例性系统是可商购自加利福尼亚州圣克拉拉市应用材料公司(applied materials,inc.,of santa clara,calif)的selectra

tm

蚀刻系统,以及来自其他制造商的合适的系统。

47.在另一个实施方式中,去除牺牲材料322包括通过排气开口326将牺牲材料322暴露于对用于形成第二介电层320和膜片层324的一种或多种材料有相对高蚀刻选择性的蚀刻剂。合适的蚀刻剂的示例包括tmah、nh4oh、hf水性溶液和缓冲的hf水性溶液(诸如hf和nh4f的水性溶液),以及无水hf。然后,通过冲洗和干燥基板来从流体贮存器322a、322b去除蚀刻副产物。在一些实施方式中,通过在使用n2气体或异丙醇(ipa)和n2气体混合物干燥基板之前用去离子水冲洗基板来去除蚀刻副产物。在其他实施方式中,诸如在使用无水hf的实施方式中,去除剩余蚀刻副产物包括在小于约40托的真空环境中将基板加热到大于约100℃的温度。

48.在活动205处,方法200包括穿过膜片层324图案化两个纳米孔328a、328b。纳米孔328a、328b可使用任何合适的方法图案化。在一个实施方式中,使用与用于形成如上所述的排气开口326的过程相同或类似的工艺图案化纳米孔328a、328b。例如,在一些实施方式中,排气开口326和纳米孔328a、328b以相同的光刻和材料蚀刻顺序形成。在其他实施方式中,排气开口326和纳米孔328a、328b以任何次序的顺序光刻和材料蚀刻序列形成。在其他实施方式中,纳米孔328a、328b在与用于通过另一个处理操作形成排气开口326的光刻和材料蚀刻序列分开的光刻和材料蚀刻序列中形成。例如,在一些实施方式中,纳米孔328a、328b在

牺牲材料322通过排气开口326被去除之后或在共同腔室被图案化之后形成,如以下在活动206中所述。

49.这里,两个纳米孔328a、328b穿过膜片层324的设置在流体贮存器312a、312b中的每一者上方的相应部分形成,并且因此定位在该流体贮存器附近的分隔壁314的任一侧。典型地,纳米孔328a、328b中的每一者具有小于约100nm的直径,诸如小于约50nm,在约0.1nm与约100nm之间或在约0.1nm与约50nm之间。这里,纳米孔328a、328b彼此间隔开小于约600nm的距离x2,例如小于约550nm、小于约500nm、小于约450nm、小于约400nm,或者在一些实施方式中,小于约300nm。

50.在活动206处,方法200包括图案化一个或多个流体端口338和共同腔室334(图3j)。在一个实施方式中,图案化一个或多个流体端口338和共同腔室334在设置在图案化膜片层324上的外涂层330中形成开口。这里,外涂层330密封膜片层324中的排气开口326,其中不期望流体进入设置在该膜片层下方的贮存器332a、332b。一个或多个流体端口338提供流体到流体贮存器332a、332b的通路以促进将电解液和生物聚合物样品引入其中。外涂层330可使用最小化外涂层材料渗透到排气开口326中的任何合适的材料和方法形成。因此,被选择用于沉积外涂层330的材料和方法应当阻止流体贮存器332a、332b通过排气开口326发生不期望的填充。

51.在一个实施方式中,通过将聚合物前驱物旋涂到图案化膜片层324上并经由暴露于热辐射或电磁辐射固化聚合物前驱物来形成外涂层330。在一些实施方式中,流体端口338和共同腔室334区域然后使用光刻-蚀刻处理序列蚀刻穿过固化聚合物。在其他实施方式中,聚合物前驱物是光敏的,诸如光敏聚酰亚胺前驱物或苯并环丁烯(bcb),并且期望图案直接地在其上暴露。然后将未暴露光敏聚合物前驱物从基板去除以形成流体端口338和共同腔室334区域。在本文中,流体端口338和共同腔室334区域可同时、顺序地或在由介入处理活动分开的处理操作中形成。

52.在另一个实施方式中,外涂层330包括在流体端口338和共同腔室334区域从中穿过形成(图案化)之前或之后层压到膜片层324的表面上的聚合物膜层,诸如聚酰亚胺膜。

53.图3j是根据本文描述的实施方式形成的可用于代替图1a描述的双孔传感器100的双孔传感器300的示意性平面图。图3k是沿线d-d截取的图3j的一部分的截面图。这里,双孔传感器300具备图案化基板301和设置在图案化基板301上的膜片层324。该图案包括由分隔壁314分开的两个凹陷区域。两个凹陷区域中的每一者具有基本上平行于图案化基板301的场(上)表面的平面的一个或多个基部表面303。基部表面303和凹陷区域中的每一者的一个或多个侧壁305(在图3j中以虚线示出)、膜片层324和分隔壁314(其上设置有一个或两个介电层318、320)分别共同地限定第一流体贮存器332a和第二流体贮存器332b。

54.这里,膜片层324与凹陷区域的一个或多个基部表面303间隔开大于约0.5μm的距离d2,诸如大于约1μm、大于约1.5μm、或大于约2μm。凹陷区域和分隔壁314的表面衬有第一介电层318或第二介电层320中的一者或两者。第一纳米孔328a穿过膜片层324的设置在第一流体贮存器332a上方的部分设置,并且第二纳米孔328b穿过膜片层324的设置在第二流体贮存器332b上方的部分设置。在一些实施方式中,膜片层334具有从中穿过形成的多个排气开口326,该排气开口被设置在该膜片层上方的外涂层330密封。外涂层330包括从中穿过设置的开口以限定共同腔室334和设置在相应流体贮存器332a、332b中的每一者上方的一

个或多个流体端口338。共同腔室334通过相应的纳米孔328a、328b与流体贮存器332a、332b中的每一者流体连通。

55.这里,膜片层324的面向贮存器的表面是基本上平面的,并且平行于图案化基板301的场表面。在一些实施方式中,膜片层324通过多个支撑结构316(以及设置在其上的介电衬里)与凹陷区域的基部表面303间隔开。典型地,多个支撑结构316中的单独的支撑结构具有梯形横截面形状。例如,本文的多个支撑结构316和分隔壁314中的一者或两者的表面倾斜,以与膜片层324的面向贮存器332a、332b的表面形成小于90

°

的角度θ,诸如小于约60

°

,或具有约54.74

°

/-5

°

、或约54.74

°

/-2.5

°

、或54.74

°

/-1

°

的范围,例如约54.74

°

。

56.在一些实施方式中,凹陷区域的深度d2与纳米孔间距x2(在图3i中描述)的比率大于约1:1,诸如大于约2:1、大于约3:1、大于约4:1,或者例如大于约5:1。在本文中,深度d2是从图案化基板301的场表面的平面到流体贮存器312a、312b的基部表面303测量的,即,在膜片层324的面向贮存器的表面与基部表面303之间的距离。在一些实施方式中,双孔传感器300进一步包括设置在流体贮存器332a、332b和共同腔室334中的每一者中的电极,诸如图1a描述的电极116a、116b和118。

57.在一些实施方式中,方法200进一步包括在活动208处,在从流体贮存器去除牺牲材料322之前在膜片层324上形成排气开口延伸层332(图3l中所示)。在去除牺牲材料322之前形成排气开口延伸层332可防止当在其上形成外涂层330时对易碎的下面的膜片层324的损坏,例如塌缩。在那些实施方式中,排气开口延伸层332可由适合形成后续外涂层330并且在活动208的描述中阐述的相同的材料和方法形成。一旦排气开口延伸层332沉积到膜片层上,多个开口340就从中穿过形成。多个开口340中的每一者与膜片层324中的对应排气开口延伸层332开口326同轴地设置和/或流体配准。在从中形成开口延伸层332的实施方式中,形成多个开口340的合适方法的示例包括光刻-蚀刻处理序列和光敏聚合物前驱物的直接暴露。在包括排气开口延伸层332的实施方式中,流体端口和共同腔室开口中的一者或两者进一步穿过排气开口延伸层形成以暴露设置在其下方的膜片层。

58.在一些实施方式中,图3j至图3k中描述的双孔传感器300进一步包括以上在图3l中描述的排气开口延伸层332。

59.在另一个实施方式中,基板是绝缘体上硅(soi)基板402(如图4a所示),其具备第一单晶)硅层402a和第二(单晶)硅层402c以及插入在两者间的电绝缘层402b(诸如蓝宝石层或氧化硅层(si

x

oy))。在该实施方式中,基板402的表面、即第二硅层402c使用以上阐述的方法200的一个或多个实施方式被图案化以形成图案化基板405(图4b)。该图案包括两个流体贮存器412a、412b、在其场表面处具有宽度w4的分隔壁414以及形成在第二硅层402c中的多个结构支撑件416。图案化第二硅层402c被热氧化到设置在其下方的电绝缘体层402b的深度,并且可使用方法200的活动202至208或其替代实施方式从中形成双孔传感器。

60.在一些实施方式中,上述方法200包括在第二硅层402c中形成图案并将第二硅层402c热氧化到电绝缘层402b的深度。在一些实施方式中,图案化第二硅层402c没有被氧化到电绝缘层402b的深度。例如,在一些实施方式中,图案化第二硅层402c被热氧化到小于约100μm的深度,诸如小于约50μm、小于25μm,或者例如小于约10μm。

61.在一些实施方式中,图3j至图3k中描述的双孔传感器300具备替代图案化基板301和排气开口延伸层332的图案化基板405中的一者或两者。在一些实施方式中,图案化基板

405进一步包括沉积在其上的介电衬里,诸如上述第二电介质320。

62.典型地,本文提供的方法用于在单个基板(诸如图5示出的单个晶片基板500)上同时制造多个双孔传感器。然后,将晶片基板500分割成单独的管芯以提供多个双孔传感器300。

63.使用本文阐述的方法形成的传感器300的示例性尺寸每侧小于约20mm,诸如小于约15mm或小于约10mm,或者例如在约1mm与约20mm之间。在一些实施方式中,使用本文阐述的实施方式形成的分割的传感器的宽度在约1mm与约100mm之间。

64.本文提供的双孔传感器可包括上文在图1a、图3j至图3k、图3l和图4b中描述的特征中的任一者或组合,包括其替代实施方式。本文提供的双孔传感器可以是分割的,或者可包括形成在单个晶片基板上的多个双孔传感器中的一个,诸如图5描述的单个晶片基板500。

65.有益地,本文描述的方法允许双孔传感器的大批量制造以及改善的质量、可重复性和制造成本。此外,所描述的制造方法允许300nm或更小的孔间间距以有益地增加可使用双孔传感器测序的相对更短的生物聚合物链的数量。

66.尽管前述内容针对的是本公开内容的实施方式,但是在不脱离本公开内容的基本范围的情况下可设想本公开内容的其他和进一步实施方式,并且本公开内容的范围由所附权利要求书的范围确定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。