基于sip堆叠结构的可拆分位宽型ddr模组互联方法

技术领域

1.本发明涉及半导体存储芯片技术领域,具体为一种基于sip堆叠结构的可拆分位宽型ddr模组互联方法。

背景技术:

2.电子装备的迅速发展对系统级封装技术提出了更高的要求,传统的平铺型sip芯片已逐渐被三维堆叠sip芯片所取代,以实现芯片向小尺寸、高可靠、高性能方向发展。半导体存储芯片作为处理器和fpga外设的重要组成部分,多存储芯片封装技术应运而生。

3.目前,以高速ddr sdram为例,3d plus、珠海欧比特、771所等单位已发布32bits或64bits的ddr3模组产品,但数据位宽不可拆分,且多采用平铺形式进行,尺寸较大。申请号为202110140717.6,发明名称为:一种交错堆叠ddr模组及其热分析方法的专利申请,提出了一种交错式堆叠方式和对应散热分析方法,但并未对互联设计方法的相关描述。因此,迫切必要采用多芯片三维堆叠互联技术,将ddr模组设计为可灵活应用的可变位宽小型化存储部件。

技术实现要素:

4.本发明提出一种基于sip堆叠结构的可拆分位宽型ddr模组互联方法,采取的技术方案如下:一种基于sip堆叠结构的可拆分位宽型ddr模组互联方法,包括sip堆叠模组,sip堆叠模组内部的m个芯片拆分为n组ddr子系统,每组ddr子系统的位宽w1为w*m/n,n为大于1的正整数且为m的约数,w为芯片的位宽;每组ddr子系统内,m/n个芯片的数据线直接与基板实现点对点连接,每个数据信号均直接引出至模组封装ball上;每组ddr子系统内,m/n个芯片的地址信号、控制信号和时钟信号与基板实现t型或flyby型拓扑结构互联,按组引出至封装ball上;n组ddr子系统在封装ball上引出n组地址信号、n组控制信号和n组时钟信号;且n组ddr子系统在封装ball上引出n组供电信号;n组ddr子系统在系统应用板上实现与控制器的应用级互联,终端匹配电阻视位宽互联情况放置于信号终端且终端匹配电阻置于系统应用板上。

5.对本发明技术方案的优选,ddr子系统在系统应用时采用拆分位宽模式,则n个ddr子系统需对应放置n组终端匹配电阻于信号末端。

6.对本发明技术方案的优选,ddr子系统在系统应用时采用级联位宽模式,则n个ddr子系统级联后需对应放置1组终端匹配电阻于信号末端。

7.对本发明技术方案的优选,sip堆叠模组包括m个ddr裸芯 、一个ddr模组基板和一个封装腔体,m个ddr裸芯堆叠而成,m个ddr裸芯的堆叠结构配置在一个ddr模组基板上,m个ddr裸芯与一个ddr模组基板之间互联,并封装于一个封装腔体内。

8.对本发明技术方案的优选,m个ddr裸芯的堆叠结构为垂直堆叠结构、左右交错堆叠或十字交叉堆叠结构。

9.对本发明技术方案的优选,m个ddr裸芯与ddr模组基板之间的互联方式采用但不限于wirebond打线形式。

10.对本发明技术方案的优选,m个ddr裸芯采用rdl预处理形式将pad信号引出至裸芯单侧或两侧。

11.对本发明技术方案的优选,系统应用板为系统pcb板或基板。

12.本发明与现有技术相比的有益效果是:本发明与现有ddr模组将所有ddr裸芯作为一个整体进行互联设计相比,该设计方法的优点在于:将1个模组分为若干个ddr子系统进行互联设计,堆叠结构是指但不限于交错式堆叠或tsv工艺堆叠结构,该发明一方面解决了位宽不可拆分问题,在保留现有ddr模组功能前提下,可将高位宽的ddr模组拆分为多个低位宽的小模组使用,增加了用户使用灵活性,另一方面,终端匹配电阻无需采用ipd排阻或分立形式放置在ddr模组内部,而是放置在pcb板上,减少了堆叠结构带来的基板拓扑设计难度,降低了基板生产成本,提高了信号完整性性能。

附图说明

13.图1为实施例的64位ddr模组的堆叠结构一的示意图。

14.图2为实施例的64位ddr模组的堆叠结构二的示意图。

15.图3为实施例的64位ddr模组的堆叠结构三的示意图。

16.图4为实施例的64位ddr模组的堆叠结构四的示意图。

17.图5为实施例的64位ddr模组互联结构的信号引出结构的示意图。

18.图6为实施例的m=4,n=2时的64位ddr模组拆分2个32位系统对应的地址线互联结构的示意图。

19.图7为实施例的m=4,n=2时的64位ddr模组拆分2个32位系统对应的数据线互联结构的示意图。

20.图8为实施例的m=4,n=2时的64位ddr模组级联1个64位系统对应的地址线互联结构的示意图。

21.图9为实施例的m=4,n=2时的64位ddr模组级联1个64位系统对应的数据线互联结构的示意图。

具体实施方式

22.下面对本发明技术方案进行详细说明,但是本发明的保护范围不局限于所述实施例。

23.为使本发明的内容更加明显易懂,以下结合附图1-图9和具体实施方式做进一步的描述。

24.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅用以解释本发明,并不用于限定本发明。

25.本实施例的具体实施方式,提出的基于sip堆叠结构的可拆分位宽型ddr模组互联方法,包括sip堆叠模组,sip堆叠模组内部的m个芯片拆分为n组ddr子系统,每组ddr子系统

的位宽w1为w*m/n,n为大于1的正整数且为m的约数,w为芯片的位宽;每组ddr子系统内,m/n个芯片的数据线直接与基板实现点对点连接,每个数据信号均直接引出至模组封装ball上;每组ddr子系统内,m/n个芯片的地址信号、控制信号和时钟信号与基板实现t型或flyby型拓扑结构互联,按组引出至封装ball上;n组ddr子系统在封装ball上引出n组地址信号、n组控制信号和n组时钟信号;且n组ddr子系统在封装ball上引出n组供电信号;n组ddr子系统在系统应用板上实现与控制器的应用级互联,终端匹配电阻视位宽互联情况放置于信号终端且终端匹配电阻置于系统应用板上。

26.如图1、2、3和4所示,sip堆叠模组包括m个ddr裸芯 、一个ddr模组基板和一个封装腔体,m个ddr裸芯堆叠而成,m个ddr裸芯的堆叠结构配置在一个ddr模组基板上,m个ddr裸芯与一个ddr模组基板之间互联,并封装于一个封装腔体内。m个ddr裸芯与ddr模组基板之间的互联方式采用但不限于wirebond打线形式。m个ddr裸芯采用rdl预处理形式将pad信号引出至裸芯单侧或两侧。

27.本实施例中,sip堆叠模组内,如图1和2所示,ddr裸芯左右交错堆叠,rdl将每颗ddr裸芯的pad引到die的一侧后,信号只从一侧打线,无需考虑间隔层的出线空间,中间通过fill胶粘接,分两种情况:1)、数据、地址、控制线均点对点打线至基板再进行基板互联设计,如图1所示。2)数据线均点对点打线至基板再进行互联设计,同侧高“层”的地址/控制线先打线至对应低“层”的裸芯bump互联成flyby(菊花链)拓扑后在统一打线至基板进行互联设计,如图2所示。

28.本实施例中,sip堆叠模组内,rdl将每颗ddr裸芯的pad引到die的两侧后,信号从两侧打线。如图3所示,ddr裸芯直接垂直堆叠,左右出线,需考虑相邻层的出线空间,中间通过垫片粘接,所有出线至基板再进行互联。如图4所示,ddr裸芯十字交叉堆叠,ddr裸芯左右前后都出线;这种结构,仅需考虑间隔层的出线空间,中间通过fill胶粘接。

29.如图1、2、3和4所示,本实施例中三维堆叠信号互联工艺主要分为wirebond打线(金丝打线)和tsv硅转接基板互联两种,同时sip堆叠模组内的堆叠结构可以但不限于左右交错堆叠(图1和2)、直接垂直堆叠(图3)和十字交叉堆叠(图4)。这里需要说明的是,本实施例中提及的三维堆叠信号互联工艺,均为本领域内技术人员已知。

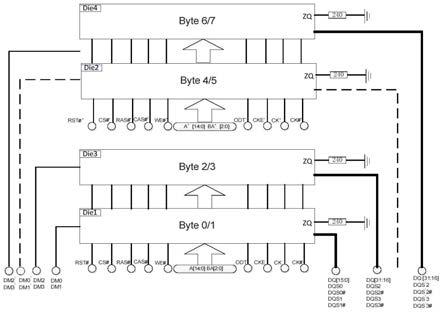

30.如图5所示,本实施例中,以64位ddr模组为例,在设计时考虑到拆分为两个32位ddr模组应用场景,即设计两个模组拥有独立的数据、地址、控制线,die1和die3为一组,出a[14:0],d[31:0]等,die2和die4为一组出a’[14:0],d’[31:0]等。

[0031]

本具体实施方式内,系统应用板为系统pcb板或基板。ddr子系统在系统应用时采用拆分位宽模式,则n个ddr子系统需对应放置n组终端匹配电阻于信号末端。

[0032]

如图6和7所示,ddr子系统在系统应用时采用拆分位宽模式,举例如下:以m=4,n=2时的64位ddr模组拆分2个32位子系统,进一步说明:拆分应用时的系统应用板。

[0033]

如图6所示,以地址线应用为例,当系统使用两个32位控制器(控制器1和控制器2)时,在系统应用板上将控制器1的地址线a[14:0]接模组的a[14:0],终端匹配电阻放置在a[14:0]各自末端,控制器2的a[14:0]接模组的a’[14:0],终端匹配电阻放置在a’[14:0]各自末端。

[0034]

如图7所示,以数据线应用为例,当系统使用两个32位控制器(控制器1和控制器2)时,在系统应用板上将控制器1的数据线d[31:0]接模组的d[31:0],控制器2的d[31:0]接模

组的d’[31:0]。

[0035]

本具体实施方式内,系统应用板为系统pcb板或基板。ddr子系统在系统应用时采用级联位宽模式,则n个ddr子系统级联后需对应放置1组终端匹配电阻于信号末端。

[0036]

如图8和9所示,ddr子系统在系统应用时采用级联位宽模式,举例如下:以m=4,n=2时的64位ddr模组级联1个64位系统,进一步说明:级联应用时的系统应用板。

[0037]

如图8所示,以地址线应用为例,当系统使用一个64位控制器时,在系统应用板上将控制器的地址线a[14:0]、模组a[14:0]、a’[14:0]通过flyby拓扑结构互联,终端匹配电阻放置在a’[14:0]末端。

[0038]

如图9所示,以数据线应用为例,当系统使用一个64位控制器时,在系统应用板上将控制器的数据线d[31:0]通过点对点拓扑结构接模组的d[31:0],控制器的d[63:32]接模组的d’[31:0]。

[0039]

以上实施例仅为说明本发明的技术思想,不能以此限定本发明的保护范围,凡是按照本发明提出的技术思想,在技术方案基础上所做的任何改动,均落入本发明保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。