具有噪声消除的混频器电路

1.本技术要求2020年9月18日提交的美国专利申请第17/026056号的优先权,该申请据此全文以引用方式并入本文。

技术领域

2.本公开整体涉及电子设备,并且更具体地涉及具有无线通信电路的电子设备。

背景技术:

3.电子设备常具备无线通信能力。具有无线通信能力的电子设备具有带有一个或多个天线的无线通信电路。无线通信电路中的无线接收器电路使用天线来接收射频信号。

4.由天线接收的信号通过收发器被馈送,该收发器通常包括用于解调射频信号的混频器。设计用于电子设备的令人满意的混频器可能是有挑战性的。

技术实现要素:

5.电子设备可包括无线通信电路。无线通信电路可包括:天线;收发器,该收发器被配置为从天线接收射频信号并且生成对应的基带信号;以及基带处理器,该基带处理器被配置为从收发器接收基带信号。

6.本公开的一方面提供了混频器电路。混频器电路可包括输入端口,该输入端口被配置为从天线接收射频信号;输出端口,基于射频信号在该输出端口上生成基带信号;振荡器,该振荡器被配置为生成第一振荡器信号,不同于第一振荡器信号的第二振荡器信号,以及相对于第二振荡器信号反相的第三振荡器信号;第一开关,该第一开关具有耦合到输入端口的输入端子,耦合到输出端口的输出端子,以及被配置为接收第一振荡器信号的控制端子;第二开关,该第二开关具有耦合到第一开关的输出端子的输入端子,耦合到输出端口的输出端子,以及被配置为接收第二振荡器信号的控制端子;以及振荡器相位噪声消除电容器,该振荡器相位噪声消除电容器具有耦合到第二开关的输入端子的第一端子以及被配置为接收第三振荡器信号的第二端子。振荡器相位噪声消除电容器可以是金属-氧化物-半导体电容器、金属-绝缘体-金属电容器或金属-氧化物-金属电容器。

7.本公开的一方面提供了一种操作混频器的方法。该方法可包括使用输入端口来接收射频信号;使用振荡器来生成第一振荡器信号,不同于第一振荡器信号的第二振荡器信号,以及相对于第二振荡器信号反相的第三振荡器信号;使用第一开关从输入端口接收射频信号并且接收第一振荡器信号;使用第二开关从第一开关接收信号,接收第二振荡器信号,并且基于射频信号生成对应的基带信号;以及使用振荡器相位噪声消除器来接收第三振荡器信号并降低与第二振荡器信号相关联的相位噪声。该方法还可包括使用触发器来生成第一输出信号和第二输出信号,使用第一系列缓冲器来接收第一输出信号并且生成第一振荡器信号,以及使用第二系列缓冲器来接收第二输出信号并生成第二振荡器信号。

8.本公开的一方面提供了一种电子设备,该电子设备包括天线,该天线被配置为接收射频信号;基带处理器,该基带处理器被配置为接收基于射频信号生成的基带信号;振荡

器,该振荡器被配置为生成振荡器信号和相对于振荡器信号反相的反相振荡器信号;以及混频器,该混频器被配置为从天线接收射频信号并且生成基带信号。混频器可包括晶体管,该晶体管具有被配置为接收振荡器信号的栅极端子;以及电容器,该电容器具有直接连接到晶体管的第一端子和被配置为接收反相振荡器信号的第二端子。振荡器可包括触发器,该触发器具有第一输出端和第二输出端;第一多个缓冲器,该第一多个缓冲器耦合到第一输出端并且被配置为生成振荡器信号中的第一振荡器信号;以及第二多个缓冲器,该第二多个缓冲器耦合到第二输出端并且被配置为生成振荡器信号中的第二振荡器信号。振荡器还可包括第一反相器,该第一反相器耦合到第一多个缓冲器中的最后缓冲器;以及第二反相器,该第二反相器耦合到第二多个缓冲器中的最后缓冲器。第一反相器可被配置为生成反相振荡器信号中的第一反相振荡器信号。第二反相器可被配置为生成反相振荡器信号中的第二反相振荡器信号。

附图说明

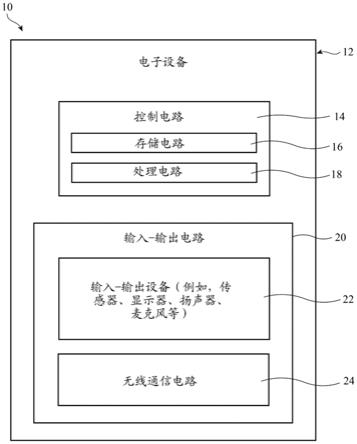

9.图1是根据一些实施方案的具有无线通信电路的例示性电子设备的图示。

10.图2是根据一些实施方案的具有收发器电路的例示性无线通信电路的图示。

11.图3是根据一些实施方案的例示性混频器电路的图示。

12.图4是根据一些实施方案的例示性本地振荡器的图示。

13.图5是根据一些实施方案的耦合到振荡器相位噪声消除电容器的例示性混频器开关的图示。

14.图6是根据一些实施方案的被配置为生成同相输出信号的混频器电路的一部分的电路图。

15.图7是根据一些实施方案的被配置为生成正交相输出信号的混频器电路的一部分的电路图。

16.图8是根据一些实施方案的被配置为生成用于控制混频器电路的振荡器信号的例示性本地振荡器的电路图。

17.图9是示出根据一些实施方案的例示性振荡器信号波形的图示。

18.图10是示出根据一些实施方案的执行振荡器相位噪声消除可如何减小噪声系数的图示。

19.图11是根据一些实施方案的在操作图2至图8所示类型的混频器电路中涉及的例示性步骤的流程图。

具体实施方式

20.电子设备,诸如图1的电子设备10可具备无线电路。无线电路可包括用于将射频信号下变频到基带的无源混频器电路。无源混频器电路包括混频器和本地振荡器。本地振荡器生成振荡器输出信号以控制混频器中的一个或多个开关。无源混频器电路可设置有振荡器相位噪声消除部件,该振荡器相位噪声消除部件被配置为消除可经由寄生耦合到混频器的输入端的相位噪声。振荡器相位噪声消除部件可以是被配置为接收反相振荡器输出信号的电容器结构。以这种方式布置和操作,无源混频器电路可生成具有改善的噪声系数性能的基带信号。

21.图1的电子设备10可以是:计算设备,诸如膝上型计算机、台式计算机、包含嵌入式计算机的计算机监视器、平板电脑、蜂窝电话、媒体播放器或者其他手持式或便携式电子设备;较小的设备,诸如腕表设备、挂式设备、耳机或听筒设备、嵌入在眼镜中的设备;或者佩戴在用户头部上的其他装备;或者其他可佩戴式或微型设备、电视机、不包含嵌入式计算机的计算机显示器、游戏设备、导航设备、嵌入式系统(诸如其中具有显示器的电子装备安装在信息亭或汽车中的系统)、连接无线互联网的语音控制的扬声器、家庭娱乐设备、遥控设备、游戏控制器、外围用户输入设备、无线基站或接入点、实现这些设备中的两个或更多个设备的功能的装备;或者其他电子装备。

22.如图1中的示意图所示,设备10可包括位于电子设备外壳诸如外壳12上或其内的部件。外壳12(有时可以称为壳体)可由塑料、玻璃、陶瓷、纤维复合材料、金属(例如,不锈钢、铝、金属合金等)、其他合适的材料、或这些材料的组合形成。在一些情况下,外壳12的部分或全部可由电介质或其他低电导率材料(例如,玻璃、陶瓷、塑料、蓝宝石等)形成。在其他情况下,外壳12或构成外壳12的结构中的至少一些结构可由金属元件形成。

23.设备10可包括控制电路14。控制电路14可包括存储装置,诸如存储电路16。存储电路16可包括硬盘驱动器存储装置、非易失性存储器(例如,被配置为形成固态驱动器的闪存存储器或其他电可编程只读存储器)、易失性存储器(例如,静态随机存取存储器或动态随机存取存储器)等。存储电路16可包括集成在设备10内的存储装置和/或可移动存储介质。

24.控制电路14可包括处理电路,诸如处理电路18。处理电路18可用于控制设备10的操作。处理电路18可包括一个或多个微处理器、微控制器、数字信号处理器、主机处理器、基带处理器集成电路、专用集成电路、中央处理单元(cpu)等。控制电路14可被配置为使用硬件(例如,专用硬件或电路)、固件和/或软件在设备10中执行操作。用于在设备10中执行操作的软件代码可以存储在存储电路16(例如,存储电路16可以包括存储软件代码的非暂态(有形)计算机可读存储介质)上。该软件代码可有时被称为程序指令、软件、数据、指令、或代码。存储在存储电路16上的软件代码可由处理电路18来执行。

25.控制电路14可用于运行设备10上的软件,诸如卫星导航应用程序、互联网浏览应用程序、互联网语音协议(voip)电话呼叫应用程序、电子邮件应用程序、媒体回放应用程序、操作系统功能等。为了支持与外部装备进行交互,控制电路14可用于实现通信协议。可使用控制电路14实现的通信协议包括:互联网协议、无线局域网(wlan)协议(例如,ieee 802.11协议——有时称为)、用于其他短距离无线通信链路的协议诸如协议或其他无线个人区域网(wpan)协议、ieee 802.11ad协议(例如,超宽带协议)、蜂窝电话协议(例如,3g协议、4g(lte)协议、5g新无线电(nr)协议等)、mimo协议、天线分集协议、卫星导航系统协议(例如,全球定位系统(gps)协议、全球导航卫星系统(glonass)协议等)、基于天线的空间测距协议(例如,在毫米波频率和厘米波频率下传送的信号的无线电探测与测距(radar)协议或其他期望的距离检测协议)或任何其他期望的通信协议。每种通信协议可与对应的无线电接入技术(rat)相关联,该无线电接入技术指定用于实现该协议的物理连接方法。

26.设备10可包括输入-输出电路20。输入-输出电路20可包括输入-输出设备22。输入-输出设备22可用于允许将数据供应给设备10并且允许将数据从设备10提供给外部设

备。输入-输出设备22可包括用户接口设备、数据端口设备和其他输入-输出部件。例如,输入-输出设备22可包括触摸传感器、显示器、发光部件诸如没有触摸传感器能力的显示器、按钮(机械、电容、光学等)、滚轮、触摸板、小键盘、键盘、麦克风、相机、按钮、扬声器、状态指示器、音频插孔和其他音频端口部件、数字数据端口设备、运动传感器(检测运动的加速度计、陀螺仪和/或罗盘)、电容传感器、接近传感器、磁传感器、力传感器(例如,耦合到显示器以检测施加到显示器的压力的力传感器)等。在一些配置中,键盘、耳机、显示器、指向设备诸如触控板、鼠标、电子铅笔(例如,手写笔)和操纵杆以及其他输入-输出设备可使用有线或无线连接来耦合到设备10(例如,输入-输出设备22中的一些可为经由有线或无线链路耦合到设备10的主处理单元或其他部分的外围设备)。

27.输入-输出电路24可包括用于无线地传送射频信号的无线通信电路,诸如无线通信电路34(有时在本文中称为无线电路24)。虽然为了清楚起见,控制电路14被示出为与无线通信电路24分开,但是无线通信电路24可包括处理电路和/或存储电路,该处理电路形成处理电路18的一部分,该存储电路形成控制电路14的存储电路16的一部分(例如,控制电路14的各部分可在无线通信电路24上实现)。例如,控制电路14(例如,处理电路18)可包括基带处理器电路或形成无线通信电路24的一部分的其他控制部件。

28.无线通信电路24可包括由一个或多个集成电路形成的射频(rf)收发器电路、被配置为对上行链路射频信号(例如,由设备10向外部设备传输的射频信号)进行放大的功率放大器电路、被配置为对下行链路射频信号(例如,由设备10从外部设备接收到的射频信号)进行放大的低噪声放大器、无源射频部件、一个或多个天线、传输线,以及用于处理射频无线信号的其他电路。也可使用光(例如,使用红外通信)来发送无线信号。

29.无线电路24可包括用于处理各种射频通信频带中的射频信号的传输和/或接收的射频收发器电路。例如,射频收发器电路可处理:无线局域网(wlan)通信频带,诸如2.4ghz和5ghz(ieee 802.11)频带;无线个人局域网(wpan)通信频带,诸如2.4ghz通信频带;蜂窝电话通信频带,诸如蜂窝低频带(lb)(例如,600mhz至960mhz)、蜂窝低中频带(lmb)(例如,1400mhz至1550mhz)、蜂窝中频带(mb)(例如,从1700mhz至2200mhz)、蜂窝高频带(hb)(例如,从2300mhz至2700mhz)、蜂窝超高频带(uhb)(例如,从3300mhz至5000mhz)或介于约600mhz和约5000mhz之间的其他蜂窝通信频带(例如,3g频带、4g lte频带、低于10ghz的5g新无线电频率范围1(fr1)频带、在20ghz和60ghz之间的毫米波长和厘米波长下的5g新无线电频率范围2(fr2)频带等);近场通信(nfc)频带(例如,在13.56mhz下);卫星导航频带(例如,在1575mhz的l1全球定位系统(gps)频带、在1176mhz的l5 gps频带、全球导航卫星系统(glonass)频带、北斗导航卫星系统(bds)频带等);由ieee 802.15.4协议和/或其他uwb通信协议支持的超宽带(uwb)通信频带(例如,在6.5ghz的第一uwb通信频带和/或在8.0ghz的第二uwb通信频带);和/或任何其他期望的通信频带。由此射频收发器电路处理的通信频带在本文中有时可被称为频带或简称为“带”并且可跨对应的频率范围。一般来讲,无线电路24内的射频收发器电路可覆盖(处理)任何期望的感兴趣的频带。

30.图2是示出无线电路24内的例示性部件的图示。如图2所示,无线电路24可包括基带处理器诸如基带处理器26、射频(rf)收发器电路诸如射频收发器28、射频前端电路诸如

射频前端模块(fem)40,以及天线42。基带处理器26可通过基带路径34耦合到收发器28。收发器28可经由射频传输线路径36耦合到天线42。射频前端模块40可插置在收发器28与天线42之间的射频传输线路径36上。

31.在图2的示例中,为了清楚起见,无线电路24被示出为仅包括单个基带处理器26、单个收发器28、单个前端模块40和单个天线42。一般来讲,无线电路24可包括任何期望数量的基带处理器26、任何期望数量的收发器36、任何期望数量的前端模块40和任何期望数量的天线42。每个基带处理器26可通过相应基带路径34耦合到一个或多个收发器28。每个收发器28可包括被配置为向天线42输出上行链路信号的发射器电路30,可包括被配置为从天线42接收下行链路信号的接收器电路32,并且可通过相应射频传输线路径36耦合到一个或多个天线42。每个射频传输线路径36可具有插置在其上的相应前端模块40。如果需要,两个或更多个前端模块40可插置在同一射频传输线路径36上。如果需要,可在其上没有插置任何前端模块的情况下实现无线电路24中的射频传输线路径36中的一个或多个射频传输线路径。

32.射频传输线路径36可耦合到天线42上的天线馈电部。天线馈电部可例如包括正天线馈电端子和接地天线馈电端子。射频传输线路径36可具有正传输线信号路径,该正传输线信号路径耦合到天线42上的正天线馈电端子。射频传输线路径36可具有接地传输线信号路径,该接地传输线信号路径耦合到天线42上的接地天线馈电端子。该示例仅仅是例示性的,并且一般来讲,天线42可使用任何期望的天线馈电方案来馈电。如果需要,天线42可具有耦合到一个或多个射频传输线路径36的多个天线馈电部。

33.射频传输线路径36可包括用于路由设备10(图1)内的射频天线信号的传输线。设备10中的传输线可包括同轴电缆、微带传输线、带状线传输线、边缘耦合的微带传输线、边缘耦合的带状线传输线、由这些类型的传输线的组合形成的传输线等。设备10中的传输线(诸如射频传输线路径36中的传输线)可集成到刚性和/或柔性印刷电路板中。在一种合适的布置中,射频传输线路径(诸如射频传输线路径36)还可包括传输线导体,这些传输线导体集成在多层层压结构(例如,在没有介入粘合剂的情况下层压在一起的导电材料(诸如铜)和电介质材料(诸如树脂)的层)内。如果需要,多层层压结构可在多个维度(例如,二维或三维)上折叠或弯曲,并且可在弯曲之后保持弯曲或折叠形状(例如,多层层压结构可被折叠成特定的三维结构形状以围绕其他设备部件布线并且可为足够刚性的以在折叠之后保持其形状而不用加强件或其他结构保持在适当的位置)。层压结构的所有多个层可以在没有粘合剂的情况下分批层压在一起(例如,在单个压制过程中)(例如,与进行多个压制过程以将多个层用粘合剂层压在一起相反)。

34.在执行无线传输时,基带处理器26可通过基带路径34向收发器28提供基带信号。收发器28还可包括用于将从基带处理器26接收的基带信号转换为对应射频信号的电路。例如,收发器电路28可包括用于在通过天线42的传输之前将基带信号上变频(或调制)为射频的混频器电路50。收发器电路28还可包括用于在数字域与模拟域之间转换信号的数模转换器(dac)电路和/或模数转换器(adc)电路。收发器28可包括发射器部件以经由射频传输线路径36和前端模块40通过天线42传输射频信号。天线42可通过将射频信号辐射到自由空间中来将射频信号传输到外部无线装备。

35.在执行无线接收时,天线42可从外部无线装备接收射频信号。可将接收到的射频

信号经由射频传输线路径36和前端模块40传送到收发器28。收发器28可包括用于将接收到的射频信号转换为对应基带信号的电路。例如,收发器28可将混频器电路50用于在将接收到的信号通过基带路径34传送到基带处理器26之前将接收到的射频信号下变频(或解调)为基带频率。混频器电路50可以包括振荡器电路,诸如本地振荡器52。本地振荡器52可生成振荡器信号,混频器电路50可将该振荡器信号用于将发射信号从基带频率调制到射频并且/或者将所接收的信号从射频解调到基带频率。

36.前端模块(fem)40可包括对通过射频传输线路径36传送(传输和/或接收)的射频信号进行操作的射频前端电路。前端模块可例如包括前端模块(fem)部件,诸如射频滤波器电路44(例如,低通滤波器、高通滤波器、陷波滤波器、带通滤波器、复用电路、双工器电路、双讯器电路、三工器电路等)、切换电路46(例如,一个或多个射频开关)、射频放大器电路48(例如,一个或多个功率放大器和一个或多个低噪声放大器)、阻抗匹配电路(例如,有助于使天线42的阻抗与射频传输线36的阻抗匹配的电路)、天线调谐电路(例如,调节天线42的频率响应的电容器、电阻器、电感器和/或开关的网络)、射频耦合器电路、电荷泵电路、功率管理电路、数字控制和接口电路,和/或对由天线42传输和/或接收的射频信号进行操作的任何其他期望的电路。可将每个前端模块部件安装到公共(共享)衬底,诸如刚性印刷电路板衬底或柔性印刷电路衬底。如果需要,各种前端模块部件还可被集成到单个集成电路芯片中。

37.滤波器电路44、切换电路46、放大器电路48以及其他电路可插置在射频传输线路径36内,可结合到fem 40中,和/或可结合到天线42中(例如,以支持天线调谐、以支持在期望频带中的操作等)。可(例如,使用控制电路14)调节这些部件(在本文中有时称为天线调谐部件)以随时间调节天线42的频率响应和无线性能。

38.收发器28可与前端模块40分开。例如,可在另一个衬底诸如设备10的主逻辑板、刚性印刷电路板或并非前端模块40的一部分的柔性印刷电路上形成收发器28。虽然为了清楚起见,在图1的示例中,控制电路14被示出为与无线电路24分开,但是无线电路24可包括处理电路和/或存储电路,该处理电路形成处理电路18的一部分,该存储电路形成控制电路14的存储电路16的一部分(例如,控制电路14的各部分可在无线电路24上实现)。例如,基带处理器26和/或收发器28的部分(例如,收发器28上的主机处理器)可形成控制电路14的一部分。控制电路14(例如,基带处理器26上形成的控制电路14的部分、收发器28上形成的控制电路14的部分和/或与无线电路24分开的控制电路14的部分)可提供控制前端模块40的操作的控制信号(例如,通过设备10中的一个或多个控制路径)。

39.收发器电路28可包括处理wlan通信频带(例如,(ieee 802.11)或其他wlan通信频带)诸如2.4ghz wlan频带(例如,从2400mhz至2480mhz)、5ghz wlan频带(例如,从5180mhz至5825mhz)、6e频带(例如,从5925mhz至7125mhz)和/或其他频带(例如,从1875mhz至5160mhz)的无线局域网收发器电路;处理2.4ghz 频带或其他wpan通信频带的无线个人区域网收发器电路;处理蜂窝电话频带(例如,从约600mhz至约5ghz的频带、3g频带、4g lte频带、低于10ghz的5g新无线电频率范围1(fr1)频带、介于20ghz和60ghz之间的5g新无线电频率范围2(fr2)频带等)的蜂窝电话收发器电路;处理近场通信频带(例如,在13.56mhz下)的近场通信(nfc)收发器电路;处理卫星导航频带(例如,从1565mhz至1610mhz的gps频带、全球导航卫星系统(glonass)频带、北斗导航卫星系统

(bds)频带等)的卫星导航接收器电路;使用ieee 802.15.4协议和/或其他超宽带通信协议来处理通信的超宽带(uwb)收发器电路;和/或用于覆盖任何其他期望的感兴趣通信频带的任何其他期望的射频收发器电路。

40.无线电路24可包括一个或多个天线,诸如天线42。可使用任何期望的天线结构来形成天线42。例如,天线42可为具有谐振元件的天线,该天线由环形天线结构、贴片天线结构、倒f形天线结构、隙缝天线结构、平面倒f形天线结构、螺旋天线结构、单极天线、偶极、这些设计的混合等形成。两个或更多个天线42可被布置成一个或多个相控天线阵列(例如,用于在毫米波频率下传送射频信号)。寄生元件可被包括在天线42中以调节天线性能。天线42可设置有导电腔,该导电腔支撑天线42的天线谐振元件(例如,天线42可为背腔天线,诸如背腔隙缝天线)。

41.如上所述,混频器电路50可用于将射频信号下变频到基带频率以用于解调。图3是例示性混频器电路50的图示。如图3所示,混频器电路50可包括输入端口rfin、第一混频器部分50-i、第二混频器部分50-q和相关联的本地振荡器(lo)52。输入端口rfin被配置为从前端模块40接收射频信号。例如,输入端口rfin可被配置为从前端模块40内的低噪声放大器接收射频。又如,输入端口rfin可被配置为从平衡-不平衡转换器接收射频信号。又如,输入端口rfin可被配置为从其他前端模块部件或直接从天线42接收射频信号。

42.振荡器52可被配置为生成第一振荡器输出信号和相对于第一振荡器输出信号相移90

°

的第二振荡器输出信号。第一振荡器输出信号被馈送到第一混频器部分50-i。第一混频器部分50-i可以将在输入端口rfin处接收的射频输入信号与第一振荡器输出信号混频,以生成对应的同相信号i(n)。第二混频器部分50-q可将在rfin端口处接收的射频输入信号与第二振荡器输出信号混频,以生成对应的正交相信号q(n)。同相信号i(n)和正交相信号q(n)可在混频器的输出端处生成,它们可统称为基带信号,然后被馈送到基带处理器26。

43.图4是本地振荡器52的框图。如图4所示,振荡器52可以包括电压控制振荡器诸如电压控制振荡器(vco)60,一个或多个数字触发器诸如数字触发器62,以及相关联的缓冲电路诸如缓冲器64。电压控制振荡器60可输出周期信号以控制数字触发器62。触发器62可以是用于基于由电压控制振荡器60提供的周期信号生成时钟信号的任何基于锁存器的数字电路。由触发器62生成的时钟信号可被馈送通过缓冲电路64的相应链以生成一个或多个振荡器输出信号66。

44.如图3的示例所示,振荡器52可生成具有不同相位的至少两个不同振荡器输出信号(参见例如,0

°

lo相位信号和90

°

lo相位信号)。又如,振荡器52可生成至少四个不同的振荡器输出信号(例如,0

°

lo相位信号、90

°

lo相位信号、180

°

lo相位信号和270

°

lo相位信号)。一般来讲,振荡器52可生成任何合适数量的lo相位(例如,两个或更多个lo相位、三个或更多个lo相位、不止四个lo相位、四个至十个lo相位、不止十个lo相位等)。在实践中,数字触发器62和缓冲电路64易受上升和下降时间变化,随机相移和信号抖动的影响,这些都会导致可由本地振荡器引入的随机相位噪声以降低整个混频器电路的噪声系数性能。

45.混频器电路50可以是有源混频器或无源混频器。有源混频器不断消耗功率,但可用于提供增益。无源混频器也可提供增益,但是可以实现改善的线性度并且比有源混频器消耗更少的功率。常规无源混频器可能遭受由于与本地振荡器相关联的相位噪声(例如,由于在生成各种lo相位时与数字触发器和缓冲电路相关联的噪声)而导致的噪声系数劣化。

如果不小心,则由本地振荡器生成的不同振荡器信号可通过寄生耦合到无源混频器的输入端口,然后输入端口可与本地振荡器频率自混频。本地振荡器信号的这种不期望的耦合(本文中有时称为本地振荡器相位噪声、振荡器相位噪声或lo相位噪声)可导致基带处的噪声劣化。这种噪声劣化在更易受闪烁噪声影响的先进互补金属-氧化物-半导体(cmos)过程处加剧。

46.图5是例示性无源混频器电路50的图示,该无源混频器电路设置有振荡器相位噪声消除部件以消除(补偿)可能无意中耦合到无源混频器的输入端口的lo相位。如图5所示,混频器电路50可包括至少一个无源混频器开关,诸如开关51。开关51可例如被实现为晶体管,诸如n沟道金属-氧化物-半导体(nmos)晶体管。这仅是例示性的。又如,开关51可被实现为p沟道金属-氧化物-半导体(pmos)晶体管。一般来讲,也可使用任何合适类型的半导体开关部件。其中开关51被实现为nmos晶体管的配置可在本文中有时作为示例进行描述。

47.开关51可具有耦合到混频器输入端口rfin的输入端子(例如,晶体管源极端子)。开关51可具有耦合到混频器输出端口bbout的输出端子(例如,晶体管漏极端子)。基带信号可在混频器输出端口bbout处提供。开关51还可包括控制端子(例如,晶体管栅极端子),该控制端子被配置为接收由振荡器52生成的振荡器信号66。用于指晶体管中的电流传送端子的术语“源极”和“漏极”端子可互换使用,并且有时称为“源极-漏极”端子。因此,图5的布置也可被描述为晶体管51,该晶体管具有耦合到rfin端口的第一源极-漏极端子和耦合到bbout端口的第二源极-漏极端子。

48.如图5所示,在开关51的控制(g)端子和输入(s)端子之间可存在寄生部件,诸如寄生电容cpar。寄生电容cpar可将与lo信号66相关联的随机噪声源耦合到输入端口rfin,该输入端口rfin然后可与lo频率自混频并且可以直接劣化在输出端口bbout处生成的基带信号的噪声系数。

49.为了帮助补偿(减轻)这种不期望的寄生耦合效应,混频器电路50被设置有振荡器相位噪声消除电容器ccancel。相位噪声消除电容器ccancel具有耦合到混频器输入端口rfin的第一端子和被配置为接收反相振荡器信号68的第二端子。信号68可相对于信号66反相(例如,信号68可为信号66的反相版本)。以这种方式配置和操作,通过寄生电容cpar从开关51的控制(g)端子注入rfin节点中的任何相位噪声都可以由对应的补偿耦合信号抵消或消除,该对应的补偿耦合信号作为使用反相(相反)振荡器信号68控制电容器ccancel的结果而同时被注入rfin节点中。因此,通过与开关51相关联的cpar耦合的相位噪声将不会转移到基带输出端口bbout。因此,电容器ccancel有时被称为振荡器相位噪声消除部件、振荡器相位噪声消除器、振荡器相位噪声消除电路、振荡器相位噪声降低电路、振荡器相位噪声补偿电路或振荡器相位噪声减轻电路。

50.在一些实施方案中,振荡器相位噪声消除电容器ccancel具有固定的电容值。又如,电容器ccancel可表现出可变电容,该可变电容可被调整以调谐与电容器ccancel相关联的消除增益(例如,调整由ccancel提供的lo相位噪声消除的量)。电容器ccancel可以被实现为电容器组(例如,电容器阵列,其中至少一些可以根据期望的电容值而被切换成使用)。

51.图6是形成为无源差分混频器的第一混频器部分50-i的电路图。如图6所示,第一混频器部分50-i可具有差分输入端口,该差分输入端口具有正输入端口rfp和负输入端口

rfn。差分输入端口rfp和rfn可共同表示图3和图5所示的混频器输入端口rfin。混频器部分50-i可具有差分输出端口,该差分输出端口具有正输出端口iop和负输出端口ion。同相信号i(n)可跨差分输出端口iop和ion生成。

52.混频器部分50-i还可包括开关m1-m12和电容器c1-c8。在图6的示例中,开关m1-m12被实现为n沟道晶体管(例如,nmos晶体管)。这仅是例示性的。在其他实施方案中,混频器部分50-i中的至少一些或所有开关可被实现为p沟道晶体管(例如,pmos晶体管)。

53.晶体管m1、m2和m3可串联耦合在正输入端口rfp和正输出端口iop之间。晶体管m1具有被配置为接收振荡器信号in的栅极(控制)端子。晶体管m2具有被配置为接收振荡器信号ip的栅极(控制)端子。晶体管m3具有被配置为接收振荡器信号in的栅极(控制)端子。信号ip和in由本地振荡器52生成并且在下面结合图8和图9详细描述。电容器c1具有耦合到正输入端口rfp的第一端子以及耦合到插置在晶体管m4和m5的源极-漏极端子之间的节点的第二端子。电容器c3具有耦合到正输入端口rfp的第一端子以及耦合到插置在晶体管m2和m3的源极-漏极端子之间的节点a的第二端子。

54.晶体管m4、m5和m6可串联耦合在负输入端口rfn和正输出端口iop之间。晶体管m4具有被配置为接收振荡器信号ip的栅极(控制)端子。晶体管m5具有被配置为接收振荡器信号in的栅极(控制)端子。晶体管m6具有被配置为接收振荡器信号ip的栅极(控制)端子。电容器c2具有耦合到负输入端口rfn的第一端子以及耦合到插置在晶体管m1和m2的源极-漏极端子之间的节点的第二端子。电容器c4具有耦合到负输入端口rfn的第一端子以及耦合到插置在晶体管m5和m6的源极-漏极端子之间的节点b的第二端子。

55.与振荡器信号ip相关联的相位噪声可经由晶体管m2的寄生电容耦合到节点a。类似地,与振荡器信号in相关联的相位噪声也可经由晶体管m3的寄生电容耦合到节点a。耦合到节点a的相位噪声然后可通过晶体管m3与振荡器信号in混频,这导致基带输出信号中的噪声劣化。为了消除与信号ip和in相关联的lo相位噪声,混频器部分50-i设置有耦合到节点a的电容器n1和n2。在图6的示例中,电容器n1和n2被实现为金属-氧化物-半导体电容器(moscap)。这仅是例示性的。又如,电容器n1和n2可被实现为金属-绝缘体-金属(mim)电容器。又如,电容器n1和n2可被实现为金属-氧化物-金属(mom)电容器。一般来讲,电容器n1和n2可使用任何合适的半导体电容器结构来实现。

56.电容器n1具有耦合到节点a的第一(主体)端子和被配置为接收振荡器信号ipb(例如,相对于信号ip反相的信号)的第二(栅极)端子。电容器n2具有耦合到节点a的第一(主体)端子和被配置为接收振荡器信号inb(例如,相对于信号in反相的信号)的第二(栅极)端子。通过将电容器n1连接到晶体管m2的源极-漏极(输出)端子并且使用相反(反相)lo相位ipb来调制电容器n1,通过晶体管m2的寄生电容耦合到节点a的任何相位噪声可被来自电容器n1的相等且相反的耦合效应消除。晶体管m2的另一个源极-漏极(输入)端子直接连接到晶体管m1。类似地,通过将电容器n2连接到晶体管m3的源极-漏极(输入)端子并且使用相反(反相)lo相位inb来调制电容器n2,可通过与电容器n2相等且相反的耦合效应来消除通过晶体管m3的寄生电容耦合到节点a的任何相位噪声。晶体管m3的另一个源极-漏极(输出)端子连接到正输出端口iop。

57.混频器部分50-i还可设置有耦合到节点b的电容器n3和n4。在图6的示例中,电容器n3和n4被实现为金属-氧化物-半导体电容器(moscap),这仅仅是例示性的。如果需要,电

容器n3和n4可被实现为金属-绝缘体-金属(mim)电容器、金属-氧化物-金属(mom)电容器或任何合适的半导体电容器结构。

58.电容器n3具有耦合到节点b的第一(主体)端子和被配置为接收振荡器信号ipb(例如,相对于信号ip反相的信号)的第二(栅极)端子。电容器n4具有耦合到节点b的第一(主体)端子和被配置为接收振荡器信号inb(例如,相对于信号in反相的信号)的第二(栅极)端子。通过将电容器n4连接到晶体管m5的源极-漏极(输出)端子并且使用相反(反相)lo相位inb来调制电容器n4,通过晶体管m5的寄生电容耦合到节点b的任何相位噪声可被来自电容器n4的相等且相反的耦合效应消除。类似地,通过将电容器n3连接到晶体管m6的源极-漏极(输入)端子并且使用相反(反相)lo相位ipb来调制电容器n3,可通过与电容器n3相等且相反的耦合效应来消除通过晶体管m6的寄生电容耦合到节点b的任何相位噪声。

59.用于消除lo相位噪声的电容器n1、n2、n3和n4可统称为振荡器相位噪声消除电路70。电容器n1-n4中的每个电容器可被称为振荡器相位噪声消除电容器、振荡器相位噪声补偿电容器、振荡器相位噪声消除部件或振荡器相位噪声消除电路。

60.在单端方法中,无源同相混频器部分50-i可以仅包括以上述方式连接的部件m1-m6、c1-c4和n1-n4。在差分信号方案中,混频器部分50-i可包括用于在负输出端口ion处生成信号的另一个半电路(参见例如晶体管m7-m12、c5-c8和n5-n8)。

61.晶体管m7、m8和m9可串联耦合在正输入端口rfp和负输出端口ion之间。晶体管m7具有被配置为接收振荡器信号ip的栅极(控制)端子。晶体管m8具有被配置为接收振荡器信号in的栅极(控制)端子。晶体管m9具有被配置为接收振荡器信号ip的栅极(控制)端子。电容器c5具有耦合到正输入端口rfp的第一端子以及耦合到插置在晶体管m10和m11的源极-漏极端子之间的节点的第二端子。电容器c7具有耦合到正输入端口rfp的第一端子以及耦合到插置在晶体管m8和m9的源极-漏极端子之间的节点c的第二端子。

62.晶体管m10、m11和m12可串联耦合在负输入端口rfn和负输出端口ion之间。晶体管m10具有被配置为接收振荡器信号in的栅极(控制)端子。晶体管m11具有被配置为接收振荡器信号ip的栅极(控制)端子。晶体管m12具有被配置为接收振荡器信号in的栅极(控制)端子。电容器c6具有耦合到负输入端口rfn的第一端子以及耦合到插置在晶体管m7和m8的源极-漏极端子之间的节点的第二端子。电容器c8具有耦合到负输入端口rfn的第一端子以及耦合到插置在晶体管m11和m12的源极-漏极端子之间的节点d的第二端子。

63.与振荡器信号in相关联的相位噪声可经由与晶体管m8相关联的寄生电容耦合到节点c。类似地,与振荡器信号ip相关联的相位噪声也可经由与晶体管m9相关联的寄生电容耦合到节点c。耦合到节点c的相位噪声然后可通过晶体管m9与振荡器信号ip混频,这导致输出端口ion处的基带输出信号中的噪声劣化。

64.振荡器相位噪声消除电容器n5-n8可用于消除与信号ip和in相关联的lo相位噪声。在图6的示例中,电容器n5-n8被实现为金属氧化物半导体电容器(moscap),这仅仅是例示性的。作为其他示例,电容器n5-n8可被实现为mim电容器、mom电容器或其他合适的半导体电容器结构。

65.电容器n5具有耦合到节点c的第一(主体)端子和被配置为接收振荡器信号inb的第二(栅极)端子。电容器n6具有耦合到节点c的第一(主体)端子和被配置为接收振荡器信号ipb的第二(栅极)端子。通过将电容器n5连接到晶体管m8的源极-漏极(输出)端子并且使

用相反(反相)lo相位inb来调制电容器n5,通过晶体管m8的寄生电容耦合到节点c的任何相位噪声可被来自电容器n5的相等且相反的耦合效应消除。晶体管m8的另一个源极-漏极(输入)端子直接连接到晶体管m7。类似地,通过将电容器n6连接到晶体管m9的源极-漏极(输入)端子并且使用相反(反相)lo相位ipb来调制电容器n6,可通过与电容器n6相等且相反的耦合效应来消除通过晶体管m9的寄生电容耦合到节点c的任何相位噪声。晶体管m9的另一个源极-漏极(输出)端子连接到负输出端口ion。

66.电容器n7具有耦合到节点d的第一(主体)端子和被配置为接收振荡器信号inb的第二(栅极)端子。电容器n8具有耦合到节点d的第一(主体)端子和被配置为接收振荡器信号ipb的第二(栅极)端子。通过将电容器n8连接到晶体管m11的源极-漏极(输出)端子并且使用相反(反相)lo相位ipb来调制电容器n8,通过晶体管m11的寄生电容耦合到节点d的任何相位噪声可被来自电容器n8的相等且相反的耦合效应消除。类似地,通过将电容器n7连接到晶体管m12的源极-漏极(输入)端子并且使用相反(反相)lo相位inb来调制电容器n7,可通过与电容器n7相等且相反的耦合效应来消除通过晶体管m12的寄生电容耦合到节点d的任何相位噪声。

67.用于消除lo相位噪声的电容器n5、n6、n7和n8也可被视为振荡器相位噪声消除电路70的一部分。电容器n5-n8中的每个电容器可被称为振荡器相位噪声消除电容器、振荡器相位噪声补偿电容器、振荡器相位噪声消除部件或振荡器相位噪声消除电路。

68.可仔细选择每个振荡器相位噪声消除电容器n1-n8的尺寸。由于电容器n1被配置为抵消与晶体管m2的栅极-源极寄生电容cgs(其表示m2的栅极端子处的寄生电容的仅一半)相关联的耦合效应,因此mos电容器n1可为晶体管m2的尺寸的至少一半或以其他方式适当地设定尺寸以匹配晶体管m2的cgs。类似地,由于电容器n2被配置为抵消与晶体管m3的栅极-漏极寄生电容cgd(其表示m3的栅极端子处的寄生电容的仅一半)相关联的耦合效应,因此mos电容器n2可为晶体管m3的尺寸的至少一半或以其他方式适当地设定尺寸以匹配晶体管m3的cgd。同样,电容器n3、n4、n5、n6、n7和n8可分别为晶体管m5、m6、m8、m9、m11和m12的尺寸的一半。

69.控制其他开关中的一些开关的振荡器信号也可耦合到内部节点a、b、c和d。例如,控制晶体管m1的栅极的振荡器信号in也可经由电容器c3耦合到节点a。又如,控制晶体管m5的栅极的振荡器信号in可经由电容器c1和c3耦合到节点a。再如,控制晶体管m4的栅极的振荡器信号ip可经由电容器c1和c3耦合到节点a。又如,控制晶体管m7的栅极的振荡器信号ip可经由电容器c3耦合到节点a。又如,控制晶体管m10的栅极的振荡器信号in可经由电容器c5和c3耦合到节点a。又如,控制晶体管m11的栅极的振荡器信号ip还可经由电容器c5和c3耦合到节点a。lo相位噪声消除电容器n1和n2的尺寸可被优化以消除来自所有这些耦合路径的lo噪声。电容器n1的尺寸可大于m2的尺寸的一半,以帮助补偿附加寄生耦合路径。类似地,电容器n2的尺寸可大于m3的尺寸的一半,以帮助补偿附加寄生耦合路径。

70.图6的其中混频器部分50-i包括12个开关、8个电容器和8个lo相位噪声消除电容器的示例仅仅是例示性的。一般来讲,混频器部分50-i可以是被配置为提供电压增益并且包括任何合适数量的部件的任何无源混频器电路。例如,混频器部分50-i可包括少于12个开关、1个-11个开关、2个-10个开关、3个-9个开关、多于12个开关、12个-20个开关、13个-19个开关、14个-18个开关或多于20个开关。又如,混频器部分50-i可包括少于8个电容器、1

个-7个电容器、2个-6个电容器、多于8个电容器、8个-16个电容器、多于10个电容器、10个-20个电容器、多于20个电容器或没有电容器。又如,混频器部分50-i可包括少于8个相位噪声消除电容器、至少一个相位噪声消除电容器、至少两个相位噪声消除电容器、四个或更多个相位噪声消除电容器、1个-7个相位噪声消除电容器、2个-6个相位噪声消除电容器、多于8个相位噪声消除电容器、8个-16个相位噪声消除电容器或多于16个相位噪声消除电容器。

71.图6的第一混频器部分50-i用于生成同相信号i(n)。图7是用于生成正交相信号q(n)的第二混频器部分50-q的电路图。如图7所示,第二混频器部分50-q可具有差分输入端口,该差分输入端口具有正输入端口rfp和负输入端口rfn。差分输入端口rfp和rfn可共同表示图3和图5所示的混频器输入端口rfin。混频器部分50-q可具有差分输出端口,该差分输出端口具有正输出端口qop和负输出端口qon。可跨差分输出端口qop和qon生成正交相信号q(n)。

72.混频器部分50-q可包括开关、电容器和lo相位噪声消除电路70。混频器部分50-q中的开关、电容器和电路70的结构和连接可类似于混频器部分50-i,并且不需要详细重复以避免模糊本公开实施方案。混频器开关可由振荡器信号qn和qp控制。为了帮助减轻与耦合到混频器部分50-q内的内部节点e、f、g和h的信号qn和qp相关联的lo相位噪声,振荡器相位噪声消除电容器70直接连接到内部节点e、f、g和h并且由反相振荡器信号qpb和qnb调制以提供相等且相反的耦合效应。

73.图8是本地振荡器52的电路图,该本地振荡器被配置为生成用于控制同相混频器部分50-i的振荡器信号ip、ipb、in、inb,以及用于控制正相混频器部分50-q的信号qp、qpb、qn、qnb。如图8所示,振荡器52使用电压控制振荡器60来生成周期信号(例如,时钟信号、方波或正弦信号)。由电压控制振荡器60生成的周期信号被馈送到数字触发器62-i和62-q的时钟输入。触发器62-i具有第一输出端和第二输出端,在该第一输出端处生成第一振荡器信号,在该第二输出处生成第二振荡器信号。第二振荡器信号可相对于第一振荡器信号180

°

相移。第一振荡器信号可被馈送通过缓冲器64的第一链以生成对应的振荡器输出信号ip。第二振荡器信号可被馈送通过缓冲器64的第二链以生成对应的振荡器输出信号in。

74.振荡器52还可包括反相缓冲器,诸如耦合到第一缓冲器链中的最后缓冲级64’的输入端的反相器80-1。换句话讲,反相器80-1从第一缓冲器链中的倒数第二缓冲器接收信号。反相器80-1用于生成振荡器输出信号ipb,该振荡器输出信号相对于信号ip反相。通过将反相器80-1仅耦合到最终缓冲级64’,使由不共用反相器路径引起的任何潜在噪声贡献最小化。

75.振荡器52还可包括反相缓冲器,诸如耦合到第二缓冲器链中的最后缓冲级64’的输入端的反相器80-2。换句话讲,反相器80-2从第二缓冲器链中的倒数第二缓冲器(即,从紧接在最后缓冲级64’之前的缓冲器)接收信号。反相器80-2用于生成振荡器输出信号inb,该振荡器输出信号相对于信号in反相。通过将反相器80-2仅耦合到最终缓冲级64’,使由不共用反相器路径引起的任何潜在噪声贡献最小化。

76.触发器62-q具有第一输出端和第二输出但,在该第一输出端处生成第三振荡器信号,在该第二输出端处生成第四振荡器信号。第三振荡器信号可相对于第一振荡器信号90

°

相移。第三振荡器信号可被馈送通过缓冲器64的第三链以生成对应的振荡器输出信号qp。第四振荡器信号可被馈送通过缓冲器64的第四链以生成对应的振荡器输出信号qn。

77.振荡器52还可包括反相缓冲器,诸如耦合到第三缓冲器链中的最后缓冲级64’的输入端的反相器80-3。换句话讲,反相器80-3从第三缓冲器链中的倒数第二缓冲器接收信号。反相器80-3用于生成振荡器输出信号qpb,该振荡器输出信号相对于信号qp反相。通过将反相器80-3仅耦合到最终缓冲级64’,使由不共用反相器路径引起的任何潜在噪声贡献最小化。

78.振荡器52还可包括反相缓冲器,诸如耦合到第四缓冲器链中的最后缓冲级64’的输入端的反相器80-4。换句话讲,反相器80-4从第四缓冲器链中的倒数第二缓冲器接收信号。反相器80-4用于生成振荡器输出信号qnb,该振荡器输出信号相对于信号qn反相。通过将反相器80-4仅耦合到最终缓冲级64’,使由不共用反相器路径引起的任何潜在噪声贡献最小化。

79.在一些实施方案中,反相器80-1、80-2、80-3和80-4可以是具有可调整延迟的可编程反相器。这些反相器的延迟可在校准操作期间静态地调整或在正常无线操作期间动态地调整,以补偿潜在的过程、电压和温度(pvt)变化。

80.图9是示出涉及本地振荡器52的操作的示例性信号波形的图示。如图9所示,vco输出可用作基础时钟信号。虽然vco波形被示出为数字方波,但vco波形可以是模拟振荡信号、正弦信号或其他周期性波形。振荡器信号ip可与vco的上升沿对准(例如,具有0

°

相位偏移)。信号ip可(例如)被馈送到图6的混频器开关m2、m4、m6、m7、m9和m11的控制/栅极端子。振荡器信号ipb可相对于信号ip反相,并且因此有时可被称为反相振荡器信号ipb。反相信号ipb可(例如)被馈送到图6中的振荡器相位噪声消除电路n1、n3、n6和n8。

81.振荡器信号in可相对于信号ip偏移180

°

相移,如箭头104所指示。信号in可(例如)被馈送到图6的混频器开关m1、m3、m5、m8、m10和m12的控制/栅极端子。振荡器信号inb可相对于信号in反相,并且因此有时可被称为反相振荡器信号inb。反相信号inb可(例如)被馈送到图6中的振荡器相位噪声消除电路n2、n4、n5和n7。

82.振荡器信号qp可相对于信号ip偏移90

°

相移,如箭头100所指示。信号qp可(例如)被馈送到图7中的对应混频器开关的控制/栅极端子。振荡器信号qpb可相对于信号qp反相,并且因此有时可被称为反相振荡器信号qpb。反相信号qpb可(例如)被馈送到图7中的对应振荡器相位噪声消除moscap。振荡器信号qn可相对于信号in偏移180

°

相移,如箭头106所指示。信号qn可(例如)被馈送到图7中的对应混频器开关的控制/栅极端子。振荡器信号qnb可相对于信号qn反相,并且因此有时可被称为反相振荡器信号qnb。反相信号qnb可(例如)被馈送到图7中的对应振荡器相位噪声消除电容器。

83.图9的其中振荡器信号ip、ipb、qp、qpb、in、inb、qn和qnb具有25%占空比的示例仅仅是例示性的。又如,振荡器信号可具有50%占空比。又如,振荡器信号可具有10%占空比。又如,振荡器信号可具有20%占空比。又如,振荡器信号可具有30%占空比。又如,振荡器信号可具有40%占空比。又如,振荡器信号可具有10%-50%占空比。又如,振荡器信号可具有大于50%占空比。又如,振荡器信号可具有60%占空比。又如,振荡器信号可具有50%-90%占空比。如果需要,则振荡器信号的占空比可以是可调整的。

84.图10为示出执行振荡器相位噪声消除可如何减小基带信号的噪声系数的图示。曲线110绘出了在不使用振荡器相位噪声消除电路的情况下,作为频率(以对数标度计)的函数的,由无源混频器电路输出的信号的噪声系数。曲线112绘出了当振荡器相位噪声消除电

路被启用时,作为频率的函数的,从无源混频器电路输出的信号的噪声系数。如图10所示,使用振荡器相位噪声消除电路可帮助减小宽范围的工作频率上的噪声系数。

85.图11是操作至少图2至图8所示类型的混频器电路中涉及的例示性步骤的流程图。在步骤120处,本地振荡器(例如,振荡器52)生成振荡器信号和反相振荡器信号。振荡器信号可以包括信号ip、qp、in和qn,而反相振荡器信号可以包括信号ipb、qpb、inb和qnb。信号ip、qp、in、qn、ipb、qpb、inb和qnb可全部在不同的振荡器输出端子上生成。

86.在步骤122处,混频器电路可从前端模块内的天线或其他电路接收射频信号(参见图2)。

87.在步骤124处,混频器电路可通过用振荡器信号控制混频器开关同时用反相振荡器信号控制相位噪声消除电路(参见例如图5中的电容器ccancel和图6至图7中的电路70)来下变频射频信号。使用反相lo信号调制lo相位噪声消除电路可帮助抵消或补偿非反相lo信号到混频器电路中的内部节点中的寄生耦合。这可帮助改善混频器电路的噪声系数性能。

88.在步骤126处,混频器电路可随后将对应的基带信号输出到一个或多个基带处理器。

89.这些步骤仅为例示性的。可修改或省略所描述的步骤中的至少一些步骤;所描述的步骤中的一些步骤可被并行执行;可在所描述的步骤之间添加或插入附加步骤;某些步骤的顺序可颠倒或改变;可调整所描述的步骤的时序,使得它们在略微不同的时间发生,或者所描述的步骤可分布在系统中。

90.以上结合图1至图11描述的方法和操作可由设备10的部件使用软件、固件和/或硬件(例如,专用电路或硬件)来执行。用于执行这些操作的软件代码可存储在非暂态计算机可读存储介质(例如,有形计算机可读存储介质)上,该非暂态计算机可读存储介质存储在设备10的部件中的一个或多个部件上(例如,图1的存储电路16和/或无线通信电路24)。该软件代码有时可被称为软件、数据、指令、程序指令或代码。非暂态计算机可读存储介质可包括驱动器、非易失性存储器诸如非易失性随机存取存储器(nvram)、可移动闪存驱动器或其他可移动介质、其他类型的随机存取存储器等。存储在非暂态计算机可读存储介质上的软件可由设备10的部件中的一个或多个部件上的处理电路(例如,无线电路24中的处理电路、图1的处理电路18等)来执行。处理电路可包括微处理器、应用处理器、数字信号处理器、中央处理单元(cpu)、具有处理电路的专用集成电路或其他处理电路。

91.根据一个实施方案,提供了混频器电路,该混频器电路包括输入端口,该输入端口被配置为接收射频信号;输出端口,基于射频信号在该输出端口上生成基带信号;振荡器,该振荡器具有在其上生成第一振荡器信号的第一振荡器输出端子,在其上生成不同于第一振荡器信号的第二振荡器信号的第二振荡器输出端子,以及在其上生成相对于第二振荡器信号反相的第三振荡器信号的第三振荡器输出端子;第一开关,该第一开关具有耦合到输入端口的输入端子,耦合到输出端口的输出端子,以及耦合到第一振荡器输出端子的控制端子;第二开关,该第二开关具有耦合到第一开关的输出端子的输入端子,耦合到输出端口的输出端子,以及耦合到第二振荡器输出端子的控制端子;以及振荡器相位噪声消除电容器,该振荡器相位噪声消除电容器具有耦合到第二开关的输入端子的第一端子和耦合到第三振荡器输出端子的第二端子。

92.根据另一个实施方案,振荡器具有在其上生成相对于第一振荡器信号反相的第四振荡器信号的第四振荡器输出端子,混频器电路包括附加振荡器相位噪声消除电容器,该附加振荡器相位噪声消除电容器具有耦合到第二开关的输入端子的第一端子和耦合到第四振荡器输出端子的第二端子。

93.根据另一个实施方案,振荡器相位噪声消除电容器包括金属氧化物半导体电容器,该金属氧化物半导体电容器具有耦合到第二开关的输入端子的主体端子以及耦合到第三振荡器输出端子的栅极端子。

94.根据另一个实施方案,振荡器相位噪声消除电容器包括金属-绝缘体-金属电容器或金属-氧化物-金属电容器。

95.根据另一个实施方案,混频器电路包括第三开关,该第三开关具有耦合到输入端口的输入端子、耦合到第一开关的输入端子的输出端子、以及耦合到第二振荡器输出端子的控制端子。

96.根据另一个实施方案,振荡器包括触发器,该触发器具有第一输出端子和第二输出端子;第一缓冲器链,该第一缓冲器链具有耦合到第一输出端子的输入端子以及在其上生成第一振荡器信号的输出端子;以及第二缓冲器链,该第二缓冲器链具有耦合到第二输出端子的输入端子以及在其上生成第二振荡器信号的输出端子。

97.根据另一个实施方案,振荡器包括第一反相器和第二反相器,该第一反相器具有耦合到第一缓冲器链中的最后缓冲器的输入端子以及在其上生成第四振荡器信号的输出端子,该第二反相器具有耦合到第二缓冲器链中的最后缓冲器的输入端子以及在其上生成第三振荡器信号的输出端子。

98.根据另一个实施方案,第一反相器和第二反相器具有可调整的延迟以补偿过程、电压和温度变化。

99.根据另一个实施方案,金属-氧化物-半导体电容器为第二开关的尺寸的至少一半。

100.根据另一个实施方案,金属-氧化物-半导体电容器大于第二开关的尺寸的一半。

101.根据一个实施方案,提供了操作混频器的方法,方法包括利用输入端口来接收射频信号;利用振荡器来生成第一振荡器信号,不同于第一振荡器信号的第二振荡器信号,以及相对于第二振荡器信号反相的第三振荡器信号;利用第一开关从输入端口接收射频信号并且接收第一振荡器信号;利用第二开关从第一开关接收信号,接收第二振荡器信号,并且基于射频信号生成对应的基带信号;以及利用振荡器相位噪声消除器来接收第三振荡器信号并降低与第二振荡器信号相关联的相位噪声。

102.根据另一个实施方案,该方法包括利用振荡器来生成相对于第一振荡器信号反相的第四振荡器信号,以及利用附加相位噪声消除器来接收第四振荡器信号并降低与第一振荡器信号相关联的相位噪声。

103.根据另一个实施方案,生成第一振荡器信号、第二振荡器信号、第三振荡器信号和第四振荡器信号包括利用触发器来生成第一输出信号和第二输出信号,利用第一系列缓冲器来接收第一输出信号并且生成第一振荡器信号,以及利用第二系列缓冲器来接收第二输出信号并生成第二振荡器信号。

104.根据另一个实施方案,生成第一振荡器信号、第二振荡器信号、第三振荡器信号和

第四振荡器信号包括利用第一反相器从第一系列缓冲器中的倒数第二缓冲器接收信号并生成第四振荡器信号,以及利用第二反相器从第二系列缓冲器中的倒数第二缓冲器接收信号并生成第三振荡器信号。

105.根据另一个实施方案,该方法包括调谐振荡器相位噪声消除器以调整由振荡器相位噪声消除器提供的消除增益的量,以及调整第一反相器或第二反相器的延迟以补偿过程、电压和温度变化。

106.根据一个实施方案,提供了电子设备,该电子设备包括天线,该天线被配置为接收射频信号;基带处理器,该基带处理器被配置为接收基于射频信号生成的基带信号;振荡器,该振荡器具有在其上生成振荡器信号的第一振荡器输出端子,以及在其上生成相对于振荡器信号反相的反相振荡器信号的第二振荡器输出端子;以及混频器,该混频器被配置为从天线接收射频信号并且被配置为生成基带信号,混频器具有晶体管和电容器,该晶体管具有耦合到第一振荡器输出端子的栅极端子,该电容器具有耦合到晶体管的第一端子和耦合到第二振荡器输出端子的第二端子。

107.根据另一个实施方案,混频器具有输入端口和输出端口,晶体管包括第一晶体管和第二晶体管,该第一晶体管具有耦合到输入端口的第一源极-漏极端子、耦合到输出端口的第二源极-漏极端子、以及被配置为接收振荡器信号中的第一振荡器信号的栅极端子,该第二晶体管具有耦合到第一晶体管的第二源极-漏极端子的第一源极-漏极端子、耦合到输出端口的第二源极-漏极端子、以及被配置为接收振荡器信号中的第二振荡器信号的栅极端子。

108.根据另一个实施方案,电容器包括第一电容器和第二电容器,该第一电容器具有直接连接到第一晶体管的第一端子和被配置为接收反相振荡器信号中的第一反相振荡器信号的第二端子,该第二电容器具有直接连接到第二晶体管的第一端子和被配置为接收反相振荡器信号中的第二反相振荡器信号的第二端子。

109.根据另一个实施方案,振荡器包括触发器,该触发器具有第一输出端和第二输出端;第一多个缓冲器,该第一多个缓冲器耦合到第一输出端并且被配置为生成振荡器信号中的第一振荡器信号;以及第二多个缓冲器,该第二多个缓冲器耦合到第二输出端并且被配置为生成振荡器信号中的第二振荡器信号。

110.根据另一个实施方案,振荡器包括第一反相器和第二反相器,该第一反相器耦合到第一多个缓冲器中的最后缓冲器,第一反相器被配置为生成反相振荡器信号中的第一反相振荡器信号并且具有可调整延迟,该第二反相器耦合到第二多个缓冲器中的最后缓冲器,第二反相器被配置为生成反相振荡器信号中的第二反相振荡器信号并且具有可调整延迟。

111.前述内容仅为示例性的并且可对所述实施方案作出各种修改。前述实施方案可独立实施或可以任意组合实施。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。