1.本技术享有以日本专利申请2020-153000号(申请日:2020年9月11日)为基础申请的优先权。本技术通过参照该基础申请而包括基础申请的全部内容。

2.本发明的实施方式涉及半导体装置。

背景技术:

3.iii族氮化物作为下一代的功率半导体器件用的材料,例如,gan(氮化镓)系半导体备受期待。gan系半导体与si(硅)相比,具备较大的带隙。因此,gan系半导体器件与si(硅)半导体器件相比,能够实现小型且高耐压的功率半导体器件。此外,由此能够减小寄生电容,因此能够实现高速驱动的功率半导体器件。

4.在gan系的晶体管中,通常应用将二维电子气(2deg)作为载流子的hemt(high electron mobility transistor:高电子迁移率晶体管)结构。通常的hemt是即使不向栅极施加电压也会导通的常通晶体管。在gan系的晶体管中,存在难以实现只要不向栅极施加电压就不导通的常断晶体管这样的问题。

5.在处理数百v~一千v这样的高压电力的电源电路等中,重视安全方面而要求常断这一动作。因此,提出了通过进行将常通的gan系晶体管与常断的si晶体管连接的共源共栅连接来实现常断动作的电路结构。

6.此外,在流过漏极-源极间的主电路电流和流过栅极-源极间的驱动电流共用源极电感的电路结构的情况下,因随着主电路电流的时间变化在源极电感中产生的电动势的缘故,驱动电流也会被调制了。随之产生的功率半导体器件的上升速度、下降速度的降低等迟延以及漏极电流、源极电压随时间剧烈变化的减幅振荡就成为了问题。因此,提出了主电路电流与栅极驱动电流不共用源极电感而使用开尔文连接的电路结构。

技术实现要素:

7.本发明的实施方式提供一种能够应用于多种使用方案的半导体装置。

8.实施方式的半导体装置具备:半导体封装,具备具有第一电极、第二电极和第一控制电极的n型沟道常断晶体管(以下称为n型常断晶体管)、以及具有电连接于第二电极的第三电极、第四电极和第二控制电极的常通晶体管;第一端子,设于半导体封装,电连接于第一电极;多个第二端子,设于半导体封装,电连接于第二电极或第三电极,分别排列于第一方向上;第三端子,设于半导体封装,电连接于第四电极;第四端子,设于半导体封装,电连接于第一控制电极;以及多个第五端子,设于半导体封装,电连接于第二控制电极,分别排列于第一方向上。

附图说明

9.图1是第一实施方式的电力转换系统的示意图。

10.图2是第一实施方式的半导体装置的电路图。

11.图3(a)、(b)是第一实施方式的半导体装置的示意性俯视图。

12.图4是表示第一实施方式的半导体装置的第一使用方案的电路图。

13.图5是表示第一实施方式的半导体装置的第一使用方案的示意性俯视图。

14.图6是表示第一实施方式的半导体装置的第二使用方案的示意性俯视图。

15.图7是表示第一实施方式的半导体装置的第三使用方案的示意性俯视图。

16.图8是表示第一实施方式的半导体装置的第四使用方案的电路图。

17.图9是表示第一实施方式的半导体装置的第四使用方案的示意性俯视图。

18.图10是表示第一实施方式的半导体装置的第五使用方案的电路图。

19.图11是表示第一实施方式的半导体装置的第五使用方案的示意性俯视图。

20.图12是表示第一实施方式的半导体装置的第六使用方案的电路图。

21.图13是表示第一实施方式的半导体装置的第七使用方案的电路图。

22.图14(a)~(c)是表示v

g_on

的一例的示意图。

23.图15是成为第一实施方式的比较方式的半导体装置的电路图。

24.图16(a)~(c)是说明第一实施方式的作用效果的曲线图。

25.图17是第二实施方式的半导体装置的电路图。

26.图18是第三实施方式的半导体装置的电路图。

27.图19是第三实施方式的半导体装置的示意性俯视图。

28.图20是第四实施方式的半导体装置的示意性俯视图。

29.图21是第五实施方式的半导体装置的示意性俯视图。

30.图22是第六实施方式的半导体装置的电路图。

31.图23是第六实施方式的半导体装置的示意性俯视图。

具体实施方式

32.以下,参照附图对本发明的实施方式进行说明。另外,在以下的说明中,有时对相同或类似的构件标注相同的附图标记。此外,对于说明过一次的构件等,有时适当省略其说明。

33.此外,本说明书中,半导体装置是包含由分立半导体等多个元件组合而成的功率模块、或者对分立半导体等多个元件编入了驱动这些元件的驱动电路或自我保护功能的智能功率模块、或者是具备功率模块、智能功率模块的系统整体的概念。

34.此外,本说明书中,“gan系半导体”是gan(氮化镓)、aln(氮化铝)、inn(氮化铟)以及具备它们的中间组分的半导体的总称。

35.(第一实施方式)

36.实施方式的半导体装置具备:半导体封装,具备具有第一电极、第二电极和第一控制电极的n型沟道常断晶体管、具有电连接于第二电极的第三电极、第四电极和第二控制电极的常通晶体管、具有电连接于第二控制电极的第一阳极和电连接于第三电极的第一阴极的第一二极管、以及具有电连接于第一电极的第二阳极和电连接于第二电极的第二阴极的齐纳二极管;第一端子,设于半导体封装,电连接于第一电极;多个第二端子,设于半导体封装,电连接于第一电极,分别排列于第一方向上;第三端子,设于半导体封装,电连接于第四电极;多个第四端子,设于半导体封装,电连接于第一控制电极,分别排列于第一方向上;以

及多个第五端子,设于半导体封装,电连接于第二控制电极,分别排列于第一方向上。

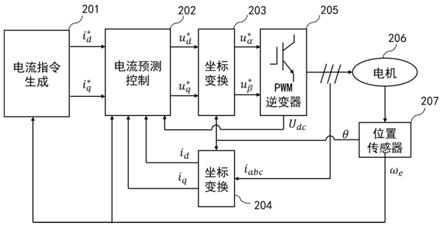

37.图1是本实施方式的电力转换系统900的示意图。

38.电力转换系统900具备电力转换装置800和电机810。

39.电力转换装置800具备:晶体管600a、600b、600c、600d、600e和600f、直流电源300、转换器400、平滑电容500。另外,如后所述,晶体管600a、600b、600c、600d、600e和600f可以包括多个晶体管以及其他元件等。

40.直流电源300输出直流电压。转换器400为dc-dc转换器,直流电源300将输出的直流电压转换为其他的直流电压。平滑电容500将由转换器400输出的电压平滑化。

41.晶体管600a、600b、600c、600d、600e和600f分别具有后述的半导体装置100。通过晶体管600a、600b、600c、600d、600e和600f,由平滑电容500平滑化的直流电压被转换为交流电压。

42.例如,晶体管600a具有第一晶体管电极602和第二晶体管电极604。此外,晶体管600b具有第三晶体管电极606和第四晶体管电极608。晶体管600a和晶体管600b通过第一晶体管电极602和第四晶体管电极608电连接而相互电连接。

43.同样地,晶体管600c和晶体管600d以及晶体管600e和晶体管600f分别相互电连接。

44.电机810具有线圈810u、810v和810w。线圈810u、810w和810v的一端在中性点820处相互电连接。线圈810u的另一端电连接于晶体管600a与晶体管600b之间。线圈810v的另一端电连接于晶体管600c与晶体管600d之间。此外,线圈810w的另一端电连接于晶体管600e与晶体管600f之间。

45.另外,本实施方式的电力转换装置800中的接地例如可以电连接于设有多个的平滑电容500之间。此外,例如,电力转换装置800中的接地也可以电连接于晶体管600b、晶体管600d和晶体管600f相互电连接的电路线。

46.图2是本实施方式的半导体装置100的电路图。本实施方式的半导体装置100例如是额定电压为600v、1200v的功率模块。

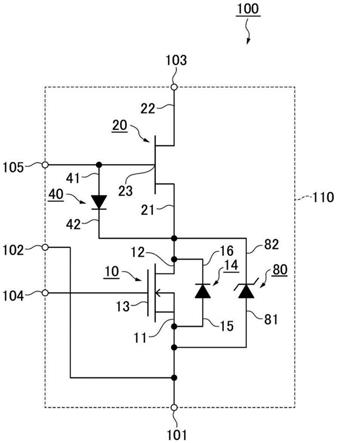

47.半导体装置100具备:n型常断晶体管10、常通晶体管20、第一二极管40、齐纳二极管80、第一端子101、第二端子102、第三端子103、第四端子104、第五端子105和半导体封装110。

48.n型常断晶体管10具有第一电极11、第二电极12和第一控制电极13。

49.n型常断晶体管10是在不向栅极输入电压的情况下不会流过漏极电流的晶体管。n型常断晶体管10例如是使用si(硅)半导体的n型mosfet(metal oxide semiconductor field effect transistor:金属氧化物半导体场效应管)。例如,第一电极11是源电极,第二电极12是漏电极,第一控制电极13是栅电极。此外,n型常断晶体管10是具有阳极15和阴极16的体二极管(寄生二极管)14。此外,n型常断晶体管10的耐压为例如10v以上且50v以下。

50.常通晶体管20具有第三电极21、第四电极22和第二控制电极23。第三电极21电连接于第二电极12。

51.常通晶体管20是即使在不向栅极输入电压的情况下也会流过漏极电流的晶体管。常通晶体管20是例如使用gan系半导体的hemt(high electron mobility transistor:高

电子迁移率晶体管)。例如,第三电极21是源电极,第四电极22是漏电极,第二控制电极23是栅电极。

52.常通晶体管20的耐压高于n型常断晶体管10的耐压。常通晶体管20的耐压例如为40v以上且3500v以下。

53.本实施方式的半导体装置100通过将n型常断晶体管10与常通晶体管20串联电连接,来实现常断动作。例如,当半导体装置100用于晶体管600b(图1)的情况下,第三晶体管电极606电连接于第一电极11,第四晶体管电极608电连接于第四电极22。

54.第一二极管40具有第一阳极41和第一阴极42。第一阳极41电连接于第二控制电极23。第一阴极42电连接于第三电极21。第一二极管40优选为响应速度快的肖特基势垒二极管。另外,即使第一二极管40是pn结型二极管,也可以优选地使用。第一二极管40的用途记载在后述的实施方式的半导体装置100的第七使用方案中。

55.齐纳二极管80具有第二阳极81和第二阴极82。第二阳极81电连接于第一电极11。此外,第二阴极82电连接于第二电极12。换言之,齐纳二极管80与n型常断晶体管10并联连接。当在n型常断晶体管10与常通晶体管20的连接部产生因浪涌等引起的过电压的情况下,在过电压到达齐纳电压的时间点,电荷被释放到齐纳二极管80。因此,会抑制连接部的电压上升,抑制常通晶体管20的栅极绝缘膜的漏电流的增大、栅极绝缘膜的破坏。

56.n型常断晶体管10、常通晶体管20、第一二极管40和齐纳二极管80设于半导体封装110内。换言之,半导体封装110具有n型常断晶体管10、常通晶体管20、第一二极管40和齐纳二极管80。

57.第一端子101设于半导体封装110,电连接于第一电极11。第一端子101例如被用作半导体装置100的源极端子。

58.第二端子102设于半导体封装110,电连接于第一电极11。第二端子102例如被用作用于对半导体装置100进行开尔文连接的端子。

59.第三端子103设于半导体封装110,电连接于第四电极22。第三端子103例如被用作半导体装置100的漏极端子。

60.第四端子104设于半导体封装110,电连接于第一控制电极13。第四端子104例如被用于将栅极信号输入至n型常断晶体管10。

61.第五端子105设于半导体封装110,电连接于第二控制电极23。第五端子105例如用于将栅极信号输入至常通晶体管20。

62.图3是本实施方式的半导体装置100的示意性俯视图。

63.图3(a)是本实施方式的半导体装置100的示意性俯视图。图3(b)是本实施方式的半导体装置100的示意俯视图的一部分的一例。

64.n型常断晶体管10例如是纵型si-mosfet,在上表面设有第一电极11和第一控制电极13。第一电极11例如经由键合线(bonding wire)116电连接于第一端子101。此外,第一电极11例如经由键合线122电连接于第二端子102。在未图示的n型常断晶体管10的下表面设有第二电极12。第二电极12电连接于例如在cu(铜)上进行了镍、钯、金等的镀敷处理的金属制的板112。第一控制电极13经由键合线124电连接于第四端子104。

65.齐纳二极管80的第二阳极81设于齐纳二极管80的上表面。第二阳极81例如经由键合线114电连接于第一端子101。即,第二阳极81例如经由键合线114、第一端子101和键合线

116电连接于第一电极11。此外,在未图示的齐纳二极管80的下表面设有第二阴极82。第二阴极82例如电连接于板112。而且,第二阴极82例如经由板112电连接于第二电极12。

66.常通晶体管20的第三电极21、第四电极22和第二控制电极23设于常通晶体管20的上表面。第三电极21例如经由键合线126连接于板112。即,第三电极21例如经由键合线126和板112电连接于第二电极12。第四电极22例如经由键合线128电连接于第三端子103。第二控制电极23例如经由键合线118电连接于第五端子105。

67.第一二极管40的第一阳极41设于第一二极管40的上表面。第一阳极41例如经由键合线120电连接于第五端子105。即,第一阳极41经由键合线120、第五端子105和键合线118电连接于第二控制电极23。此外,在未图示的第一二极管40的下表面设有第一阴极42。第一阴极42经由板112和键合线126电连接于第三端子21。

68.另外,本实施方式的半导体装置100中使用的键合线的材质、根数没有特别限定。此外,不限于键合线,如图21所示,也可以通过金属盘(metal plate)进行连接。

69.半导体装置100具有作为第二端子102的多个第二端子102a、102b和102c。多个第二端子102a、102b和102c通过端子102d相互电连接。

70.此外,半导体装置100具有作为第五端子的多个第五端子105a、105b和105c。第五端子105a、105b和105c通过端子105d相互电连接。

71.同样地,半导体装置100具有作为第一端子101的相互电连接的多个第一端子101a、101b、101c、

……

、101q。另外,第一端子101a、101b、101c、

……

、101q也可以不分离。此外,半导体装置100具有作为第三端子103相互电连接的多个第三端子103a、103b、103c、

……

、103q。另外,半导体装置100还可以进一步具有其他端子即作为端子106的端子106a、106b、106c、

……

、106k和作为端子107的端子107a、107b、107c和107d。

72.另外,第三端子103a、103b、103c、

……

、103q如图20所示,也可以不分离。第二端子102、第五端子105、第一端子101、端子106和端子107也是同样的。

73.例如,如图3(b)所示,多个第二端子102a、102b和102c分别被虚拟直线l1穿过。此外,多个第五端子105a、105b和105c分别被虚拟直线l1穿过。换言之,多个第二端子102a、102b和102c排列于第一方向上。此外,多个第五端子105a、105b和105c排列于第一方向上。在此,第一方向是例如第一端子101和第三端子103对置的方向。

74.另外,虚拟直线l1实际上并没有在半导体装置100中记载或者设置。

75.此外,优选多个第二端子102a、102b和102c以及多个第五端子105a、105b和105c设于半导体封装110的端部。

76.此外,优选在多个第二端子102a、102b和102c与多个第五端子105a、105b和105c之间未设置第一端子101、第三端子103和第四端子104中的任一个。换言之,优选多个第二端子102a、102b和102c与多个第五端子105a、105b和105c相互邻接设置而不是隔着第一端子101、第三端子103和第四端子104中的任一个。

77.此外,优选第四端子104设置在半导体封装110的端部。

78.此外,优选在多个第二端子102a、102b和102c与第四端子104之间不设置第一端子101、第三端子103和第五端子105中的任一个。换言之,优选多个第二端子102a、102b和102c与第四端子104相互邻接设置而不是隔着第一端子101、第三端子103和第五端子105中的任一个。

79.另外,虽然多个第二端子102a、102b和102c的个数在本实施方式的半导体装置100中为三个,但不限于三个。此外,虽然多个第五端子105a、105b和105c的个数在本实施方式的半导体装置100中为三个,但不限于三个。

80.图4是表示本实施方式的半导体装置100的第一使用方案的电路图。作为贴片电阻(chip resistor)150的贴片电阻150a具有作为第六端子152的第六端子152a和作为第七端子154的第七端子154a。而且,第六端子152a电连接于第二端子102,第七端子154a电连接于第五端子105。贴片电阻150a例如为长边0.6mm、短边0.3mm的0603型贴片电阻。

81.图5是表示本实施方式的半导体装置100的第一使用方案的示意性俯视图。第六端子152a经由金属板142电连接于作为第二端子102的第二端子102a。此外,第七端子154a经由金属板140电连接于第五端子105c。

82.图6是表示本实施方式的半导体装置100的第二使用方案的示意性俯视图。作为贴片电阻150的贴片电阻150b具有作为第六端子152的第六端子152b和作为第七端子154的第七端子154b。而且,第六端子152b电连接于作为第二端子102的第二端子102a,第七端子154b电连接于第五端子105。贴片电阻150b例如为长边1.0mm、短边0.5mm的1005型贴片电阻。

83.图7是表示本实施方式的半导体装置100的第三使用方案的示意性俯视图。作为贴片电阻150的贴片电阻150c具有作为第六端子152的第六端子152c和作为第七端子154的第七端子154c。而且,第六端子152c电连接于作为第二端子102的第二端子102b,第七端子154c电连接于作为第五端子105的第五端子105b。贴片电阻150c例如为长边1.6mm、短边0.8mm的1608型贴片电阻。

84.图8是表示本实施方式的半导体装置100的第四使用方案的电路图。贴片铁氧体磁珠(chip ferrite beads)156具有第六端子152和第七端子154。而且,第六端子152电连接于第二端子102,第七端子154电连接于第五端子105。

85.图9是表示本实施方式的半导体装置100的第四使用方案的示意性俯视图。第六端子152经由金属板142电连接于作为第二端子102的第二端子102b。此外,第七端子154经由金属板140电连接于作为第五端子105的第五端子105b。

86.图10是表示本实施方式的半导体装置100的第五使用方案的电路图。第一贴片二极管160的第三阴极164电连接于第二端子102。第一贴片二极管160的第三阳极162电连接于第五端子105。

87.此外,贴片电阻150a的第六端子152电连接于第二端子102。在第五端子105处,第二贴片二极管170的第四阴极174电连接于第五端子105。第二贴片二极管170的第四阳极172与第七端子154电连接。由此,第二贴片二极管170与贴片电阻150a电连接的电路与第一贴片二极管160并联电连接。

88.在从第五端子105侧向第二端子102侧急剧地流过大电流的情况下,通过第一贴片二极管160流过该大电流。另一方面,在从第二端子102侧向第五端子105侧急剧地流过大电流的情况下,虽然通过第二贴片二极管170流过该大电流,但该电流受到贴片电阻150a的限制。由此,会抑制在设于半导体封装110内的n型常断晶体管10和常通晶体管20从关断变为导通时急剧地流过大电流,会抑制噪声增大。

89.另外,虽然在图10中对使用贴片电阻150a的实施方式进行了描述,但是也可以使

用贴片铁氧体磁珠156来代替贴片电阻150a。

90.图11是表示本实施方式的半导体装置100的第五使用方案的示意性俯视图。金属板146电连接于第二端子102c。第六端子152和第三阴极164电连接于金属板146。此外,金属板144电连接于第五端子105a。第三阳极162和第四阴极174电连接于金属板144。第七端子154和第四阳极172由金属板148连接。

91.图12是表示本实施方式的半导体装置100的第六使用方案的示意性俯视图。第二端子102和第五端子105通过布线180电连接。也可以是如本使用方案那样使用布线180来连接的方案。另外,作为第二端子102,可以是第二端子102a、102b和102c中的任一个。此外,作为第五端子105,可以是第五端子105a、105b和105c中的任一个。

92.图13是表示本实施方式的半导体装置100的第七使用方案的电路图。

93.电容85具有第八端子86和第九端子87。第八端子86电连接于第五端子。

94.电阻75具有第十端子76和第十一端子77。第十端子76电连接于第四端子104。

95.第二二极管70具有第五阳极71和第五阴极72。第五阳极71电连接于第十一端子77。第五阴极72电连接于第四端子104和第十端子76。第二二极管70与电阻75电并联地设置。

96.第三二极管90具有第三阳极91和第三阴极92。第三阳极91电连接于第五端子105和第八端子86。第三阴极92电连接于第九端子87、第五阳极71和第十一端子77。第三二极管90与电容85电并联地设置。

97.第二二极管70和第三二极管90优选为响应速度快的肖特基势垒二极管。另外,即使第二二极管70和第三二极管90是pn结型二极管,也可以优选地使用。

98.电容85优选为陶瓷电容。原因是频率特性优越。但是,作为电容85,也可以优选使用其他的薄膜电容、铝电解电容或者钽电解电容等。

99.栅极电阻94具有端子93和端子95。端子93连接于第三阴极92、第九端子87、第五阳极71和第十一端子77。

100.信号源98输出例如矩形波等信号。

101.栅极驱动电路96连接于端子95。而且,栅极驱动电路96基于从信号源98输出的信号,输出驱动n型常断晶体管10和常通晶体管20的信号。另外,栅极驱动电路96的接地与第二端子102连接。

102.栅极驱动电路96是多个元件被单片化后的ic或配置有多个电子零件的电子电路基板。

103.接着,说明本实施方式的半导体装置100的第七使用方案的动作的一例。

104.考虑例如使用信号源98和栅极驱动电路96来输出往返于0v与v

g_on

的矩形波的情况。

105.图14是表示v

g_on

的一例的示意图。图14(a)示出了栅极驱动电路96的输出电压是在时间t1期间输出的0v与时间t2期间输出的v

g_on

之间反复的矩形波的情况。图14(b)示出了第一栅极驱动电路96a的输出电压是在时间t1期间输出的v1与时间t2期间输出的v1跟v2的和之间反复的矩形波的情况。在图14(b)的情况下,v

g_on

=v1 v2(v

g_on

=|v1| |v2|)。

106.图14(c)示出了在时间t1期间输出负电压的情况。在图14(c)的情况下,v

g_on

=|v2|-|v1|。这样,栅极驱动电路96的输出电压是随时间变化的电压。而且,例如栅极驱动电路

96的输出电压中的最大电压是v

g_on

。另外,虽然在图14中作为t1=t2进行了图示,但是t1和t2也可以不同。此外,栅极驱动电路96的输出电压的随时间变化的方法不限于图14所示的方法。此外,v

g_on

可以使用市售的示波器等容易地来测定。此外,v

g_on

是以第一端子101或第一电极11的电压为基准进行测定的电压。在此,“以电压为基准”是指例如“将电压设为0v”。

107.当从栅极驱动电路96输出v

g_on

时,电流从电容85经由第一二极管40流过。在第二控制电极23与第三电极21之间输入与第一二极管40的正向电压vf相当的电压。由此,常通晶体管20变为导通。另一方面,在从栅极驱动电路96输出0v时,电流经由常通晶体管20的未图示的寄生电容c

gs

流向电容85的反向。在第二控制电极23与第三电极21之间输入与vf和v

g_on

的差分相当的负的电压(vf-v

g_on

)。如果负的电压(vf-v

g_on

)低于常通晶体管20的阈值电压,则可以使常通晶体管20关断。

108.此外,如果v

g_on

高于n型常断晶体管10的阈值电压,则在从栅极驱动电路96输出v

g_on

时,能使n型常断晶体管10导通。

109.在此,在半导体装置100从关断过渡到导通时,优选n型常断晶体管10比常通晶体管20先导通。如果使常通晶体管20先导通,则由于会在第二电极12与第三电极21的连接部施加高电压,所以恐怕会使耐压低的n型常断晶体管10的特性劣化。

110.在本实施方式的半导体装置100中,在半导体装置100从关断状态过渡到导通状态时,从栅极驱动电路96输出的电流流过第二二极管70。因此,第一控制电极13的充电不会受电阻75的影响。因此,能对第一控制电极13快速充电。由此,在半导体装置100从关断状态过渡到导通状态时,能使n型常断晶体管10比常通晶体管20可靠地先导通。由此,半导体装置的可靠性提高。

111.此外,通过设置电阻75,能够使n型常断晶体管10的关断定时从常通晶体管20的关断定时延迟期望的时间。进而,根据第二二极管70的特性、电阻75的电阻值、矩形波的形状的设计,能够在n型常断晶体管10的状态保持为导通的状态下进行动作。

112.另外,要考虑到由信号源98和栅极驱动电路96输出0v,n型常断晶体管10、常通晶体管20为关断的情况。当对第四电极22施加高电压时,第三电极21的电压会变高。此时,常通晶体管20的关断状态恐怕会无法保持。因此,设置第三二极管90,使栅极驱动电路96与第二控制电极23短路,以保持常通晶体管20的关断状态。

113.另外,在上述内容中,记载了经由金属板140、金属板142、金属板144和金属板146的电连接。但是,实施方式的半导体装置100中的第二端子102和第五端子105的电连接也可以是不经由金属板140、金属板142、金属板144和金属板146的电连接。

114.接着,对实施方式的半导体装置100的作用效果进行记载。

115.图15是实施方式的比较方式的半导体装置1000的电路图。在半导体装置1000中,不设置第二端子102、第五端子105、第一二极管40和齐纳二极管80。此外,经由布线1002,第二控制电极23与第一电极11电连接。例如,将信号源和栅极驱动电路经由第四端子104与第一控制电极13连接,输入控制n型常断晶体管10的信号。输入到第二控制电极23的电压由第二电极12的电压与第一电极11的电压的差,即n型常断晶体管10的漏极-源极间电压v

ds

决定。由此,可以控制n型常断晶体管10与常通晶体管20两者。

116.在此,在随开关的电压的时间变化即dv/dt以意外的形式发生的情况下,有时谋求加以抑制。作为控制dv/dt的方法,例如可以考虑选择具有适当的电阻值的电阻,利用该电

阻连接第一电极11和第二控制电极23的方法。但是,连接第一电极11和第二控制电极23的电阻的电阻值根据使用半导体装置1000的电力转换系统900的规格而不同。因此,如果未将半导体装置1000实际用于电力转换系统900来反复试验的话,就难以适当地选定连接第一电极11和第二控制电极23的电阻的电阻值。但是,由于第一电极11和第二控制电极23的连接在半导体封装110内进行,因此存在无法容易地进行电阻的选定、电阻的连接这样的问题。

117.此外,由于在电力进行开关时会产生具有高频的信号,因此优选以较短布线长度连接第一电极11和第二控制电极23。但是,作为电阻优选使用的贴片电阻、贴片铁氧体磁珠的大小有时根据电阻的电阻值会具有不同的大小。因此,存在会成为布线长度因电阻值而大不相同的连接,不能顺利地控制dv/dt而发生寄生振荡的情况。

118.此外,例如在第七使用方案中使用半导体装置100的情况下,如上所述,半导体装置100的可靠性提高。然而,根据电力转换系统900的规格,也可考虑其他的使用方案为适当的情况。因此,得到了能容易地在各种使用方案中使用的半导体装置。

119.因此,由于在实施方式的半导体装置100中,设有由虚拟直线l1穿过的多个第二端子102和多个第五端子105,换言之,设有排列于第一方向上的多个第二端子102和多个第五端子105,所以在图4和图5所示的第一使用方案、图6所示的第二使用方案、图7所示的第三使用方案、图8和图9所示的第四使用方案以及图10和图11所示的第五使用方案中的任一个中,都能结合电力转换系统900的规格和所使用的贴片电阻、贴片铁氧体磁珠等的大小,来适当选择多个第二端子102和多个第五端子105,以短布线长度进行电阻等的连接。因此,可以容易地进行dv/dt的控制。

120.此外,根据电力转换系统900的规格,能够在图12所示的第六使用方案中使用半导体装置100。在第六使用方案中可以看出,成为比较方式的半导体装置1000的由布线1002实现的第二控制电极23和由第一电极11实现的连接,是在半导体封装110的外面使用布线180来进行的。

121.进而,根据电力转换系统900的规格,能够在图13所示的第七使用方案中使用半导体装置100。

122.这样,半导体装置100根据电力转换系统900的规格,可以适当地被使用。因此,能够提供一种能够应用于多种使用方案的半导体装置。

123.图16是说明实施方式的半导体装置100的作用效果的曲线图。图16(a)是表示在第一使用方案中使用实施方式的半导体装置100的情况下,流过n型常断晶体管10和常通晶体管20的电流在使贴片电阻150的电阻变化的情况下的随时间变化的曲线图。图16(b)是表示在第一使用方案中使用实施方式的半导体装置100的情况下,使贴片电阻150的电阻变化的情况下的第一电极11与第四电极22之间的电压的随时间变化的曲线图。图16(c)是表示在第一使用方案中使用实施方式的半导体装置100的情况下,流过n型常断晶体管10和常通晶体管20的电流和第一电极11与第四电极22之间的电压的乘积在使贴片电阻150的电阻变化的情况下的随时间变化的曲线图。如图16(a)所示,在贴片电阻150的电阻值小的情况下,电流的振动即使经过长时间也不太会衰减,而且振动的振幅也很大。在贴片电阻150的电阻值大的情况下,电流的振动经过短时间就会衰减,振动的振幅也很小。如图16(b)所示,在贴片电阻150的电阻大的情况下,在电压从400v降低至0v之前,有需要更长时间的倾向。在贴片

电阻150的电阻小的情况下,在电压从400v降低至0v之前,有需要更短时间的倾向,能够容易地控制dv/dt。如图16(c)所示,贴片电阻150的电阻值越大,上述的电流与电压的乘积有越小的倾向。在实施方式的半导体装置100中,根据电力转换系统900的规格,能够适当地选择贴片电阻150的电阻值,可以在各个优选方案中进行动作。

124.另外,优选多个第二端子102和多个第五端子105设于半导体封装110的端部。此外,优选在多个第二端子102与第五端子105之间不设置第一端子101、第三端子103和第四端子104中的任一个。原因是要使贴片电阻150等的连接最短。

125.此外,优选第四端子104设于半导体封装110的端部。此外,优选在多个第二端子102a、102b和102c和第四端子104之间不设置第一端子101、第三端子103和第五端子105中的任一个。原因是要减小在布线上产生的寄生电感。

126.此外,优选第五端子105设于半导体封装110的端部。此外,优选在多个第二端子102a、102b和102c和第五端子105之间不设置第一端子101、第三端子103和第四端子104中的任一个。原因是要减小在布线上产生的寄生电感。

127.根据本实施方式的半导体装置100,能提供一种能够应用于多种使用方案的半导体装置。

128.(第二实施方式)

129.本实施方式的半导体装置具备:半导体封装,具备具有第一电极、第二电极和第一控制电极的n型常断晶体管、具有电连接于第二电极的第三电极、第四电极和第二控制电极的常通晶体管、具有电连接于第二控制电极的第一阳极和电连接于第一电极的第一阴极的第一二极管、以及具有电连接于第一电极的第二阳极和电连接于第二电极的第二阴极的齐纳二极管;第一端子,设于半导体封装,电连接于第一电极;多个第二端子,设于半导体封装,电连接于第一电极,分别排列于第一方向上;第三端子,设于半导体封装,电连接于第四电极;第四端子,设于半导体封装,电连接于第一控制电极;多个第五端子,设于半导体封装,电连接于第二控制电极,分别排列于第一方向上。在此,省略与第一实施方式重复内容的记载。

130.图17是本实施方式的半导体装置200的电路图。在半导体装置200中,在第一二极管40的第一阴极42电连接于第一电极11这一点上与第一实施方式的半导体装置100不同。另外,由于多个第二端子102电连接于第一电极11,因此第一阴极42电连接于多个第二端子102。

131.在本实施方式的半导体装置200中,也能提供一种能够应用于多种使用方案的半导体装置。

132.(第三实施方式)

133.本实施方式的半导体装置具备:半导体封装,具备具有第一电极、第二电极和第一控制电极的p型沟道常断晶体管(以下称为p型常断晶体管)、以及具有电连接于第二电极的第三电极、第四电极和第二控制电极的常通晶体管;第一端子,设于半导体封装,电连接于第一电极;第二端子,设于半导体封装,电连接于第二电极或第三电极,排列于第一方向上;第三端子,设于半导体封装,电连接于第四电极;第四端子,设于半导体封装,电连接于第一控制电极,排列于第一方向上;第五端子,设于半导体封装,电连接于第二控制电极,分别排列于第一方向上。在此,省略与第一和第二实施方式重复内容的记载。

134.图18是本实施方式的半导体装置210的电路图。在半导体装置210中,使用p型常断晶体管30来代替n型常断晶体管10。p型常断晶体管30具有第一电极31、第二电极32和第一控制电极33。p型常断晶体管30是在不向栅极输入电压的情况下不会流过漏极电流的晶体管。p型常断晶体管30是例如使用si(硅)半导体的p型沟道mosfet(metal oxide semiconductor field effect transistor:金属氧化物半导体场效应管)。例如,第一电极31是漏极,第二电极32是源极,第一控制电极33是栅极。此外,p型常断晶体管30具备具有阳极35和阴极36的体二极管(寄生二极管)34。此外,p型常断晶体管30的耐压为例如10v以上且50v以下。

135.此外,在第二端子102电连接于第二电极32(或第三电极21)这一点上与第一实施方式的半导体装置100不同。这是因为在n型常断晶体管的情况下是以源极电压即第一电极11与第一控制电极13之间的电压进行控制,而在p型常断晶体管的情况下是以源极电压即第二电极32与第一控制电极33之间的电压进行控制,所以将第二端子102电连接于第二电极32。

136.图19是本实施方式的半导体装置210的示意性俯视图。

137.例如在cu(铜)上进行了镍、钯、金等的镀敷处理的金属制的板112与第一端子101电连接。在板112上设有常通晶体管20、p型常断晶体管30、第一二极管40。

138.常通晶体管20具有作为第二控制电极23的第二控制电极23a和第二控制电极23b。第二控制电极23a例如通过键合线118与第五端子105电连接。第三控制电极21例如通过键合线120与第二端子102电连接。

139.p型常断晶体管30在上表面具有第二电极32和第二控制电极33,在下表面具有未图示的第一电极31。第二控制电极32例如通过键合线126与第三电极21电连接。第二控制电极33例如通过键合线124与第四端子104电连接。第一电极31与板112和第一端子101电连接。

140.在第二端子102上设有齐纳二极管80。齐纳二极管80的第二阳极81设于齐纳二极管80的上表面,例如通过键合线130与板112和第一端子101电连接。齐纳二极管80的第二阴极82设于齐纳二极管80的下表面,与第二端子102和第二电极32电连接。

141.第一二极管40的第一阳极41设于第一二极管40的上表面。第二控制电极23b例如通过键合线132与第一阳极41电连接。未在图19中图示的第一二极管40的第一阴极42设于第一二极管40的下表面,与板112和第一端子101电连接。

142.另外,在使用p型常断晶体管30的半导体装置210中,将第二端子102与第二电极32电连接。另一方面,在使用n型常断晶体管10的情况下,将多个第二端子102与第一电极11电连接。因此,在使用p型常断晶体管30的情况下,能够不经由常断晶体管而在接近第三端子103的位置进行开尔文连接。由此,能够进一步抑制驱动电流的调制、迟延或减幅振荡等。

143.此外,如上所述,半导体封装110的上下的端子(第一端子101和第三端子103)是半导体装置210的漏极端子和源极端子,横向端子(第二端子102、第四端子104、第五端子105)是控制端子(栅极端子和开尔文源极端子),因此在形成半桥或全桥电路时,能够将高侧元件的封装和低侧元件的封装接近配置,能够缩短pcb板上的布线。因此,能够降低主环(常断晶体管的源极-漏极间和常通晶体管的源极-漏极间)的寄生电感。

144.另外,也可以不设置第一二极管40和齐纳二极管80。

145.在本实施方式的半导体装置中,也能提供一种能够应用于多种使用方案的半导体装置。

146.(第四实施方式)

147.本实施方式的半导体装置在第三端子103和第一端子101没有被分离这一点上与第一至第三实施方式的半导体装置不同。在此,省略与第一至第三实施方式重复内容的记载。

148.图20是本实施方式的半导体装置220的示意性俯视图。第三端子103为一体,不具有像第三端子103a、103b、103c、

……

、103q那样分离的部分。另外,第二端子102、第五端子105、第一端子101、端子106和端子107也能够被做成同样的结构。

149.在本实施方式的半导体装置中,也能提供一种能够应用于多种使用方案的半导体装置。

150.(第五实施方式)

151.本实施方式的半导体装置在使用金属盘代替键合线进行电连接这一点上与第一至第四实施方式的半导体装置不同。在此,省略与第一至第四实施方式重复内容的记载。

152.图21是本实施方式的半导体装置230的示意性俯视图。使用金属盘129代替键合线128,使用金属盘127代替键合线126。金属盘127和金属盘129例如由cu(铜)、al(铝)等金属形成。另外,关于其他的键合线,也同样地可以使用金属盘。

153.在本实施方式的半导体装置中,也能提供一种能够应用于多种使用方案的半导体装置。

154.(第六实施方式)

155.本实施方式的半导体装置在第一二极管40和齐纳二极管80未设于半导体封装110内这一点上与第三实施方式的半导体装置不同。在此,省略与第一至第五实施方式重复内容的记载。

156.图22是本实施方式的半导体装置240的电路图。图23是本实施方式的半导体装置240的示意性俯视图。通过未将第一二极管40和齐纳二极管80设于半导体封装110内,可以获得半导体装置的设计的自由度提高的优点。

157.在本实施方式的半导体装置中,也能提供一种能够应用于多种使用方案的半导体装置。

158.虽然已经说明了本发明的一些实施方式和实施例,但是这些实施方式和实施例是作为例子而进行提示的,不意在限定发明的范围。这些新的实施方式能够在其他的各种方式中实施,在不脱离发明的主旨的范围内,能够进行各种省略、置换、变更。这些实施方式和其变形包含在发明的范围、主旨中,并且包含在权利要求书中记载的发明及其同等的范围内。

159.(附记)

160.上述的各实施方式总结如下。

161.(第一项)

162.一种半导体装置,具备:半导体封装,具备具有第一电极、第二电极和第一控制电极的n型沟道常断晶体管、具有电连接于第二电极的第三电极、第四电极和第二控制电极的常通晶体管、具有电连接于所述第二控制电极的第一阳极和电连接于所述第一电极或所述

第三电极的第一阴极的第一二极管、以及具有电连接于所述第一电极的第二阳极和电连接于所述第二电极的第二阴极的齐纳二极管;第一端子,设于所述半导体封装中,电连接于所述第一电极;多个第二端子,设于所述半导体封装中,电连接于所述第一电极,分别排列于第一方向上;第三端子,设于所述半导体封装中,电连接于所述第四电极;第四端子,设于所述半导体封装中,电连接于所述第一控制电极;以及多个第五端子,设于所述半导体封装中,电连接于所述第二控制电极,分别排列于第一方向上。

163.(第二项)

164.根据第一项所述的半导体装置,其中,具有第六端子和第七端子的贴片电阻或贴片铁氧体磁珠的所述第六端子电连接于所述多个第二端子中的任一个,所述第七端子电连接于所述多个第五端子中的任一个。

165.(第三项)

166.根据第一项所述的半导体装置,其中,具有第三阳极和第三阴极的第一贴片二极管的所述第三阴极电连接于所述多个第二端子中的任一个,所述第三阳极电连接于所述多个第五端子中的任一个,具有第六端子和第七端子的贴片电阻或贴片铁氧体磁珠的所述第六端子电连接于所述多个第二端子中的任一个,具有第四阳极和第四阴极的第二贴片二极管的所述第四阴极电连接于所述多个第五端子中的任一个,所述第七端子与所述第四阴极电连接。

167.(第四项)

168.根据第一项所述的半导体装置,其中,所述多个第二端子中的任一个和所述多个第五端子中的任一个通过布线电连接。

169.(第五项)

170.根据第一项所述的半导体装置,其中,具有第八端子和第九端子的电容的所述第八端子电连接于所述第五端子。

171.(第六项)

172.根据第五项所述的半导体装置,其中,具有第十端子和第十一端子的电阻的所述第十端子电连接于所述第四端子,所述第十一端子电连接于所述第九端子,具有第五阳极和第五阴极的第二贴片二极管的所述第五阳极电连接于所述第十一端子,所述第五阴极电连接于所述第十端子,所述第二二极管并联电连接于所述电阻。

173.(第七项)

174.根据第一项至第六项中的任一项所述的半导体装置,其中,所述多个第二端子和所述多个第五端子设于所述半导体封装的端部。

175.(第八项)

176.根据第一项至第七项中的任一项所述的半导体装置,其中,在所述多个第二端子和所述多个第五端子之间未设置所述第一端子、所述第三端子和所述第四端子。

177.(第九项)

178.根据第一项至第七项中的任一项所述的半导体装置,其中,所述多个第二端子未隔着所述第一端子、所述第三端子和所述第四端子地与所述多个第五端子邻接。

179.(第十项)

180.根据第一项至第七项中的任一项所述的半导体装置,其中,在所述多个第二端子

与所述多个第四端子之间未设有所述第一端子、所述第三端子和所述第五端子。

181.(第十一项)

182.根据第一项至第七项中的任一项所述的半导体装置,其中,所述多个第二端子未隔着所述第一端子、所述第三端子和所述第五端子地与所述多个第四端子邻接。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。