1.本发明涉及半导体技术领域,特别涉及一种密封环及芯片的封装结构。

背景技术:

2.静电释放(electronic static discharge,esd)是一种客观存在的自然现象,产生的方式多种,如接触、摩擦、感应等。特点是长时间积聚、高电压、低电量、大电流和作用时间短的特点。静电在日常生活中无处不在,人体和周围就带有很高的静电电压,几千伏甚至几万伏。

3.esd事件带来的瞬时大电流脉冲常常会导致芯片中器件失效。esd导致的集成电路失效占有很大的比例。在传统工艺中,由于栅氧化层的厚度较厚,栅氧化层在esd冲击下出现过压击穿的问题不是很严峻。然而随着集成电路工艺的不断进步,栅氧化层不断减薄,晶体管的栅极击穿电压变得越来越小,抵御esd轰击的能力变得越来越弱。

4.在做芯片设计产品的时候,不仅需要考虑到模拟性能,还需要确保芯片的系统级可靠性。在将产品交给客户使用时,不发生系统级可靠性问题。

5.如图1~2所示,现有的芯片技术提出一种不增加版图面积的方法,来改善因为各种不可防范的静电击穿晶体管的栅极,并有效防止封装短路,具体为内部管芯电路外围具有硅片管脚(pad),以及处于硅片管脚外围具有密封环。密封环用来隔离防护因为外部切割应力、潮湿、外部电荷带入,从而影响内部芯片性能。密封环作为隔离槽,也可以改变它的版图布局方法,使之成为一种独特的电容去提高esd性能,但是因为密封环作为电容,最后封装拉线会出现偶发情况,例如:因为拉线问题造成硅片管脚之间短路,如图3所示。因此需要设计一种新的密封环,既可以在不增加面积的情况下对esd防护又可以提高封装可靠性。

技术实现要素:

6.本发明的目的在于提供一种密封环及芯片的封装结构,以解决现有的密封环作为电容封装时因为拉线造成硅片管脚之间短路的问题。

7.为解决上述技术问题,本发明提供一种密封环,包括:

8.多个金属层;

9.其中顶层的金属层被划分为多个金属模块,各所述金属模块之间没有电性连接;

10.所述多个金属层形成至少一个电容。

11.可选的,在所述的密封环中,相邻的两层金属层之间形成一个电容。

12.可选的,在所述的密封环中,所述电容为mom电容。

13.可选的,在所述的密封环中,所述电容连接在电源正极与接地之间。

14.本发明还提供一种芯片的封装结构,包括:

15.密封环,位于所述密封环内的管芯,和设置在所述管芯上的多个硅片管脚;

16.所述密封环包括多个金属层,其中顶层的金属层被划分为多个金属模块,各所述金属模块之间没有电性连接,所述多个金属层形成至少一个电容;

17.各所述硅片管脚越过所述金属模块与芯片管脚键合。

18.可选的,在所述的芯片的封装结构中,相邻的两层金属层之间形成一个电容。

19.可选的,在所述的芯片的封装结构中,所述电容为mom电容。

20.可选的,在所述的芯片的封装结构中,所述硅片管脚包括电源正极管脚和接地管脚;各所述电容连接在所述电源正极管脚和所述接地管脚之间。

21.在本发明提供的密封环及芯片的封装结构中,通过顶层的金属层被划分为多个金属模块,且各所述金属模块之间没有电性连接,不仅实现了在不增加面积的情况下实现了对esd防护,而且又因为各金属模块之间是断开的,降低了短路的概率,提高芯片系统的封装可靠性。

附图说明

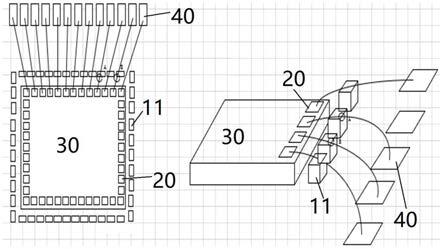

22.图1是现有的提高芯片系统级可靠性的结构俯视示意图;

23.图2是现有的提高芯片系统级可靠性的结构中密封环的剖示图;

24.图3是现有的提高芯片系统级可靠性的结构键合时导线塌陷的示意图;

25.图4是本发明一实施例密封环的剖示图;

26.图5是本发明一实施例芯片的封装结构键合时导线塌陷的示意图;

27.图中所示:10-密封环;11-金属模块;20-硅片管脚;30-管芯;40-芯片管脚。

具体实施方式

28.以下结合附图和具体实施例对本发明提出的密封环及芯片的封装结构作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

29.另外,除非另行说明,本发明的不同实施例中的特征可以相互组合。例如,可以用第二实施例中的某特征替换第一实施例中相对应或功能相同或相似的特征,所得到的实施例同样落入本技术的公开范围或记载范围。

30.本发明的核心思想在于提供一种密封环及芯片的封装结构,以解决现有的密封环作为电容封装时因为拉线造成硅片管脚之间短路的问题。

31.为实现上述思想,如图4所示,本发明提供了一种密封环,包括:多个金属层,其中顶层的金属层被划分为多个金属模块,各个金属模块之间无电性连接。而其他层的金属层局部是不分割开的一整块长板,整体组成连贯的环状,金属层的层数可以根据实际需要进行设置,顶层的金属层(每个金属模块)与其相邻的一层金属层之间相当于电容(图4中未示出,但本领域技术人员可以推测出),第二层金属层与第三层金属层之间相当于另一电容,以此类推,相邻的两个金属层之间均相当于一电容。另外,图4未示意的情况还有:电容可以位于密封环的任意几层金属层中。

32.如图5所示,本实施例提供一种芯片的封装结构,包括:密封环10,位于所述密封环内的管芯30,和设置在所述管芯30上的多个硅片管脚20;所述密封环包括多个金属层top mt、mt1~mtn 1,其中顶层的金属层top mt被划分为多个金属模块11,各所述金属模块11之间没有电性连接,所述多个金属层形成至少一个电容;各所述硅片管脚(即pad)通过导线

(例如:金线)越过所述金属模块与芯片管脚40键合。

33.具体的,在所述的芯片的封装结构中,还包括:设置多个硅片管脚20于所述密封环10中,所述硅片管脚20通过导线越过所述金属模块11上方与芯片管脚40键合,在采用导线将各个硅片管脚20与芯片管脚40分别连接时,若部分导线出现塌陷,导致其与某个金属模块11电性连接,多根塌陷的导线同时接触到同一个金属模块11的概率较低,大概率是塌陷的导线分别接触到不同的金属模块11,如图5所示,因各金属模块11之间没有电性连接,塌陷导线连接的硅片管脚20之间也不会出现短路的情况,从而提高了封装的可靠性。

34.与现有技术相比,现有的密封环其顶层金属层为一整块金属,只要出现2根塌陷的导线接触到顶层金属层,这两个芯片管脚之间就会出现短路;而本实施例的封装结构,只有出现多根塌陷的导线同时接触到同一个金属模块11的情况下才会发生芯片管脚(pad)间的短路,大大提高了芯片封装的可靠性。

35.进一步的,在所述的芯片的封装结构中,还包括:设置管芯30在多个所述硅片管脚20之间,或管芯30上直接形成硅片管脚20;多个金属层中的一层或多层之间(例如mt1~top mt之间)形成电容,可选的,相邻的两层金属层之间形成一个电容,所述电容电连接在电源正极与接地之间。所述电容是金属-氧化物-金属mom电容,所述mom电容位于密封环10的任意一层或几层金属层(例如mt1~mtn 1之间)中。

36.另外,在所述的密封环及芯片的封装结构中,还包括:所述电容与所述硅片管脚20内的放电电路并联。

37.具体的,在密封环及芯片的封装结构中,硅片管脚20包括电源正极管脚20和接地管脚20,所述电容的两个电极分别与电源正极管脚20和接地管脚20连接。

38.本实施例还提供一种提高芯片系统级可靠性的结构,包括:密封环10,其包括多个金属层;所述密封环10的顶层金属层被划分为多个金属模块11,各个金属模块11之间没有电性连接;所述多个金属层形成至少一个电容。

39.在本发明提供的密封环及芯片的封装结构中,通过形成包括多个金属层的密封环10,在所述密封环10的顶层金属层被划分为多个金属模块11,以使各个金属模块11之间没有电性连接,不仅在不增加面积的情况下实现了对esd防护,而且又因为各金属模块11之间没有电性连接的关系(因为各金属模块是断开的),降低了键合时芯片管脚(pad)之间短路的概率,提高芯片系统的封装可靠性。

40.图4示出密封环的剖示图。如图4所示,整芯片包括处于封装结构中心的管芯30、硅片管脚20以及处于硅片管脚20外围的密封环10。在本发明的实施例中,管芯30可以是各种类型的管芯。管芯30可以是小规模集成电路(ssi)、中规模集成电路(msi)。具体而言,管芯30可以是mcu、fpga、soc、电源等等。硅片管脚20可包括用于信号输入和/或输出的硅片管脚、功率硅片管脚、接地硅片管脚、电源钳位硅片管脚等等。

41.密封环10可防止芯片在切割的时候受到机械损伤。密封环10可以屏蔽芯片外的干扰。在本发明的实施例中,由密封环10中的一层或多层金属层形成的电容充当电源和接地之间的电容,用于静电释放esd。通过将密封环中的一层或多层金属层设计成电源与地之间的电容,可有效增加电容且不增加版图面积。

42.在本发明的一些实施例中,mom电容可以位于密封环的任意几层金属层中。例如mom电容可以位于第二金属层mt2和第三金属层mt3中。或者,mom电容可以位于第二金属层

mt2、第三金属层mt3和第四金属层mt4中。或者,mom电容可以位于第三金属层mt3和第四金属层mt4中。或者,mom电容可以位于顶层金属层top mt和第tn 1层金属层mtn 1中。

43.通过利用密封环金属层形成电容,可以在不增加版图面积的情况下,改善因为各种不可防范的esd击穿mos器件的栅极。

44.综上,上述实施例对密封环及芯片的封装结构的不同构型进行了详细说明,当然,本发明包括但不局限于上述实施中所列举的构型,任何在上述实施例提供的构型基础上进行变换的内容,均属于本发明所保护的范围。本领域技术人员可以根据上述实施例的内容举一反三。

45.本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的系统而言,由于与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

46.上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。