具有顶侧存储器模块的ic封装

1.相关申请的交叉引用

2.本技术要求于2019年6月10日提交的题为“ball grid array(bga)package upper connection to memory module”的美国临时专利申请no.62/859,560的权益,其全部内容通过引用结合于此。

技术领域

3.本发明大体上涉及集成电路(ic)封装技术,且更特别地涉及在ic封装的底部表面及顶部表面两者上具有电连接的ic封装。

背景技术:

4.集成电路(ic)封装涉及被覆盖在外壳中的集成电路的半导体裸片(也称为ic芯片),该外壳防止对ic芯片的物理损坏,腐蚀等。另外,提供外壳外部的电连接点,例如引脚或焊盘,以允许与外壳内的ic芯片的电连接。ic芯片、外壳和电连接点有时被称为ic封装。

5.球栅阵列(bga)是表面安装ic封装,其中在bga封装的底表面上的焊盘阵列允许bga封装电连接到印刷电路板(pcb),每个焊盘具有附着的焊料球。bga封装上的焊料球的密度(有时由相邻球之间的距离(间距尺寸)度量)具有上限。结果,对于较大的更复杂的ic芯片,其输入/输出(i/o)连接的数量较多,而较多的输入/输出(i/o)连接需要较多数量的焊料球,则bga封装的整体尺寸增加,这增加了bga封装的成本。

技术实现要素:

6.在一个实施例中,一种印刷电路板(pcb)系统,包括:第一pcb;集成电路(ic)封装,包括:i)封装衬底,ii)电耦合到所述封装衬底的顶表面的主ic芯片,iii)设置在所述封装衬底的底表面上并且电耦合到所述第一pcb的第一接触结构,以及iv)设置在所述封装衬底的所述顶表面上的第二接触结构;存储器模块,包括:i)第二pcb,ii)设置在所述第二pcb的顶表面上的一个或多个存储器ic芯片,以及iii)设置在所述第二pcb的底表面上的第三接触结构;以及内插器,设置在所述ic封装的所述第二接触结构和所述存储器模块的所述第三接触结构之间,以将所述ic封装的所述第二接触结构与所述存储器模块的所述第三接触结构电耦合。

7.在另一个实施例中,一种用于组装pcb系统的方法包括:将ic封装安装到第一pcb,以将所述ic封装的封装衬底的底表面上的第一接触结构电耦合到所述第一pcb,所述ic封装包括主ic芯片;将存储器模块堆叠并对准在所述ic封装上,所述存储器模块包括:i)第二pcb,ii)设置在所述第二pcb上的一个或多个存储器ic芯片,以及iii)设置在所述第二pcb的底表面上的第二接触结构;以及将设置在存储器模块的第二pcb的底表面上的第二接触结构电耦合到设置在封装衬底的顶表面上的第三接触结构。

附图说明

8.图1a是示出根据一个实施例的具有设置在pcb上的集成电路(ic)封装的示例印刷电路板(pcb)的俯视图的示图。

9.图1b是示出根据一个实施例的被配置成设置在图1a所示的ic封装上的示例性存储器模块的顶视图的示图。

10.图1c是示出根据一个实施例的示例pcb系统的顶视图的图,该示例pcb系统包括设置在图1a所示的ic封装上的图1b的存储器模块。

11.图2a至图2c是根据一个实施例的图1c的示例pcb系统的不同视图。

12.图3是根据一个实施例的用于组装pcb系统的示例的流程图。

具体实施方式

13.在下面描述的实施例中,印刷电路板(pcb)系统包括第一pcb和集成电路(ic)封装,其具有i)封装衬底,ii)电耦合到封装衬底的顶表面的主ic芯片,iii)设置在封装衬底的底表面上并且电耦合到第一pcb的第一接触结构,以及iv)设置在封装衬底的顶表面上的第二接触结构。该pcb系统还包括存储器模块,该存储器模块具有i)第二pcb,ii)设置在第二pcb上的一个或多个存储器ic芯片,以及iii)设置在第二pcb的底表面上的第三接触结构。pcb系统还包括设置在ic封装的第二接触结构和存储器模块的第三接触结构之间的内插器,以将ic封装的第二接触结构与存储器模块的第三接触结构电耦合。

14.在一些实施例中,因为用于ic芯片的一些输入/输出(i/o)连接被设置在封装衬底(例如,第二接触结构)的顶表面上,所以与如果所有i/o连接被设置在封装衬底的底表面上相比,用于设置在封装衬底的底表面上的ic芯片的i/o连接(例如,第一接触结构)的数目较少,并且因此ic封装的总尺寸被减小。例如,对于球栅阵列(bga)封装,焊料球的密度具有实际的上限,并且因此大量的焊料球需要更大的ic封装尺寸。因此,在ic封装将bga封装技术用于第一接触结构的一些实施例中,减少第一接触结构的数量有助于减小ic封装的整体尺寸,从而降低ic封装的成本。

15.另外,根据一些实施例,由于设置在封装衬底的底表面上的ic芯片的i/o连接(例如,第一接触结构)的数量较少(与如果所有i/o连接设置在封装衬底的底表面上相比),所以电耦合到ic封装的第一接触结构的第一pcb上的迹线的数量较少。因此,根据一些实施例,与其中所有i/o连接设置在封装衬底的底表面上的封装衬底相比,第一pcb的复杂性降低(例如,层数减少),从而降低了第一pcb的成本。

16.图1a是示出根据一个实施例的示例性pcb 100(本文中有时称为“主pcb”)的俯视图的示图。根据一个实施例,pcb 100包括安装在pcb 100的顶表面108上的ic封装104。ic封装104包括具有顶表面116和与顶表面116相对的底表面(未示出)的衬底112。ic芯片120耦合到衬底112的顶表面116。

17.根据各种实施例,衬底112包括合适的绝缘材料(也称为介电材料),诸如基于环氧树脂的层压衬底、基于树脂的双马来酰亚胺三嗪(bt)衬底等。衬底112是相对刚性的,以向ic芯片120提供机械支撑。在一些示例中,衬底112包括多层金属迹线,例如铜线等,该多层金属迹线之间具有绝缘材料。在不同实施例中,不同层上的迹线通过导电通孔连接。

18.在一个实施例中,电接触结构形成在顶表面116和底表面两者上,以将ic芯片电连

接到ic封装120外部的电子元件,例如主pcb 100上的电子元件和将参照图1b讨论的存储器模块上的电子元件。

19.衬底112的底表面包括作为电子接触结构的多个i/o焊盘(未示出),其允许将pcb 100电连接到ic芯片120的第一i/o。在一个实施例中,ic封装104使用bga技术,并且多个i/o焊盘(未示出)设置在阵列中,其中焊料球(未示出)连接到多个i/o焊盘。

20.ic芯片120可以是任何合适的集成电路芯片,例如集成电路处理器、控制器、收发器、开关设备、片上系统等。ic芯片120包括用于提供计算和/或处理功能的各种电路。在一些示例中,ic芯片120从ic封装104外部的组件接收诸如模拟信号、数字信号、控制信号、数据信号等合适的信号,并处理所接收的信号。在一些示例中,ic芯片120产生合适的信号,例如模拟信号、数字信号、控制信号、数据信号等,并将所产生的信号输出到ic封装104外部的组件。

21.在一个实施例中,ic封装104用于分组交换的高速网络交换设备中。例如,ic芯片120包括用于分组处理的核心电路和用于接口(输入/输出)处理(例如接收和/或发送携带分组的信号)的外围电路。在一个示例中,ic芯片120包括一个或多个分组处理器,其被配置为执行分组处理,包括但不限于分组转发。ic芯片120还包括接口电路,例如调制/解调电路、用于排队分组的存储器电路等。

22.衬底112提供从ic芯片121的输入/输出到形成在衬底112的底表面和顶表面116上的接触结构的互连。根据一个实施例,ic芯片120包括电连接到形成在ic芯片120上的内部电路的i/o焊盘(未示出),并且衬底112的顶表面116包括与ic芯片120上的凸点结构匹配的焊料凸点(未示出)。ic芯片120设置在顶表面116上,使得ic芯片120上的凸点结构与衬底112的顶表面116上的焊料凸点对准。然后,执行回流工艺以形成凸点结构和焊料凸点的连接。

23.在其它实施例中,ic芯片120被接线键合以形成与衬底112的电连接。

24.pcb 100包括设置在pcb 100的顶表面108上的多个焊盘(未示出),这些焊盘在位置上与ic封装104的底表面上的多个i/o焊盘(未示出)相对应并且电连接到ic封装104的底表面上的多个i/o焊盘(未示出)。在ic封装104使用bga技术的实施例中,设置在pcb 100的顶表面108上的多个焊盘(未示出)使用多个焊料球电连接到ic封装104的底表面上的多个i/o焊盘(未示出)。

25.pcb 100还包括多个迹线124,其电耦合到设置在pcb 100的顶表面108上的多个焊盘(未示出),并且其电连接到ic封装104的底表面上的多个i/o焊盘(未示出)。迹线124将设置在pcb 100上的其它电子元件(未示出)电耦合到ic芯片120的第一i/o。

26.ic封装104还包括覆盖ic芯片120同时使衬底112的顶表面116的外围部分不被覆盖的盖140。在一个实施例中,盖140包括有助于在操作期间从ic芯片120散热的散热块(heat slug)。在一些实施例中,盖140包括覆盖ic芯片120的金属材料,例如以保护ic芯片120并在ic芯片120上电时在操作期间帮助散热。

27.多个内插器152设置在ic封装104的衬底112的顶表面116上。在一个实施例中,每个内插器152包括电连接到衬底112的多个迹线(未示出)的多个接触结构。衬底112的多个迹线(未示出)将ic芯片120的第二i/o与内插器152的接触结构电耦合。在说明性示例中,根据一个实施例,每个内插器152包括在内插器152的至少一侧上的多个压缩接触,其允许(结

合图1b和图1c所描述的)存储器模块电耦合到ic芯片120的第二i/o。例如,根据一个实施例,pcb系统100包括被配置为向pcb 100和(结合图1b和图1c所描述的)存储器模块施加压缩力以将存储器模块与ic芯片120的第二i/o电耦合的力部件。

28.图1b是示出根据一个实施例的示例性存储器模块156的顶视图的图,该存储器模块156被配置成安装在图1a的ic封装104之上并经由多个内插器152(图1a)电耦合到ic芯片120(图1a)。

29.存储器模块156包括设置在pcb 164上的一个或多个存储器ic 160,该存储器模块156在此有时称为“存储器模块pcb 164”。存储器模块pcb 164具有顶表面166和底表面(未示出)。在一个实施例中,一个或多个存储器ic 160设置在存储器模块pcb 164的顶表面166上。在另一实施例中,一个或多个存储器ic 160设置在存储器模块pcb 164的底表面166上。

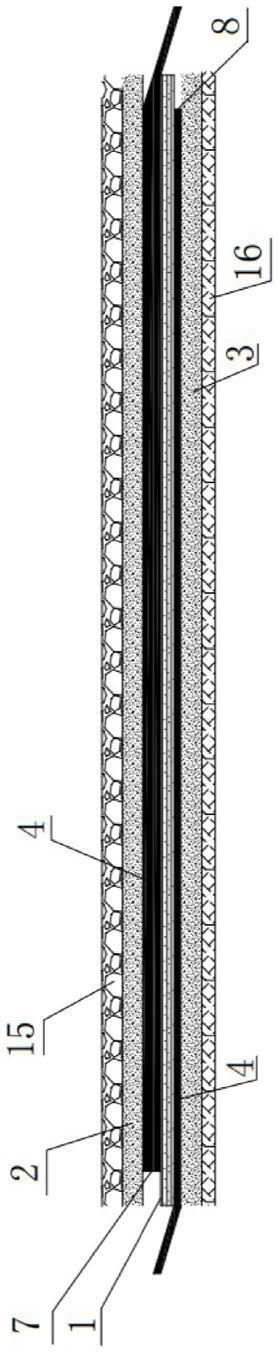

30.在一些实施例中,在存储器模块pcb 164上没有设置处理器ic,并且存储器模块156免去了任何处理器ic。在一些实施例中,在存储器模块pcb 164上不设置除存储器ic之外的ic,并且存储器模块156免去了除存储器ic之外的任何ic。在其它实施例中,除了一个或多个存储器ic 160之外,处理器ic设置在存储器模块pcb 164上。在一些实施例中,除了一个或多个存储器ic 160之外,在存储器模块pcb 164上还设置与存储器ic和处理器ic不同的一个或多个ic。

31.存储器模块pcb 164包括多个外边缘168和形成pcb存储器模块164中的开孔176的多个内边缘172。开孔176的尺寸被设计成容纳ic封装104(图1a)的盖140,如将结合图1c所描述的。pcb存储器模块164包括在存储器模块pcb 164的底表面上邻近pcb存储器模块164的内边缘172设置的多个电接触结构180。在一个实施例中,电接触结构180围绕开孔176设置。电接触结构180被配置以当存储器模块156安装在ic封装104之上时与ic封装104(图1a)的内插器152电连接,如下文参看图1c所讨论的。

32.存储器模块pcb 164包括将存储器ic 160电耦合到电接触结构180的多个迹线184。

33.根据一些实施例,存储器模块pcb 164与主pcb 100相比具有明显更少的部件,并且因此比主pcb 100更小且具有更少的层。结果,根据一些实施例,存储器模块pcb 164的成本显著小于主pcb 100。另外,通过将存储器ic 160设置在存储器模块pcb 164上而不是主pcb 100上,可以减少主pcb 100的层数(与设置有存储器ic 160的主pcb相比),从而至少在一些实施例中降低了主pcb 100的成本。此外,至少在一些实施例中,通过将存储器ic 160设置在存储器模块pcb 164上而不是主pcb 100上,可以将存储器ic 160定位为更靠近ic芯片120(与设置有存储器ic 160的主pcb相比),从而提高性能。

34.根据一个实施例,电接触180的密度高于ic封装104的底表面上的bga焊料球的密度。

35.图1c是示出根据一个实施例的包括图1a的pcb 100的示例pcb系统192的顶视图的示图,其中图1b的示例存储器模块156安装在ic封装104之上。电接触结构180电连接到内插器152(图1a,而图1c中未示出)。结果,ic芯片120的第二i/o经由存储器模块pcb 164的内插器152、电接触结构180和迹线124(图1b,现在在图1c中示出)电耦合到存储器ic 160。ic封装104的盖140容纳在开孔176内(图1b,现在在图1c中示出)。

36.尽管存储器模块156在上面被描述为包括一体的存储器模块pcb 164的相应一体

模块,但是在其它实施例中,存储器模块156包括多个分离的子模块,每个子模块具有相应的pcb,如图1b和图1c中的虚线192所指示的。

37.图2a至图2c是根据一个实施例的图1c的pcb系统192的不同视图,但是仅示出了存储器模块156的一部分(或仅单个存储器子模块)以帮助示出pcb系统192。图2a示出了pcb系统192的透视图(但是仅示出了存储器模块156的一部分,或者仅示出了单个存储器子模块),图2b示出了pcb系统192的截面图(但是仅示出了存储器模块156的一部分),并且图1c示出了pcb系统192的顶视图(但是仅示出了存储器模块156的一部分,或者仅示出了单个存储器子模块)。

38.在图2a至图2c所示的示例中,衬底112包括形成在衬底112的顶表面116上的接触结构204。在一个实施例中,衬底112包括金属迹线(未示出),其将(ic芯片120附接到其上的)焊料凸点电连接到接触结构204。

39.根据本公开的一个方面,接触结构204和ic芯片120设置在衬底112的相同表面侧上。在一些实施例中,接触结构204设置在围绕ic芯片120的衬底112的外围区域,例如ic芯片120的盖140和衬底112的边缘之间的区域。

40.接触结构204是任何合适的接触结构。在一个实施例中,至少一些接触结构204中的每一个包括焊盘和沉积在焊盘上的焊料球。在另一个实施例中,至少一些接触结构204中的每一个包括焊盘。在另一实施例中,至少一些接触结构204中的每一个包括引脚。

41.在图2a中,接触结构204显示为圆形。在其它实施例中,接触结构204具有其它合适的形状,例如球形、方形、引脚形等。

42.接触结构204被配置为能够使用适当的技术电连接到其它部件。例如,在一个实施例中,接触结构204被配置以经由内插器152与存储器模块156上的电接触180进行电连接。

43.更具体地,内插器152包括多个互连结构212,以将存储器模块156上的电接触180的相应接触结构216与ic封装104的接触结构204电连接。每个互连结构212被配置为使用适当的技术形成与第二接触结构204的第一连接以及与接触结构216的第二连接。在一个实施例中,每个互连结构212是对第一连接和第二连接使用压缩连接的双重压缩结构。在另一个实施例中,每个互连结构212是具有焊料球的单个压缩结构,该单个压缩连接使用用于第一连接的焊料球和用于第二连接的压缩连接。

44.图2a包括根据一个实施例的被配置用于压紧连接的互连结构212的一侧的特写图。根据一个实施例,互连结构212包括从内插器152的表面突出的金属舌220,且金属舌220可在压缩力下被推入表面中。在其它实施例中,使用不同于互连结构212的其它合适的互连结构。

45.在一个实施例中,pcb系统100包括力产生部件,该力产生部件可施加压缩力以使内插器152将存储器模块156与接触结构204互连。例如,主pcb 100和存储器模块156被设计和制造成具有可对准以设置螺栓的孔。在将ic封装104安装在主pcb 100上之后,对准并堆叠内插器152和存储器模块156。注意,可插入合适的间隔件224以使调平主pcb 100上的存储器模块156。然后,将螺栓228和232紧固到对应的螺母236和240,以将堆叠的第一pcb 110,内插器130和pcb模块140锁定就位,并施加压紧力以使内插器152将存储器模块156的接触结构216与ic封装104的接触结构204互连。

46.在各种实施例中,主pcb 100和存储器模块pcb 164分别包括设置在介电材料的多

层夹层结构上的多层金属迹线,例如铜线等。在一些示例中,主pcb 100和存储器模块pcb 164具有不同数量的金属层。例如,主pcb 100具有比存储器模块pcb 164更多的金属层。存储器模块pcb 164为存储器ic 160和诸如其它ic封装、电阻器、二极管、电容器、晶体管等的任何其它合适的电子部件(如果有的话)提供附加的电连接支持。

47.根据本发明的一个方面,内插器152具有高密度和低轮廓。在一个示例中,内插器152具有0.80mm的间距栅格(例如,小于用于典型bga的焊料球间距)和1mm的主体高度(用于最短信号路径的0.33mm高度)。因此,在一个示例中,主pcb 100和存储器模块pcb 164之间的距离小于ic封装104的高度。

48.在一个实施例中,内插器152的间距栅格小于bga焊料球间距要求。在一个示例中,ic封装104的顶表面116上的接触结构204的密度高于ic封装104的底表面上的bga焊料球的密度。在一些实施例中,与如果内插器152的间距栅格和/或接触结构204的密度与bga焊料球的间距要求一样的情况相比,内插器152的较小间距栅格和/或接触结构204的密度允许ic封装衬底112的尺寸得以减小,因此降低了ic封装104的成本。

49.在一个实施例中,与诸如封装的电镀通孔(pth)式通孔、pcb pth、pcb等的电连接技术相比,通过内插器130从ic封装104的接触结构204到存储器模块156的电连接提供了相对较短的信号路径。因此,从接触结构204经由内插器152到存储器模块156的电连接比其它互连技术具有较小的衰减,且因此可用于较高速度的信号。

50.如图2b所示,衬底112包括形成在衬底112的底表面264上的接触结构260。在一个实施例中,衬底112包括金属迹线(未示出),其将(ic芯片120附接到其上的)焊料凸点电连接到接触结构260。在一个实施例中,ic封装104是bga封装,并且每个第一接触结构260包括焊盘和沉积在焊盘上的焊料球。在另一实施例中,ic封装104是平面栅格阵列(lga)封装,并且每个第一接触结构260包括焊盘。在另一个实施例中,ic封装104是针脚栅格阵列(pga)封装,并且每个第一接触结构260包括针脚。

51.注意,在一些实施例中,使用与衬底112的底表面264上的接触结构260不同的技术来实现衬底112的顶表面116上的第二接触结构204。例如,根据一个实施例,使用焊盘和焊料球来实现接触结构260,并且使用没有焊料的焊盘来实现接触结构204。

52.根据本公开的一个方面,接触结构260分别被配置为能够使用合适的技术电连接到部件。在一个示例中,接触结构260被配置为使用焊接技术实现到主pcb 100的电连接。例如,当ic封装104安装在主pcb 100上时,执行回流焊工艺以形成焊接接头,因此接触结构260连接到主pcb 100上的相应接触结构。

53.现在参考图1a至图1c和图2a至图2b,在一些实施例中,ic芯片120包括处理器(诸如用于交换设备的分组处理器,中央处理单元(cpu),数字信号处理器(dsp)等),并且存储器ic 160包括存储器设备(例如,随机存取存储器(ram),只读存储器(rom),诸如闪存的固态存储器等),这些存储器设备在执行处理任务,操作等时由处理器使用。ic芯片120上的处理器经由接触结构204,内插器152和电接触180访问存储器ic160。

54.因为存储器ic 160被设置在存储器模块156上,并且ic芯片120可以经由封装衬底112的顶表面116上的接触结构204而不是经由封装衬底112的底表面264上的接触结构260来访问存储器ic 160,所以封装衬底112的底表面264上的接触结构260的数量得以减少,这允许封装衬底112的尺寸得以减小。封装衬底112的制造通常相对昂贵(与典型的pcb和存储

器模块pcb 164相比),并且衬底112的成本随着衬底112的尺寸增加而增加。因此,根据一些实施例,减小封装衬底112的尺寸降低了封装衬底112的成本。另外,因为存储器ic 160设置在存储器模块156上,并且ic芯片120可以经由封装衬底112的顶表面116上的接触结构204而不是经由封装衬底112的底表面264上的接触结构260来访问存储器ic 160,所以减小了封装衬底112的底侧上的bga中的i/o的数量,这减少了封装衬底112中从封装衬底112的顶侧166到封装衬底的底侧的通孔的数量。另外,至少在一些实施例中,因为穿过封装衬底112的多个层的通孔的数目,所以减小了封装衬底112中的层的数目。根据一些实施例,对所需通孔数量的放松和/或封装衬底112的层数的减少也降低了封装衬底112的成本。

55.此外,根据一些实施例,因为存储器ic 160被设置在存储器模块156上而不是主pcb 100上,所以还降低了主pcb 100的复杂性,例如,降低了pcb 100的层数。pcb 100的成本通常随着层数的增加而增加。因此,根据一些实施例,减少pcb 100中的层数降低了pcb 100的成本。

56.此外,根据一些实施例,因为存储器ic 160被设置在存储器模块156上而不是设置在具有电耦合到ic封装104的其它部件的主pcb 100上,所以与如果存储器ic 160被设置在主pcb 100上相比,存储器ic 160可以被定位为更靠近ic封装104。例如,如果存储器ic 160被设置在主pcb 100上,则存储器ic 160将需要位于离ic封装104更远的位置(与pcb系统192相比),以允许在ic封装104和主pcb 100上的其它部件之间布线迹线。至少在一些实施例中,通过将存储器ic定位为更靠近ic封装104,使得性能得以提高。

57.图3是根据一个实施例的组装pcb系统的示例方法300的流程图。在一个实施例中,执行方法300以组装pcb系统,例如上面参考图1a至图1c和图2a至图2c描述的示例性pcb系统192,并且参考图1a至图1c和图2a至图2c描述方法300仅用于解释的目的。在其它实施例中,执行方法300以组装不同于示例性pcb系统192的合适的pcb系统。

58.在框304,通过将ic封装的第一接触结构耦合到第一pcb,将ic封装安装到第一pcb。例如,根据一个实施例,ic封装104安装在主pcb 100上。更具体地,根据一个实施例,接触结构260与主pcb 100上的相应接触结构对准并连接到主pcb 100上的相应接触结构。在示例中,执行回流焊工艺以形成焊料接头,该焊料接头形成ic封装104和主pcb 100之间的电连接,其中接触结构260连接到主pcb 100上的相应接触结构。

59.在框308,存储器模块被堆叠在ic封装上并与ic封装对准。在一个实施例中,框308包括在存储器模块(例如,存储器模块156)和ic封装(例如,ic封装104)之间设置内插器(例如,内插器152)。在一个实施例中,框308包括将内插器152与ic封装104上的接触结构204对准。在一个实施例中,存储器模块156的存储器模块pcb 164和主pcb 100被设计和制造成具有孔,所述孔可被对准以设置螺栓或其它合适的紧固件。

60.在框312,存储器模块电连接到ic封装。在一个实施例中,在框312处将存储器模块电连接到ic封装包括:使用机械紧固件将存储器模块与ic封装按压在一起,以在置于存储器模块与ic封装之间的内插器上施加压紧力。例如,螺栓112和114被紧固到相应的螺母113和115,以将主pcb 110和存储器模块156压在一起,以施加压缩内插器152的力,这使得内插器152将存储器模块156的接触结构216与ic封装104的接触结构204互连。

61.注意,在各种实施例中,可在方法300之前,在方法300中的步骤之间及/或在方法300之后执行其它合适的方法动作,以用于半导体器件制造。作为说明性示例,根据一个实

施例,在将ic封装104安装到主pcb 100之前,将存储器模块156安装到ic封装104。

62.实施例1:一种印刷电路板pcb系统,包括:第一pcb;集成电路ic封装,所述集成电路ic封装包括:i)封装衬底,ii)主ic芯片,电耦合到所述封装衬底的顶表面,iii)第一接触结构,设置在所述封装衬底的底表面上并且电耦合到所述第一pcb,以及iv)第二接触结构,设置在所述封装衬底的顶表面上;存储器模块,包括:i)第二pcb,ii)一个或多个存储器ic芯片,设置在所述第二pcb的顶表面上,以及iii)第三接触结构,设置在所述第二pcb的底表面上;以及内插器,其设置在所述ic封装的所述第二接触结构和所述存储器模块的所述第三接触结构之间,以将所述ic封装的所述第二接触结构与所述存储器模块的所述第三接触结构电耦合。

63.实施例2:根据实施例1所述的pcb系统,其中所述内插器被配置成在所述内插器的至少一侧上提供压缩接触,以将所述ic封装的所述第二接触结构与所述存储器模块的所述第三接触结构电耦合。

64.实施例3:根据实施例1或2中任一项所述的pcb系统,其中:存储器模块包括多个单独的存储器子模块;以及所述第二pcb包括分别对应于所述多个单独的存储器子模块的多个单独的第二pcb,每个单独的第二pcb具有设置在所述单独的第二pcb的顶表面上的一个或多个存储器ic芯片,以及iii)设置在所述单独的第二pcb的底表面上的所述第三接触结构的子集。

65.实施例4:根据实施例1或2中任一项实施例所述的pcb系统,其中所述存储器模块包括一体的第二pcb。

66.实施例5:根据实施例1-4中任一项所述的pcb系统,其中:所述ic封装包括包围所述主ic芯片并使设置在所述封装衬底的顶表面上的所述第二接触结构未被覆盖的盖;该存储器模块的第二pcb包括:i)多个外边缘,以及ii)多个内边缘,这些内边缘限定了开孔;并且其中所述ic封装的所述盖被设置在由所述第二pcb的所述多个内边缘限定的所述开孔内。

67.实施例6:根据实施例5所述的pcb系统,其中:包围所述主ic芯片的盖包括散热块;其中所述散热块设置在由所述第二pcb的所述多个内边缘限定的所述开孔内。

68.实施例7:根据实施例5所述的pcb系统,其中:所述存储器模块的第三接触结构被设置在第二pcb上靠近所述多个内边缘;所述pcb系统包括多个内插器,所述多个内插器围绕所述主ic芯片设置在所述ic封装的所述第二接触结构和所述存储器模块的所述第三接触结构之间。

69.实施例8:根据实施例1-7中任一项所述的pcb系统,其中:所述ic封装的第二接触结构围绕所述ic芯片设置在所述封装衬底上。

70.实施例9:根据实施例1-8中任一项所述的pcb系统,其中:所述第一pcb具有第一数目的层;并且所述第二pcb包括第二数目的层,所述第二数目小于所述第一数目。

71.实施例10:根据实施例1-9中任一项所述的pcb系统,其中:所述主ic芯片包括:处理器;多个电气部件,其被设置在所述第一pcb上;以及所述处理器i)经由设置在所述封装衬底和所述内插器的所述顶表面上的所述第二接触结构与所述存储器模块的所述一个或多个存储器ic芯片接口连接,以及ii)经由设置在所述封装衬底的所述底表面上的所述第二接触结构与设置在所述第一pcb上的多个电气部件接口连接。

72.实施例11:根据实施例1-10中任一项所述的pcb系统,其中:设置在封装衬底的底表面上的第一接触结构包括球栅阵列(bga)接触结构。

73.实施例12:根据实施例11所述的pcb系统,其中:设置在封装衬底的底表面上的bga接触结构的第一密度小于设置在封装衬底的顶表面上的第二接触结构的第二密度。

74.实施例13:一种用于组装印刷电路板pcb系统的方法,包括:将集成电路ic封装安装到第一pcb,以将所述ic封装的封装衬底的底表面上的第一接触结构电耦合到所述第一pcb,所述ic封装包括主ic芯片;将存储器模块堆叠并对准在所述ic封装上,所述存储器模块包括:i)第二pcb,ii)设置在所述第二pcb上的一个或多个存储器ic芯片,以及iii)设置在所述第二pcb的底表面上的第二接触结构;以及将设置在存储器模块的第二pcb的底表面上的第二接触结构电耦合到设置在封装衬底的顶表面上的第三接触结构。

75.实施例14:根据实施例13所述的方法,进一步包括:在设置于所述存储器模块的所述第二pcb的所述底表面上的所述第二接触结构与所述第三接触结构之间设置内插器,以将所述存储器模块的所述第二接触结构与设置在所述封装衬底的所述顶表面上的所述第三接触结构互连。

76.实施例15:根据实施例14所述的方法,进一步包括:施加压缩力以将所述存储器模块和所述ic封装按压在一起,以使所述内插器将所述存储器模块的所述第二接触结构与所述ic封装的所述第三接触结构电连接。

77.实施例16:根据实施例15所述的方法,其中施加所述压缩力包括:紧固螺栓以施加所述压缩力。

78.实施例17:根据实施例13-16中任一项所述的方法,其中:设置在封装衬底的底表面上的第一接触结构包括球栅阵列(bga)接触结构;以及将所述ic封装安装到所述第一pcb包括:执行回流焊工艺以将所述bga接触结构连接到所述第一pcb。

79.实施例18:根据实施例13-17中任一项所述的方法,其中:所述存储器模块包括多个单独的存储器子模块,并且所述第二pcb包括分别对应于所述多个单独的存储器子模块的多个单独的第二pcb,每个单独的第二pcb具有设置在所述单独的第二pcb上的一个或多个存储器ic芯片,并且每个单独的第二pcb具有设置在所述单独的第二pcb的底表面上的所述第二接触结构的子集;在ic封装上堆叠和对准存储器模块包括在ic封装上堆叠和对准每个单独的存储器子模块;以及将所述存储器模块的所述第二接触结构电耦合到所述封装衬底的所述第三接触结构包括:将每个存储器子模块的所述第二接触结构的每个子集电耦合到所述封装衬底的所述第三接触结构的相应子集。

80.实施例19:根据实施例13-17中任一项所述的方法,其中:所述存储器模块包括一体的第二pcb,其中所述第二接触结构设置在所述单体的第二pcb的底表面上;以及将所述存储器模块的所述第二接触结构电耦合到所述封装衬底的所述第三接触结构包括:将设置在所述存储器模块的所述一体的第二pcb的所述底表面上的所述第二接触结构电耦合到所述封装衬底的所述第三接触结构。

81.实施例20:根据实施例13-19中任一项所述的方法,其中:在ic封装上堆叠和对准存储器模块包括在ic封装上堆叠和对准免去处理器的存储器模块。

82.虽然已经参考特定的实施例描述了本发明,这些实施例仅仅是说明性的而不是对本发明的限制,但是在不脱离本发明的范围的情况下,可以对所公开的实施例进行改变、添

加和/或删除。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。