一种sic mosfet子模组单元压接型封装

技术领域

1.本发明属于电力半导体封装技术领域,具体涉及一种sic mosfet子模组单元压接型封装。

背景技术:

2.sicmosfet作为宽禁带功率半导体器件,相比于传统的硅器件具有很多优势,比如工作温度更高、通态损耗更低、开关频率更高和临界击穿场强更大等特点。随着碳化硅功率器件应用的逐渐推广,目前针对高压碳化硅功率器件的封装,还没有成熟统一的形式。

3.对于硅器件的传统压接式结构,主要以凸台式硬压接为主。采用凸台式硬压接结构的主要有toshiba的iegt系列和westcode的presspack系列,最高电压电流等级达到4.5kv/3ka。该种结构虽然解决了焊接型封装中脆弱的键合引线面临的问题,但在实际应用中依然存在新的挑战。

4.首先,该结构利用一体式的钼盘凸台,对芯片施加刚性压力。为了保证接触电阻尽可能的低,施加的压力往往很大,这就对钼盘凸台的加工精度和芯片尺寸的一致性提出了非常高的要求,如果加工精度不够高或者同一个模块内部芯片之间的尺寸一致性不好,就会出现不同的芯片之间所受应力差别很大的情况,会导致芯片受力超过限度从而发生物理损坏。

5.另外,即便是加工精度和芯片尺寸的一致性符合要求,在功率模块实际运行中,由于芯片之间的布局在整体上不可能完全一致,以及模块运行中内部温度分布也不可能完全相同。这两个因素导致了不同位置的芯片和钼盘凸台会发生不同程度的微观形变,而由于凸台式硬压接结构给整体施加固定的应力,在面对不同程度的微观形变时无法保证芯片之间受力平均,最终可能引起界面接触电阻相差过大或者芯片出现物理层面的损坏。

6.最后,由于芯片和电极的连接界面没有了传统的焊层和键合线,全靠施加应力来保证接触可靠,导致在功率模块内部无法使用硅凝胶作为绝缘介质,只能使用气体绝缘,而气体的绝缘性能往往不如硅凝胶介质,从而导致模块在高压应用领域内会面临绝缘的问题。

7.以上这三点都是凸台式硬压接封装结构面临的新问题。因此针对高压碳化硅功率器件的封装,既要实现其压接型封装结构,也要面对传统凸台式硬压接型封装所存在的种种缺陷,提出新的压接型封装结构,才能充分发挥高压碳化硅器件本身性能的优势。

技术实现要素:

8.本发明的目的在于提供一种sic mosfet子模组单元压接型封装,以克服碳化硅器件难以进行压接型封装的问题,同时解决了传统凸台式硬压接封装结构存在的内部芯片受力不均和无法使用硅凝胶绝缘的问题,本发明提高了模块的功率密度,采用硅凝胶作为填充绝缘材料,提高了装置可靠性,可以应用在高压领域。

9.为达到上述目的,本发明采用如下技术方案:

10.一种sic mosfet子模组单元压接型封装,包括:sicmosfet子单元阵列、栅极碟簧及连接部件、pcb基板、栅极端子、辅助源极端子和源极底板;

11.所述sicmosfet子单元阵列由m个sic mosfet子单元组成;每个sic mosfet子单元均通过若干栅极碟簧及连接部件与pcb基板的上表面连接,所述pcb基板的下表面连接至源极底板,所述栅极端子设置在pcb基板的一侧,所述辅助源极端子设置在源极底板的一侧,且栅极端子和辅助源极端子位于同一方位;

12.所述sic mosfet子单元包括sicmosfet子模组阵列、漏极端子、dbc陶瓷基板、外壳、源极碟簧及连接部件和源极端子;所述sicmosfet子模组阵列包括若干sicmosfet子模组,所述sicmosfet子模组包括源极钼片、sicmosfet芯片阵列和漏极钼片;

13.所述源极钼片下表面对称设有n个第一凸起,所述第一凸起分别与n个sicmosfet芯片阵列相连,并露出sicmosfet芯片阵列的栅极和部分源极;所述漏极钼片上表面设置有n个用于连接和定位sicmosfet芯片阵列的第二凸起,第二凸起与所述sicmosfet芯片阵列的漏极相连;所述sicmosfet芯片阵列由n个sicmosfet芯片组成;

14.所述sicmosfet子模组阵列由x个sicmosfet子模组组成,分布成y行;所述dbc陶瓷基板设置有y 1个,且y 1个dbc陶瓷基板和y行sicmosfet子模组间隔设置,所述漏极钼片下表面和dbc陶瓷基板下表面均与漏极端子上表面相连,所述外壳底部边缘与漏极端子边缘相连,所述源极端子通过x个源极碟簧及连接部件分别与x个sicmosfet子模组连接,所述源极底板上表面与源极端子相接触。

15.进一步地,所述第一凸起、第二凸起和sicmosfet芯片阵列的数量均为4个、6个或8个。

16.进一步地,所述第一凸起与sicmosfet芯片阵列通过纳米银烧结相连,所述第二凸起与sicmosfet芯片阵列通过纳米银烧结相连。

17.进一步地,所述sic mosfet子模组的数量为8个,分布成2行。

18.进一步地,所述sicmosfet芯片阵列的栅极通过键合线与dbc陶瓷基板相连;所述漏极端子的上表面和漏极钼片的下表面通过纳米银烧结相连;所述漏极端子的上表面和dbc陶瓷基板的下表面通过纳米银烧结相连。

19.进一步地,所述源极碟簧及连接部件包括第一铜柱,第一铜柱上套设有第一碟簧,第一碟簧的外侧设置有第一铜片,所述第一铜柱与源极钼片的上表面相接触,所述第一铜片和源极端子通过焊接相连,形成一个整体。

20.进一步地,所述漏极端子一侧填充有能够覆盖sicmosfet子模组阵列和第一铜柱的硅凝胶。

21.进一步地,所述sic mosfet子单元的数量为4个。

22.进一步地,所述栅极碟簧及连接部件包括第二铜柱,第二铜柱上套设有第二碟簧,第二碟簧的外侧设置有第二铜片;所述pcb基板上表面有覆铜,所述第二铜片和pcb基板的上表面覆铜通过焊接相连;所述第二铜柱和dbc陶瓷基板相接触。

23.进一步地,所述辅助源极端子设置有两个,且两个辅助源极端子对称设置在栅极端子两侧,辅助源极端子和栅极端子和外电路相连。

24.与现有技术相比,本发明具有以下有益的技术效果:

25.本发明在sicmosfet子单元内部,同时将x个sicmosfet子模组排列组成y行

sicmosfet子模组阵列,使用源极碟簧及连接部件分别对每一个sicmosfet子模组施加均匀可调的弹性压力,进一步优化了sic芯片压接时的受力分布,同时可以使用硅凝胶作为绝缘,实现了更高的可靠性,也增加了功率密度,多个sicmosfet子单元共同组成功率模块,可以结合实际应用所需,自由调节sicmosfet子模组和sicmosfet子单元的数量,整体结构实现了模块化封装,安装容易,故障排查和缺陷模块更换简单。

附图说明

26.说明书附图用来提供对本发明的进一步理解,构成本发明的一部分,本发明的示意性实施例及其说明用于解释本发明,并不构成对本发明的不当限定。

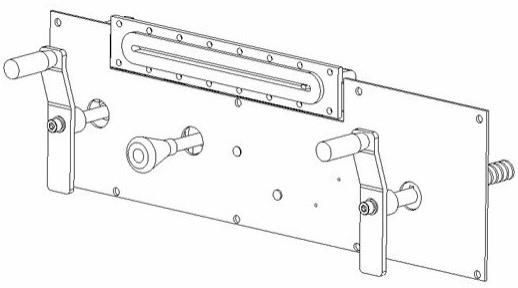

27.图1为本发明sicmosfet子模组的结构示意图;

28.图2为本发明sicmosfet子模组的分解示意图;

29.图3位本发明sicmosfet子单元的结构示意图;

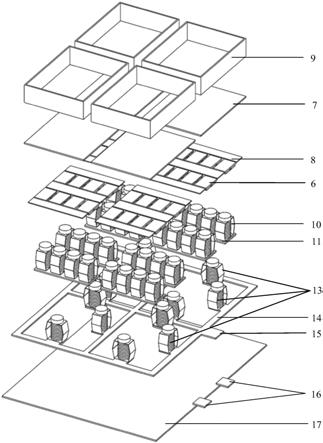

30.图4为本发明sicmosfet子单元的分解示意图;

31.图5为本发明sicmosfet子模组单元压接型封装的结构示意图;

32.图6和7为本发明sicmosfet子模组单元压接型封装的分解示意图。

33.其中,1-源极钼片,2-sicmosfet芯片阵列,3-漏极钼片,4-栅极,5-部分源极,6-sicmosfet子模组阵列,7-漏极端子,8-dbc陶瓷基板,9-外壳,10-源极碟簧及连接部件,11-源极端子,12-sicmosfet子单元阵列,13-栅极碟簧及连接部件,14-pcb基板,15-栅极端子,16-辅助源极端子,17-源极底板,18-sic mosfet子单元,19-sicmosfet子模组。

具体实施方式

34.下面结合附图和实施例对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

35.如图1和图2所示,本发明所设计的sicmosfet子模组,包括源极钼片1、sicmosfet芯片阵列2和漏极钼片3。所述源极钼片1下表面对称设有n个第一凸起,所述第一凸起分别与n个sicmosfet芯片阵列2相连,并露出sicmosfet芯片阵列2的栅极4和部分源极5;所述漏极钼片3上表面设置有n个用于连接和定位sicmosfet芯片阵列2的第二凸起,第二凸起与所述sicmosfet芯片阵列2的漏极相连;所述sicmosfet芯片阵列2由n个sicmosfet芯片组成;所述第一凸起、第二凸起和sicmosfet芯片阵列2的数量均为4个、6个或8个;所述第一凸起与sicmosfet芯片阵列2通过纳米银烧结相连;所述第二凸起与sicmosfet芯片阵列2通过纳米银烧结相连。

36.如图3和图4所示,本发明所设计的sicmosfet子单元18,包括sicmosfet子模组阵列6、漏极端子7、dbc陶瓷基板8、外壳9、源极碟簧及连接部件10和源极端子11。所述漏极端子7上表面和漏极钼片3下表面相连;所述dbc陶瓷基板8下表面和漏极端子7相连;所述外壳9底部边缘与漏极端子7边缘相连;所述源极碟簧及连接部件10的数量和sicmosfet子模组19的数量相等;所述源极碟簧及连接部件10由第一碟簧、第一铜柱和第一铜片组成;所述sicmosfet子模组阵列6由x个sicmosfet子模组19组成,分布成y行;所述漏极端子7和源极

端子11的材质均为钼;所述sic mosfet子模组19的数量为8个,分布成2行;所述sic mosfet子模组阵列6所包含的sicmosfet芯片阵列2的栅极4通过键合线与dbc陶瓷基板8相连;所述dbc陶瓷基板8和所述sic mosfet子模组阵列6间隔排列;所述漏极端子7的上表面和漏极钼片3的下表面通过纳米银烧结相连;述漏极端子7的上表面和dbc陶瓷基板8的下表面通过纳米银烧结相连;所述源极碟簧及连接部件10的第一铜柱与源极钼片1的上表面相接触;所述源极碟簧及连接部件10的第一铜片和源极端子11通过焊接相连,形成一个整体;所述漏极端子7一侧填充硅凝胶,硅凝胶覆盖住sicmosfet子模组阵列6和源极碟簧及连接部件10的第一铜柱。

37.如图5、图6和图7所示,本发明所设计的压接型封装,包括sicmosfet子单元阵列12、栅极碟簧及连接部件13、pcb基板14、栅极端子15、辅助源极端子16和源极底板17。所述sicmosfet子单元阵列12由m个sic mosfet子单元18组成;所述栅极碟簧及连接部件13的数量和dbc陶瓷基板8的数量相等;所述栅极碟簧及连接部件13由第二碟簧、第二铜柱和第二铜片组成;所述pcb基板14下表面与源极底板15相接触;所述源极底板17的材质为钼;所述sicmosfet子单元阵列12的数量为4个;所述栅极碟簧及连接部件13的第二铜片和pcb基板14的上表面覆铜通过焊接相连;所述栅极碟簧及连接部件13的第二铜柱和dbc陶瓷基板8相接触;所述pcb基板14下表面与源极底板17相接触;所述pcb基板14在侧面设置有栅极端子15;所述源极底板17在侧面设置有辅助源极端子16;所述源极底板17上表面与源极端子11相接触。

38.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。