一种多并联ipm故障保护装置、系统以及方法

技术领域

1.本发明涉及ipm(intelligent power module,智能功率模块)故障保护技术领域,尤其涉及一种多并联ipm故障保护装置、系统以及方法。

背景技术:

2.ipm(智能功率模块)是将功率开关器件和驱动电路集成在一起,同时内部还集成有短路保护、欠压保护等故障输出电路以及器件温度输出功能,不仅具有gtr(大功率晶体管)高电流密度、低饱和电压和耐高压的优点,还具有mosfet(场效应晶体管)高输入阻抗、高开关频率和低驱动功率的优点。ipm还具备故障自诊断和保护功能,当发生故障时,可输出故障信号,以保证自身不受损坏。

3.在负载特殊的情况下,ipm通常需要多个并联一起使用,以共同驱动负载。ipm由于内部集成众多元器件,各器件之间会相互关联相互影响,在使用过程中可能会发生各类型的故障,而并联后的ipm抗干扰能力会变得更差,一旦ipm发生故障即可能影响整个系统的稳定可靠性,不利于整个系统的稳定运行,因此非常有必要对并联ipm进行精确、有效的故障保护。

4.针对于ipm的故障保护,目前通常都是针对单一ipm的故障保护方式,即针对每个单一的ipm输出的故障信号进行监测识别但是该类方式当应用于多个ipm并联的情况下时,由于每个ipm都会持续输出信号,输出信号可能是ipm输出的正常信号,也可能是故障反馈信号,而ipm发送的故障反馈信号维持的时间通常较短,维持时间为微秒级(≥20us),而从故障反馈信号发送到传输至处理器检测识别端需要一定时长,并且由于处理器程序运行周期是有一定的时间,所以在检测识别端很容易产生检测不到维持时间较短的故障反馈信号而导致漏检,从而不能达到及时保护ipm的目的。

5.如中国专利申请cn201210298006.2公开一种基于dsp的感应电机变频调速系统,该方案通过利用dsp给ipm发送驱动信号,同时利用dsp接收及处理ipm的出错信号,当ipm出错或出现其他异常时dsp可以关断ipm驱动信号的发送,实现对ipm的保护。上述方案仅是单纯针对单一ipm的故障保护,当应用于多个ipm并联的情况下时,由于各个并联的ipm都会同时持续输出信号,故障反馈信号由于持续时间较短极易于导致漏检的情况,因而上述方案实际并不适用于实现多并联ipm的故障保护识别中。

6.多并联ipm的故障保护还需要做到低成本,系统简单可靠,从而实现工程化低成本可靠应用。如中国专利申请cn201010204616.2公开一种电机控制系统中的ipm驱动和保护方法,该方案通过利用fpga给ipm发送驱动信号,同时利用fpga接收及处理ipm的出错信号,当ipm出错或出现其他异常时fpga可以关断ipm驱动信号的发送,实现对ipm的保护。上述方案中,fpga的运算能力有限,在工程中不能运行复杂的电机控制算法,导致控制系统中还需要额外增加其他控制芯片进行辅助处理,不仅增加了系统的复杂度,而且成本高。

技术实现要素:

7.本发明要解决的技术问题就在于:针对现有技术存在的技术问题,本发明提供一种结构简单、成本低、故障保护效率以及精度高的多并联ipm故障保护装置、系统以及方法,能够同时实现多个并联ipm的故障保护。

8.为解决上述技术问题,本发明提出的技术方案为:

9.一种多并联ipm故障保护装置,包括相互连接的主控模块、故障识别定位模块,所述故障识别定位模块包括相互连接的第一电平转换单元以及锁存单元,所述锁存单元的输入端接入多个并联连接ipm的故障信号进行锁存,锁存信号经过所述第一电平转换单元进行电平转换后,输出给所述主控模块,由所述主控模块进行故障识别定位。

10.进一步的,所述故障识别定位模块还包括与所述锁存单元连接的锁存复位控制单元,所述锁存复位控制单元接入各个ipm的所述故障信号进行逻辑处理,将逻辑处理结果经过延时后输出至所述锁存单元的锁存复位控制端,以控制所述锁存单元进行锁存复位。

11.进一步的,所述锁存复位控制单元包括用于进行逻辑处理的逻辑处理子单元以及用于进行延时的延时子单元,所述逻辑处理子单元的输入端接入各个ipm的所述故障信号,输出端通过所述延时子单元连接至所述锁存单元的锁存复位控制端。

12.进一步的,所述逻辑处理子单元包括多个与门以及一个与非门,各个所述与门分别与所述与非门连接,每个所述与门接入两个ipm的故障信号进行与运算,由所述与非门对各所述与门输出的结果进行与非运算,输出结果提供给所述延时子单元。

13.进一步的,所述延时子单元为基于电容的延时电路、基于rc的延时电路、基于运放的延时电路以及基于晶体管的延时电路中任意一种。

14.进一步的,还包括与所述主控模块连接的故障检测模块,所述故障检测模块包括相互连接的第二电平转换单元以及故障信号逻辑处理单元,所述故障信号逻辑处理单元用于接入各个ipm的所述故障信号进行逻辑处理,逻辑处理结果经过所述第二电平转换单元进行电平转换后输出给所述主控模块的检测端,以实现故障检测。

15.进一步的,当所述主控模块的检测端接收到信号时,判定存在ipm发生故障,控制封锁发送给各ipm的pwm脉冲。

16.进一步的,所述故障检测模块包括多个与门,每个所述与门接入两个ipm的故障信号进行与运算后输出。

17.进一步的,所述主控模块采用dsp。

18.进一步的,所述锁存单元为触发器或者锁存器。

19.进一步的,还包括设置在ipm与所述主控模块之间的隔离保护电路,以用于实现ipm与所述主控模块之间数据交互的隔离保护。

20.进一步的,所述隔离保护电路包括隔离光耦和/或隔离运放,所述主控模块输出的信号和/或所述ipm输出的故障信号,经过所述隔离光耦进行传输,ipm输出的温度信号通过所述隔离运放传输给所述主控模块。

21.进一步的,一种多并联ipm系统,包括多个ipm以用于驱动负载,每两个ipm构成一组ipm,各个所述ipm并联连接,还包括与各所述ipm连接的如上述的故障保护装置。

22.进一步的,每两个所述ipm共用一个驱动隔离电源。

23.一种多并联ipm故障保护方法,其特征在于,步骤包括:

24.s01.接收多个并联连接ipm的故障信号;

25.s02.将所接收到的各个ipm的故障信号由锁存单元进行锁存后输出;

26.s03.将锁存后输出故障信号经过电平转换后,进行故障识别定位。

27.进一步的,所述步骤s03中还包括锁存复位控制步骤,包括:接入各个ipm的所述故障信号进行逻辑处理,将逻辑处理结果经过延时后输出至所述锁存单元的复位控制端,以控制所述锁存单元进行锁存复位。

28.进一步的,所述步骤s02中,通过将每两个ipm的故障信号进行与运算,所有与运算结果再进行与非运算,得到所述逻辑处理结果。

29.进一步的,还包括故障检测步骤,包括:接入各个ipm的所述故障信号进行逻辑处理,将逻辑处理结果进行电平转换后输出至检测端;当所述检测端检测到信号时,判定存在ipm发生故障。

30.进一步的,所述故障检测步骤中,具体将各个ipm的所述故障信号中每两个故障信号进行与运算,得到所述逻辑处理结。

31.与现有技术相比,本发明的优点在于:

32.1、本发明通过由锁存单元接收各个并联连接的ipm的故障信号,锁存后经过电平转化输出给主控模块,由主控模块1进行故障识别,同时将各个并联连接的ipm的故障信号接入至锁存复位控制单元,进行逻辑处理后将逻辑处理结果经过延时后输出给锁存单元的复位控制端,则当有ipm反馈故障信号时,经过逻辑处理后延时一定时间产生有效控制信号给锁存复位控制单元,由于故障信号经过了锁存,因而能够有效确保精准识别到各ipm的故障,同时通过延时的锁存复位控制,还可以实现故障识别定位的持续执行,从而能够有效解决多个ipm故障信号的精确定位识别问题。

33.2、本发明通过由锁存单元、锁存复位控制单元等硬件电路来实现故障识别定位,不仅电路结构简单,可以降低实现复杂程度以及成本,且借助于硬件方式来实现故障识别定位,还可以提高识别定位的可靠性以及效率。

34.3、本发明进一步基于硬件检测方式实现快速故障检测功能,当存在ipm故障时,通过将各个ipm的故障信号进行逻辑处理后,直接经过第二电平转换单元进行电平转换后发送给主控模块的检测端,从而使得只要主控模块的检测端接收到有效信号即可快速的判断存在故障信号。

附图说明

35.图1是本发明实施例1多并联ipm故障保护装置的结构原理示意图。

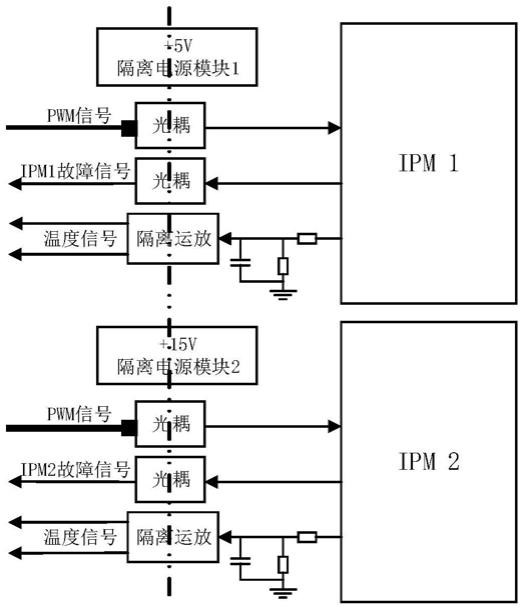

36.图2是本发明实施例1中隔离保护电路设置的原理示意图。

37.图3是本发明实施例1的多并联ipm系统中两组ipm的结构示意图。

38.图4是本发明实施例2中多并联ipm故障保护装置的结构示意图。

39.图例说明:1、主控模块;2、故障识别定位模块;201、第一电平转换单元;202、锁存单元;203、锁存复位控制单元;231、逻辑处理子单元;232、延时子单元;3、故障检测模块;301、第二电平转换单元;;302、故障信号逻辑处理单元。

具体实施方式

40.以下结合说明书附图和具体优选的实施例对本发明作进一步描述,但并不因此而限制本发明的保护范围。

41.实施例1:

42.如图1所示,本实施例多并联ipm故障保护装置包括相互连接的主控模块1、故障识别定位模块2,故障识别定位模块2包括相互连接的第一电平转换单元201以及锁存单元202,锁存单元202的输入端接入多个并联连接ipm的故障信号进行锁存,锁存信号经过第一电平转换单元201进行电平转换后,输出给主控模块1,由主控模块1进行故障识别定位。

43.本实施例通过由锁存单元202接收各个并联连接的ipm的故障信号(如果发生故障,则故障信号对应为有效信号状态,如果未发生故障,则故障信号对应则为无效信号状态),锁存后经过平转化模块2进行电平转换输出给主控模块1,由主控模块1进行故障识别,由于故障信号经过了锁存,因而能够有效确保精准识别到各ipm的故障,避免故障信号持续时间过短而造成漏检,从而能够有效解决多个ipm故障信号的精确定位识别问题。

44.本实施例中,故障识别定位模块2还包括与锁存单元202连接的锁存复位控制单元203,存复位控制单元203接入各个ipm的所述故障信号进行逻辑处理,将逻辑处理结果经过延时后输出至所述锁存单元202的锁存复位控制端,以控制锁存单元202进行锁存复位。上述逻辑处理即为将各个故障信号逻辑运算,得到是否存在故障信号的结果(如果存在ipm故障信号则逻辑处理后对应得到有效信号,否则对应得到无效信号),则当有ipm反馈故障信号时,经过逻辑处理后会产生有效控制信号给锁存复位控制单元203。由于锁存复位控制单元203接收到的逻辑处理结果经过了延时处理,因而故障信号会先由锁存单元202进行锁存、主控模块1进行故障识别,经过一段时间后再控制锁存单元202进行锁存复位,以等待主控模块1识别完成后进行复位,等待下一次的故障。本实施例通过延时的锁存复位控制,可以实现故障识别定位的持续执行,结合上述故障信号锁存,能够有效解决多个ipm故障信号的精确定位识别问题。本实施例中锁存复位控制单元203包括用于进行逻辑处理的逻辑处理子单元231以及用于进行延时的延时子单元232,逻辑处理子单元231的输入端接入各个ipm的故障信号,输出端通过延时子单元232连接至锁存单元202的锁存复位控制端。上述逻辑处理子单元231具体通过逻辑处理,将各个故障信号进行逻辑运算得到是否存在故障信号的结果,即如果存在ipm故障信号则逻辑处理后对应得到有效信号,否则对应得到无效信号。上述有效信号、无效信号是对应于锁存复位控制单元203的锁存复位控制端的有效、无效状态,即当逻辑处理子单元231输出的是有效信号时,表明存在ipm故障信号,则经过延时后发送有效信号给锁存复位控制端,以控制进行锁存复位,否则如果逻辑处理子单元231输出的是无效信号时,表明不存在ipm故障信号,则不需要发送信号给锁存复位控制端。

45.本实施例中,逻辑处理子单元231具体包括多个与门以及一个与非门,各个与门分别和与非门连接,每个与门接入两个ipm的故障信号进行与运算,以将每两个ipm的故障信号进行与运算,由与非门对各与门输出的结果进行与非运算,输出结果提供给延时子单元232。当有ipm发送故障信号时,经过与门处理之后的故障信号至少会有一路信号变为低电平(由高电平对应无故障、低电平对应有故障),经过与非门处理后可以产生一个上升沿,将该信号经过延时子单元232后输出给锁存复位控制单元203,即可实现锁存控制。

46.可以理解的是,如果锁存复位控制单元203的锁存复位控制端是在下降沿时有效,

则可以相应的调整逻辑处理子单元231的结构,如将与非门使用与门代替,以使得当有故障信号时,产生下降沿来驱动锁存单元202复位,具体可以根据实际需求确定。

47.本实施例中,延时子单元232可以采用基于电容的延时电路、基于rc的延时电路、基于运放的延时电路以及基于晶体管的延时电路等,具体可以根据实际需求确定。延时子单元232的延时的时长具体可以依据主控模块1实现故障识别所需要的时间确定,使得当主控模块1完成故障识别后,控制锁存单元202进行锁存复位,具体延时时间设定可以依据实际需求进行设置。

48.本实施例中,锁存单元202具体可采用触发器或者锁存器等实现,触发器可采用如d触发器等,锁存器可采用如sr锁存器等,触发器或者锁存器的信号输出端与各ipm的故障信号输出端连接,触发器或者锁存器的输出端与第一电平转换单元201的输入端连接,触发器或者锁存器的复位控制端与锁存复位控制单元203的输出端连接。锁存单元202当然也可以采用除触发器、锁存器以外的其他的可以实现锁存功能的电路、器件实现。

49.本实施例中,还包括与主控模块1连接的故障检测模块3,故障检测模块5包括相互连接的第二电平转换单元301以及故障信号逻辑处理单元302,故障信号逻辑处理单元302用于接入各个ipm的故障信号进行逻辑处理,逻辑处理结果经过第二电平转换单元301进行电平转换后输出给主控模块1的检测端,以实现故障检测。上述逻辑处理即为将各个故障信号逻辑运算,得到是否存在故障信号的结果,如果存在ipm故障信号则逻辑处理后对应得到有效信号,否则对应得到无效信号,则通过将各个ipm的故障信号进行逻辑处理后,直接经过第二电平转换单元301进行电平转换后发送给主控模块1的检测端,当存在ipm发送故障信号时,经过逻辑处理后即会产生有效信号输出给主控模块1的检测端,则只要主控模块1的检测端接收到有效信号即可判断存在故障信号,可以实现故障的快速故障检测。该故障检测相比于上述故障识别定位要更为快速,因为结合该故障检测以及上述故障识别定位,当存在ipm故障时,首先可以快速检测出故障的发生,以使得能够及时获取到该故障状态,而后通过故障识别定位可以实现精准的故障识别定位,确定出故障发生的位置,实现快速故障检测与故障精准识别定位双重功能。

50.本实施例中,当主控模块1的检测端接收到信号时,判定存在ipm发生故障,控制进行脉冲封锁,使得可以根据故障信号快速封锁脉冲输出,从而达到有效保护ipm及外围电路的作用。

51.本实施例中,故障信号逻辑处理单元302具体包括多个与门,每个与门接入两个ipm的故障信号进行与运算后输出,以将每两个ipm的故障信号进行与运算,则当有ipm发送故障信号时,经过与门处理之后的故障信号至少会有一路信号变为低电平(由高电平对应无故障、低电平对应有故障),经过第二电平转换单元301输出给主控模块1。

52.本实施例第一电平转换单元201、第二电平转换单元301均是用于将接收到的电平信号进行转换,以使得匹配于主控模块1的检测,在经过逻辑处理后的信号,如果其中存在故障信号,则经过第一电平转换单元201、第二电平转换单元301转换后会产生有效电平,提供给主控模块1的信号输入端或检测端,以使得在主控模块1的信号输入端接收到有效电平后可进行故障识别定位,在检测端检测到有效电平后,可判定出存在ipm故障信号。上述第一电平转换单元201、第二电平转换单元301可以采用分立的两个转换电路实现,当然也可以采用集成的一个转换电路实现。

53.本实施例中,还包括设置在ipm与主控模块1之间的隔离保护电路,以用于实现ipm与主控模块1之间数据交互的隔离保护,进一步提高ipm与主控模块1之间的数据交互可靠性。

54.如图2所示,本实施例中隔离保护电路包括隔离光耦以及隔离运放,主控模块1输出的信号、ipm输出的故障信号,经过隔离光耦进行传输,ipm输出的温度信号通过隔离运放传输给主控模块1。本实施例具体分别设置第一光耦,以将主控模块1输出的信号(pwm脉冲信号)经过第一光耦后传输给ipm,以及设置第二光耦,以将ipm输出的故障信号经过第二光耦传输给主控模块1。上述隔离光耦具体可以采用具有高共模抑制比的高速光耦,也可以根据实际需求采用其他类型的光耦。通过采用上述全隔离的方式,利用隔离光耦以及隔离运放将ipm与dsp控制信号侧完全隔离进行控制,可以大大增强了电路的抗干扰性。

55.如图3所示,本实施例还包括多并联ipm系统,该多并联ipm系统包括多个ipm以用于驱动负载,每两个ipm构成一组ipm,各个ipm并联连接,还包括与各ipm连接的如上述的故障保护装置,可以当ipm发生故障时,精准识别出故障以及故障发生位置,确保各并联ipm的稳定可靠性。在设计电路的pcb时,可以减量减小电流回流路径,即图1中的线路(1)的路径长度,以达到提高电路抗干扰性的要求。

56.本实施例中,每两个ipm共用一个驱动隔离电源(如图3中 15v隔离电源模块),即采用2个ipm共用一个驱动电源的方式,可以对pcb进行精细化设计,减小电流回流路径,从而可以增强电路的抗干扰性,同时减少隔离电源的使用数量,降低设备的成本。当然也可以根据实际需求,采用其他的驱动电源提供方式,如ipm由一个驱动电源单独给一个ipm供电的方式进行供电,然后对多个的ipm进行并联处理。

57.本实施例多并联ipm故障保护方法的步骤包括:

58.s01.接收多个并联连接ipm的故障信号;

59.s02.将所接收到的各个ipm的故障信号由锁存单元202进行锁存后输出;

60.s03.将锁存后输出故障信号经过电平转换后,进行故障识别定位。

61.本实施例中,步骤s03中还包括锁存复位控制步骤,包括:接入各个ipm的所述故障信号进行逻辑处理,将逻辑处理结果经过延时后输出至锁存单元202的复位控制端,以控制锁存单元202进行锁存复位。

62.本实施例步骤s02中,通过将每两个ipm的故障信号进行与运算,所有与运算结果再进行与非运算,得到逻辑处理结果。

63.本实施例中还包括故障检测步骤,包括:接入各个ipm的故障信号进行逻辑处理,将逻辑处理结果进行电平转换后输出至检测端;当检测端检测到信号时,判定存在ipm发生故障。

64.本实施例故障检测步骤中,具体将各个ipm的故障信号中每两个故障信号进行与运算,得到逻辑处理结果。

65.本实施例多并联ipm故障保护方法与上述多并联ipm故障保护装置的原理一致,在此不再一一赘述。

66.实施例2:

67.本实施例多并联ipm系统具体包括6个ipm,每2个ipm为一组ipm,6个ipm并联用以驱动负载。6个ipm采用同一个直流高压电源,并联驱动磁悬浮电机的不同线圈,以减小电流

回流路径的长度,提高电路的抗干扰性能,同时兼顾设计成本,在ipm驱动电源侧采用2个ipm共用一个驱动隔离电源,即每2个ipm采用同一个ipm驱动电源,且控制侧电源与驱动电源隔离分开。

68.本实施例多并联ipm故障保护装置包括相互连接的主控模块1、故障识别定位模块2,故障识别定位模块2包括依次连接的第一电平转换单元201、锁存单元202以及锁存复位控制单元203,锁存单元202的输入端接入多个并联连接ipm的故障信号进行锁存,锁存信号经过第一电平转换单元201进行电平转换后,输出给主控模块1,由主控模块1进行故障识别定位,锁存复位控制单元203接入各个ipm的所述故障信号进行逻辑处理,将逻辑处理结果经过延时后输出至锁存单元202的锁存复位控制端,以控制锁存单元202进行锁存复位。且具体主控模块1采用dsp实现,由dsp对ipm进行开关控制,锁存单元202采用d触发器实现,通过充分利用dsp的强大计算性能,结合触发器等可以有效实现多并联ipm的高效驱动与故障保护。

69.本实施例中,锁存复位控制单元203包括用于进行逻辑处理的逻辑处理子单元231以及用于进行延时的延时子单元232,逻辑处理子单元231的输入端接入各个ipm的所述故障信号,输出端通过所述延时子单元232连接至锁存单元202的锁存复位控制端。逻辑处理子单元231具体包括3个与门以及一个与非门,各个与门分别与与非门连接,每个与门接入两个ipm的故障信号进行与运算,由与非门对各所述与门输出的结果进行与非运算,输出结果提供给延时子单元232。延时子单元232具体采用电容器。

70.本实施例中,还包括设置在ipm与主控模块1之间的隔离保护电路,以用于实现ipm与主控模块1之间数据交互的隔离保护,进一步提高ipm与主控模块1之间的数据交互可靠性。隔离保护电路包括隔离光耦以及隔离运放,具体参见图2所示,主控模块1输出的信号、ipm输出的故障信号,经过隔离光耦进行传输,ipm输出的温度信号通过隔离运放传输给主控模块1。为了增强电路的抗干扰能力,本实施例中pwm信号由dsp产生,并经过光耦隔离送给ipm,ipm的故障反馈信号也由光耦隔离之后送回dsp,上述光耦选用高共模抑制比的高速光耦,以提高电路抗干扰性能。ipm的温度反馈信号采用隔离运放隔离之后送给dsp的片内ad模块。上述隔离运放是一个单边电压输入,差分电压输出的隔离运放,具有可隔离3kv电压的性能。每2个ipm采用同一个隔离电源为隔离器件(光耦、隔离运放)供电,如下图 5v隔离电源模块1。在故障反馈和温度反馈的路径上,靠近器件管脚放置电容,以用于滤波。

71.本实施例中,还包括与dsp连接的故障检测模块3,故障检测模块5包括相互连接的第二电平转换单元301以及故障信号逻辑处理单元302,故障信号逻辑处理单元302用于接入各个ipm的故障信号进行逻辑处理,逻辑处理结果经过第二电平转换单元301进行电平转换后输出给dsp的检测端(tz检测管),以实现故障检测,即故障反馈检测也由dsp进行完成处理,利用dsp上的tz管脚能够快速检测故障,实现dsp脉冲封锁,从而保护ipm模块。本实施例第二电平转换单元301具体与第一电平转换单元201采用集成的一块电平转换芯片实现。

72.由于有6个ipm故障反馈信号,如图4所示,本实施例将6个ipm的故障反馈信号分两部分进行检测处理,包括:

73.一部分是故障信号的快速检测处理,用于检测到ipm故障信号之后,快速封锁dsp的pwm输出脉冲。此部分利用2输入的与门将6路ipm的故障反馈信号两两做与处理,将与处理之后的3个信号通过电平转换器直接送到dsp的tz检测管脚上。dsp的tz管脚是硬件检测

管脚,当检测到信号时,硬件直接封锁pwm脉冲输出,减少了程序封锁脉冲的运行时间。由于此部分故降快速检测电路,不能精确的判断出哪个ipm报的故障信号,由另一部分ipm故障反馈检测电路来完成此项功能。

74.另一部分是故障信号的识别定位检测处理。由于ipm的故障反馈信号维持的时间较短,为了能够识别定位故障ipm,将ipm故障信号送入d触发器,d触发器出来的信号经过电平转换器送给dsp的gpio口,进行程序判断识别;经过与门处理的三路故障反馈信号与dsp的复位信号一起经过与非门,再经过电容延时处理之后,送给d触发器的控制引脚。当有故障来临时,经过与门处理之后的三路故障信号至少会有一路信号变为低电平,经过与非门处理,再经过电容延时,此时就会出现一个上升沿给d触发器的控制引脚,此时d触发器的输入口信号比d触发器的控制引脚信号来的要早,从而将d触发器输入端的信号进行锁存输出给dsp,直到dsp精确识别定位ipm故障之后,dsp再输出复位信号,将d触发器进行锁存复位,等待下一次的故障来临。

75.通过本实施例上述装置,既可以根据故障信号快速封锁脉冲输出达到保护ipm及外围电路的作用,还可以实现多个ipm故障信号的精确定位识别,以解决多个ipm故障信号的精确定位识别问题。

76.上述只是本发明的较佳实施例,并非对本发明作任何形式上的限制。虽然本发明已以较佳实施例揭露如上,然而并非用以限定本发明。因此,凡是未脱离本发明技术方案的内容,依据本发明技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均应落在本发明技术方案保护的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。