1.本发明涉及增量型模数转换器的输入缩放模块,属于模拟感知信号的芯片设计技术领域。

背景技术:

2.随着物联网、电源管理和自动驾驶等新技术的日益发展进步,对各种信号的感知与测量要求也越来越高。随着被测量信号幅度范围的增大,需要模数转换器(adc:analog-to-digital converter)能够处理从几毫伏到比如几十伏的输入电压。增量型模数转换器(iadc:incremental(delta-sigma)adc)常用在高精度、低速模数转换应用场合。

3.现有技术中,如图11和图12所示,图11为一个典型的二阶增量型模数转换器的结构图。图12所示为输入采样与积分器的差分电路。为了能够采样较高的输入电压,通常采用如图13所示的减少采样电容或者如图14所示的对输入用电阻串分压。

4.首先,无论是采用电阻串对输入进行分压,还是减小输入的采样电容值,都面临改变分压比例或采样电容比例时,adc增益因为电阻或电容失配(mismatch)而需要重新校正的问题。其次,降低电阻分压比例或减小采样电容值时,都面对adc信噪比与功耗之间的权衡。即要么信噪比降低,要么芯片的功耗甚至面积增加。

技术实现要素:

5.本发明的目的是解决上述现有技术的不足,针对传统改变分压比例或采样电容比例存在电阻或电容失配及出现信噪比与功耗权衡的问题,提出增量型模数转换器的输入缩放模块。

6.为了达到上述目的,本发明所采用的技术方案为:

7.增量型模数转换器的输入缩放模块,设置在二阶增量型模数转换器中,所述二阶增量型模数转换器具备输入采样与积分器的差分电路,

8.所述输入采样与积分器的差分电路包括差分输入电压v

inp

和v

inn

、参考电压v

ref

和v

gnd

、对应差分输入电压的c

in

和对应参考电压的c

ref

、采样相位φ1和积分相位φ2,其特征在于:

9.所述差分输入电压v

inp

和v

inn

的输出端分别设有数字缩放模块,所述数字缩放模块具备分数m/n过采样,所述m和所述n均为整数,所述m<n,所述n为二阶增量型模数转换器总积分周期数p的约数。

10.优选地,所述数字缩放模块包括输入分数采样时钟φ

1s

和积分时钟φ

2s

,所述输入分数采样时钟φ

1s

及积分时钟φ

2s

相对于采样相位φ1和积分相位φ2的占空比为分数m/n。

11.优选地,所述输入采样与积分器的差分电路包括若干组差分输入电压,任意组所述差分输入电压的v

inp

和v

inn

分别具备所述数字缩放模块。

12.优选地,所述二阶增量型模数转换器的增益为:

[0013][0014]

其中v

in_diff

为当前差分输入电压。

[0015]

优选地,所述c

ref

=4c

in

,av=2,v

ref

=v

sup

/2,v

in_diff_fs

=v

sup

,v

in_diff_fs

为差分输入满量程,v

sup

为电源电压。

[0016]

本发明的有益效果主要体现在:

[0017]

1.通过输入缩放模块实现分数过采样从而缩放输入范围,避免电容缩小带来的热噪声kt/c增加而降低adc的精度。

[0018]

2.采用固定的采样电容值,避免了电容缩放或电阻分压时因失配而需要重新校正adc的增益。

[0019]

3.采样时钟的数字控制既节省了芯片面积,也具有更大的灵活性与可编程性。

[0020]

4.分数过采样可以用来加权多个输入,同时共享采样电容,从而各自权重均不受电容失配的影响。

附图说明

[0021]

通过阅读参照以下附图所作的对非限制性实施例所作的详细描述,本技术的其它特征、目的和优点将会变得更明显:

[0022]

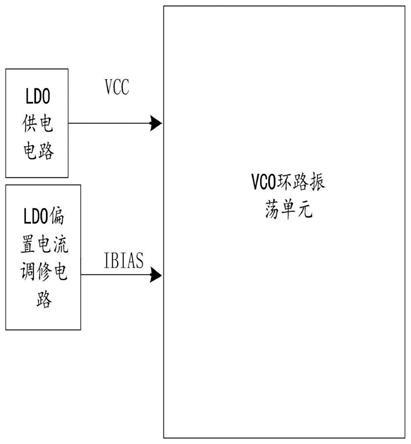

图1是本发明输入缩放模块设置在输入采样差分电路中的结构示意图。

[0023]

图2是本发明输入电压1/4分数过采样控制时钟图。

[0024]

图3是本发明输入电压1/4分数过采样仿真结果图。

[0025]

图4是本发明输入电压1/2分数过采样仿真结果图。

[0026]

图5是本发明输入缩放模块应用于iadc输入加权电路中的结构示意图。

[0027]

图6是本发明输入加权的分数过采样控制时钟图。

[0028]

图7是本发明分数过采样与传统输入过采样的对比图。

[0029]

图8是本发明分数过采样与传统输入过采样的另一对比图。

[0030]

图9是传统输入过采样仿真结果图。

[0031]

图10是传统输入过采样的另一仿真结果图。

[0032]

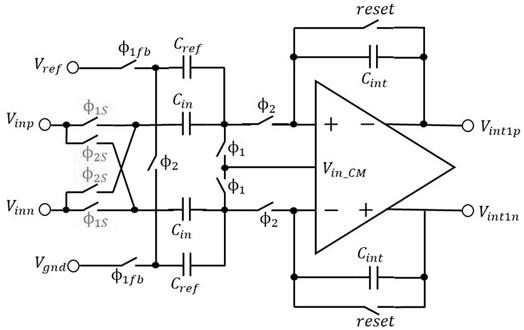

图11是现有技术中二阶增量型模数转换器的结构示意图。

[0033]

图12是现有技术中输入采样差分电路的电路图。

[0034]

图13是现有技术中减少采样电容的示意图。

[0035]

图14是现有技术中分压电阻串的示意图。

具体实施方式

[0036]

为使本发明实施例的目的、技术方案和优点更加清楚,下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

[0037]

下面结合附图和实施例对本技术作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释相关发明,而非对该发明的限定。另外还需要说明的是,为了

便于描述,附图中仅示出了与有关发明相关的部分。需要说明的是,在不冲突的情况下,本技术中的实施例及实施例中的特征可以相互组合。

[0038]

通过本发明输入缩放模块能实现分数(m/n)过采样,等效地将adc输入电压缩小n/m倍。相当于在数字领域里对adc的输入电压进行缩放(scaling)。相比于传统的依赖于电阻或电容比例的电阻分压或减小采样电容值,本发明对adc输入电压的缩放比(scaling ratio)不受电阻或电容等器件的失配影响。能实现开关电容时钟的数字控制,而没有传统方法里的电阻或电容的失配问题。同时,数字控制具有更大的灵活性与可编程性。

[0039]

本发明提供增量型模数转换器的输入缩放模块,如图1和2所示,设置在二阶增量型模数转换器中,二阶增量型模数转换器具备输入采样与积分器的差分电路。该差分电路如图12所示,包括差分输入电压v

inp

和v

inn

、参考电压v

ref

和v

gnd

、对应差分输入电压的c

in

和对应参考电压的c

ref

、采样相位φ1和积分相位φ2,其属于现有技术。

[0040]

当其输入电压的最大值为电池电压v

sup

多倍时,其为了能够采样较高的输入电压,通常采用如图3和图4所示的减少采用电容或使用电阻串分压的方式,前者引起iadc输入热噪声的能量kt/c增加多倍,后者更是将iadc的量化误差相对于未分压的输入来说增加多倍。传统方法的另一个缺点是如果adc的满量程是可配置的(re-configurable),改变满量程设置后,由于电阻或电容的失配,iadc的增益需要重新校正。

[0041]

针对此情况,如图1和图2所示,差分输入电压v

inp

和v

inn

的输出端分别设有数字缩放模块,数字缩放模块具备分数m/n过采样,m和n均为整数,n为二阶增量型模数转换器总积分周期数p的约数,m<n,而n<<p。

[0042]

具体地,如图1和图2所示,该数字缩放模块应用于输入满量程可配置的输入采样差分电路中。即通过数字缩放模块改变输入采样时钟相对于过采用时钟的占空比(on/off dutycycle)分数,从而满足缩放调节需求。

[0043]

在一个具体实施例中,如图1和图2所示,数字缩放模块包括输入分数采样时钟φ

1s

和积分时钟φ

2s

,输入分数采样时钟φ

1s

及积分时钟φ

2s

相对于采样相位φ1和积分相位φ2的占空比为分数m/n。

[0044]

如图1所示,输入缩放模块设置在输入采样差分电路中的结构示意图,图2是本发明adc输入电压1/4分数采用控制时钟的图示。本发明的方法既简单又灵活,仅仅是在数字电路中改变输入采样时钟相对于过采样时钟的“占空比”(on/off duty cycle)分数。

[0045]

如图3、图4、图7至图10所示,其为传统输入电压调节与本发明iadc仿真结果的比较,这里电源电压v

sup

=3.3v,参考电压v

ref

=1.65v。

[0046]

图9和图10中,传统iadc的仿真结果包括输入差分电压分别为0.2v和3.0v。图中的波形包含了第一级积分器的差分输出(outp1和outn1),第二级积分器的差分输出(outp2和outn2),以及1-位(1-bit)量化器的输出(do_3d)。

[0047]

图3和图4是本发明的输入分数过采样iadc的仿真结果,包括输入差分电压为0.8v而分数为1/4,以及输入差分电压为6.0v而分数为1/2。图中的波形同样包含了第一级积分器的差分输出(outp1和outn1),第二级积分器的差分输出(outp2和outn2),以及1-位量化器的输出(do_3d)。

[0048]

比较本发明仿真结果与传统仿真结果,可见第一级积分器的输出电压范围只是稍微增加约10%,而第二级积分器的输出电压范围几乎相同。

[0049]

图7和图8比较了传统和本发明的iadc经三级128阶低通数字滤波器后的输出。仿真中的数字滤波器是使用verilog-a模型实现的,所以输出信号sinc3是如下的模拟电压仿真中传统结构iadc的输入满量程v

in_diff_fs

=3.3v,所以当差分输入电压v

in_diff

=0.2或3.0v时,理想的滤波器输出电压sinc3=0.060606或0.90909。

[0050]

图7和图8中仿真结果显示,过采样频率为1mhz时,iadc仿真中积分开始时间为45μs,到大约520μs时,iadc只考虑量化噪声的输出已经稳定在14或15位精度。

[0051]

一般情况下,二阶增量型模数转换器的增益为:其中v

in_diff

为当前差分输入电压。c

ref

=4c

in

,av=2,v

ref

=v

sup

/2,v

in_diff_fs

=v

sup

,v

in_diff_fs

为差分输入满量程,v

sup

为电源电压。

[0052]

在一个具体实施例中,如图5和图6所示,输入采样差分电路包括若干组差分输入电压,任意组差分输入电压的v

inp

和v

inn

分别具备数字缩放模块。

[0053]

即加权iadc的多个输入共享采样电容,既避免了采样电容过小而使输入热噪声kt/c增加,又使权重精确而不受采样电容失配的影响。如图5和图6所示,iadc的等效输入为:

[0054]

如图5所示,是对应的开关电容实现的输入采样和积分电路图。值得注意的是,多个输入可以是加权后相加,也可以是相减。同样地,参考电压可以是单极性的,也可以是双极性的。

[0055]

通过以上描述可以发现,本发明增量型模数转换器的输入缩放模块,通过输入缩放模块实现分数过采样从而缩放输入范围,避免电容缩小带来的热噪声kt/c增加而降低adc的精度。采用固定的采样电容值,避免了电容缩放或电阻分压时因失配而需要重新校正adc的增益。采样时钟的数字控制既节省了芯片面积,也具有更大的灵活性与可编程性。分数过采样可以用来加权多个输入,同时共享采样电容,从而各自权重均不受电容失配的影响。

[0056]

术语“包括”或者任何其它类似用语旨在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备/装置不仅包括那些要素,而且还包括没有明确列出的其它要素,或者还包括这些过程、方法、物品或者设备/装置所固有的要素。

[0057]

至此,已经结合附图所示的优选实施方式描述了本发明的技术方案,但是,本领域技术人员容易理解的是,本发明的保护范围显然不局限于这些具体实施方式。在不偏离本发明的原理的前提下,本领域技术人员可以对相关技术特征作出等同的更改或替换,这些更改或替换之后的技术方案都将落入本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。