1.本发明涉及半导体集成电路领域,特别是一种半导体器件的制造方法。

背景技术:

2.随着半导体器件集成度的不断提高,特征尺寸逐渐减小,来自制造和设计方面的挑战促使了三维设计晶体管的发展。例如如鳍片场效应晶体管(finfet)、以及纳米片晶体管(nanosheet)。

3.相对于现有的平面晶体管,finfet是用于20nm及以下工艺节点的先进半导体器件,包括一个垂直于体硅衬底的fin,fin被称为鳍、鳍片或鳍状半导体柱,在该fin内限定有源极区、漏极区和沟道区,不同的fintet被sti结构分割开来,栅极绝缘层和栅极层形成的栅极堆叠在侧面和顶面包围fin,从而使得finfet具有极佳的特性。

4.然而随着半导体器件的元件密度和集成度的提高,对finfet器件的性能提出了更高的要求,其中提高finfet器件的性能的关键目标之一是提高器件沟道内的迁移率并对流过器件沟道的漏电流进行控制,目前主要通过离子注入轻掺杂漏极(light doped drain,ldd)掺杂区的方法,来提高载流子迁移率,避免或抑制导电沟道长度缩短引起源极和漏极之间的漏电流,进而提高晶体管的性能。

5.但是,采用离子注入轻掺杂漏极掺杂区,会使得掺杂区的掺杂层分布不均匀,从而导致载流子迁移率降低,并未很好的达到避免或抑制导电沟道长度缩短引起源极和漏极之间的漏电流的效果。

技术实现要素:

6.本申请所要解决的技术问题是,提供一种半导体器件的制造方法,使得掺杂区的掺杂层分布均匀,从而提高载流子迁移率,避免或抑制导电沟道长度缩短引起源极和漏极之间的漏电流,进而提高晶体管的性能。

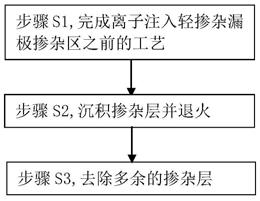

7.为了解决上述技术问题,本发明公开了一种半导体器件的制造方法,包括以下步骤:

8.步骤s1,完成离子注入轻掺杂漏极掺杂区之前的工艺,所形成的器件包括:

9.形成于半导体表面上的伪栅极结构;所述半导体器件具有第一方向和第二方向,在所述半导体器件的第二方向的两侧形成有源极区和漏极区;

10.步骤s2,沉积掺杂层并退火;

11.步骤s3,去除多余的掺杂层。

12.优选地,所述掺杂层的材料为psg。

13.优选地,所述掺杂层的材料为bsg。

14.优选地,所述掺杂层由化学汽相沉积法沉积而成。

15.优选地,所述半导体器件为鳍式晶体管。

16.优选地,所述栅极结构覆盖在部分长度的所述鳍体的顶部表面和侧面;所述源极

区和漏极区形成在所述栅极结构两侧的所述鳍体中。

17.优选地,所述各个鳍体之间形成有隔离区域。

18.优选地,所述隔离区域为sti。

19.优选地,所述半导体器件为纳米片晶体管。

附图说明

20.图1是本发明的半导体器件的制造方法流程图。

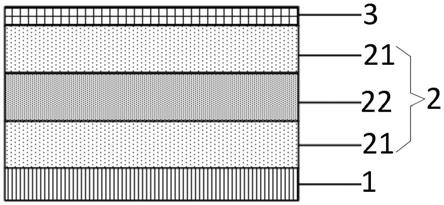

21.图2是本发明的半导体器件的制造方法器件实施例一的第一方向剖面示意图。

22.图3是本发明的半导体器件的制造方法器件实施例一的第二方向剖面示意图。

23.附图标记说明

24.10

ꢀꢀꢀꢀ

半导体衬底

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

20

ꢀꢀꢀꢀꢀꢀ

伪栅极结构

25.30

ꢀꢀꢀꢀ

源极区

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

40

ꢀꢀꢀꢀꢀꢀ

漏极区

26.50

ꢀꢀꢀꢀ

鳍部

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

60

ꢀꢀꢀꢀꢀꢀ

掺杂层

具体实施方式

27.下文公开了本发明的具体实施例;但是,应该理解的是,公开的实施例仅为本发明的示例,它们可以采用各种形式实施。因此,在此所公开的具体结构和功能细节不应解释为具有限制性。进一步地,本文中使用的名词和术语不是限制性的;而是提供对本发明的可理解描述。通过结合附图来考虑以下描述将能更好地理解本发明,其中相同参考数字代表相同的含义。这些附图不是按比例绘制。

28.实施例1

29.本发明的一种较佳实施例半导体器件的制造方法,包括以下步骤:

30.步骤s1,完成离子注入轻掺杂漏极掺杂区之前的工艺。

31.具体地,该工艺步骤可以如下:

32.首先提供一半导体衬底10。所述半导体器件具有第一方向和第二方向。衬底10可以是晶圆,如硅晶圆。在一些实施例中,衬底10的半导体材料可包括硅;锗;包括碳化硅、砷化镓、磷化镓、磷化铟、砷化铟和/或锑化铟的化合物半导体;或其组合。

33.然后,可以通过光刻工艺形成sti,之后去除光刻胶,然后刻蚀沟槽,并生长衬垫氧化层;之后可以采用自对准间隔光刻双重图案方法sadp形成鳍部50。

34.之后,由于半导体器件形成有p区和n区,在p区形成p阱,在n区形成n阱。从半导体器件的第一方向上看,所述sti结构形成在p阱和n阱之间。

35.然后,在上述的器件上形成伪栅极结构20。从半导体器件的第一方向上看,所述sti结构形成在两个伪栅极结构20之间,从半导体器件的第二方向上看,伪栅极结构20的两侧形成有源极区30和漏极区40。

36.步骤s2,沉积掺杂层60并退火。

37.优选地,所述掺杂层60为固相薄膜层,材料为如磷-硅酸盐玻璃(psg)或硼-硅酸盐玻璃(bsg),并且可通过诸如cvd或pecvd的任何适当方法沉积。

38.优选地,可以在p区沉积硼-硅酸盐玻璃(bsg),在n区沉积磷-硅酸盐玻璃(psg)。

39.这样,在退火后,从半导体器件的第二方向上看,伪栅极结构20的源极区30和漏极

区40的鳍部上会形成均匀的掺杂层60,从而可以提高载流子迁移率,避免或抑制导电沟道长度缩短引起源极和漏极之间的漏电流,进而提高晶体管的性能。

40.步骤s3,去除多余的掺杂层。

41.随后地,可执行诸如cmp的平坦化工艺去除多余的掺杂层。

42.实施例二

43.实施例二与实施例一的区别在于,实施例二的半导体器件为纳米片晶体管,所述掺杂层形成在纳米片晶体管的源极区与漏极区。

44.以上通过具体实施方式和实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

技术特征:

1.一种半导体器件的制造方法,其特征在于,包括以下步骤:步骤s1,完成离子注入轻掺杂漏极掺杂区之前的工艺,所形成的器件包括:形成于半导体表面上的伪栅极结构;所述半导体器件具有第一方向和第二方向,在所述半导体器件的第二方向的两侧形成有源极区和漏极区;步骤s2,沉积掺杂层并退火;步骤s3,去除多余的掺杂层。2.如权利要求1所述的半导体器件的制造方法,其特征在于,所述掺杂层的材料为psg。3.如权利要求1所述的半导体器件的制造方法,其特征在于,所述掺杂层的材料为bsg。4.如权利要求1所述的半导体器件的制造方法,其特征在于,所述掺杂层由化学汽相沉积法沉积而成。5.如权利要求1所述的半导体器件的制造方法,其特征在于,所述半导体器件为鳍式晶体管。6.如权利要求4所述的半导体器件的制造方法,其特征在于,所述栅极结构覆盖在部分长度的所述鳍体的顶部表面和侧面;所述源极区和漏极区形成在所述栅极结构两侧的所述鳍体中。7.如权利要求4所述的半导体器件的制造方法,其特征在于,所述各个鳍体之间形成有隔离区域。8.如权利要求7所述的半导体器件的制造方法,其特征在于,所述隔离区域为sti。9.如权利要求1所述的半导体器件的制造方法,其特征在于,所述半导体器件为纳米片晶体管。

技术总结

本发明公开了一种半导体器件的制造方法,包括以下步骤:步骤S1,完成离子注入轻掺杂漏极掺杂区之前的工艺,所形成的器件包括:形成于半导体表面上的伪栅极结构;所述半导体器件具有第一方向和第二方向,在所述半导体器件的第二方向的两侧形成有源极区和漏极区;步骤S2,沉积掺杂层并退火;步骤S3,去除多余的掺杂层。本发明使得掺杂区的掺杂层分布均匀,从而提高载流子迁移率,避免或抑制导电沟道长度缩短引起源极和漏极之间的漏电流,进而提高晶体管的性能。管的性能。管的性能。

技术研发人员:翁文寅

受保护的技术使用者:上海华力集成电路制造有限公司

技术研发日:2021.11.23

技术公布日:2022/2/28

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。