1.本发明涉及晶原级半导体器件微波特性测量技术领域,尤其涉及一种校准件制备的方法及校准件。

背景技术:

2.微电子行业中配备的大量“在片s参数测试系统”在使用前,需要使用在片校准件结合相应的校准方法进行矢量误差修正。用于表征晶体管性能的矢量网络分析仪校准一般使用商用的阻抗标准(iss),具体包含制作在陶瓷衬底上的开路-短路-负载-直通(solt)校准件,传输线-反射-匹配(lrm)校准件,传输线-反射-反射-匹配(lrrm)校准件等。iss的特点是成本低廉,使用方便而且耐用。

3.传输线结构为共面波导cpw。国内在校准件设计方面,一般采用电磁仿真方法,但电磁仿真模型精度有限、校准件结构单一、工艺差等方面,导致设计的直通校准件的阻抗偏离50ω,负载校准件阻值不一致等问题。

技术实现要素:

4.本发明实施例提供了一种校准件制备的方法及校准件,以解决现有技术中采用电磁仿真模型制备校准件时出现的校准件出现偏差的问题。

5.第一方面,本发明实施例提供了一种校准件制备的方法,包括:

6.确定传输线横截面尺寸;

7.当所述横截面尺寸满足预设校准件频率要求时,对所述横截面尺寸进行优化,得到最优横截面尺寸;

8.基于所述最优横截面尺寸设置多组传输线,确定所述多组传输线中特征阻抗与预设阻抗值最接近的目标传输线,并基于所述目标传输线确定对应的校准件尺寸;

9.根据所述校准件尺寸进行半导体工艺加工,并对加工完成的校准件中的负载校准件的电阻进行激光修阻,对修阻后所有校准件进行定值。

10.在一种可能的实现方式中,所述确定传输线横截面尺寸,包括:

11.获取衬底厚度、衬底介电常数、设置在所述衬底上的金属的电导率和金属厚度;

12.根据所述衬底厚度、所述衬底介电常数、所述电导率和所述金属厚度,得到传输线横截面尺寸。

13.在一种可能的实现方式中,所述对所述横截面尺寸进行优化,得到最优横截面尺寸,包括:

14.将所述横截面尺寸在第一预设步进范围内变化,得到多组横截面尺寸;

15.对所述多组横截面尺寸、预设长度的传输线进行仿真,将所有传输线中s

11

最小值对应的横截面尺寸确定为最优横截面尺寸。

16.在一种可能的实现方式中,判断所述横截面尺寸满足预设校准件频率要求的方法包括:

17.根据所述横截面尺寸计算校准件频率;

18.当所述校准件频率大于或等于所述预设校准件频率时,确定所述横截面尺寸满足预设校准件频率要求。

19.在一种可能的实现方式中,所述根据所述横截面尺寸计算校准件频率,包括:

20.根据计算校准件频率;

21.其中,f表示校准件频率,g表示中心导体与对应地板的间距,w表示中心导体的宽度,μ0表示空气磁导率,ε0表示空气的介电常数,εr表示衬底介电常数,h表示衬底厚度。

22.在一种可能的实现方式中,所述基于所述最优横截面尺寸设置多组传输线,确定所述多组传输线中特征阻抗与预设阻抗值最接近的目标传输线,包括:

23.将所述最优横截面尺寸在第二预设步进范围内变化,得到多组最优横截面尺寸,并基于所述多组最优横截面尺寸和每组最优横截面尺寸对应的至少三个长度进行不同的传输线版图加工;

24.采用预设电阻对传输线特征阻抗进行标定;

25.基于传输线版图和预设电阻,测量每根传输线的特征阻抗,确定与所述预设电阻的阻抗值最接近的特征阻抗对应的传输线为目标传输线。

26.在一种可能的实现方式中,所述根据所述校准件尺寸进行半导体工艺加工,包括:

27.根据确定的校准件尺寸制备带线和电阻对应的掩模版;

28.对陶瓷衬底进行清洗和干燥,所述陶瓷衬底的任一面抛光;

29.在所述陶瓷衬底的抛光面上溅射电阻层;

30.在所述电阻层上溅射合金层;

31.在所述合金层的表面上,将所述掩模版图形中的带线电镀金属;

32.在制备了金属带线的校准件表面涂覆光刻胶,依次将所述掩模版图形外的合金和电阻腐蚀掉,得到校准件。

33.在一种可能的实现方式中,所述对陶瓷衬底进行清洗和干燥,包括:

34.在第一清洗液中,将所述陶瓷衬底于预设温度范围内煮第一预设时间后取出,用水冲洗至陶瓷衬底的ph为中性;

35.将经过第一步处理的陶瓷衬底在氢氟酸中浸泡第二预设时间,用水冲洗至陶瓷衬底的ph为中性;

36.在第二清洗液中,将经过第二步处理的陶瓷衬底于所述预设温度下煮所述第一预设时间后取出,用水冲洗至陶瓷衬底的ph为中性;

37.将陶瓷衬底使用经过干燥过滤的氮气吹干;

38.所述第一清洗液为水、氨水和过氧化氢混合而成,其体积比依次为4:1:1;

39.所述第二清洗液为水、盐酸和过氧化氢混合而成,其体积比依次为4:1:1;

40.所述预设温度范围为80℃至90℃构成的范围;

41.所述第一预设时间为10min至15min中的任一时间;

42.所述第二预设时间为2min。

43.在一种可能的实现方式中,所述电阻层采用材料为nic或tan;所述电阻层的厚度为40nm至100nm中的任一值;

44.所述合金层采用材料为ti/w;所述合金层的厚度为50nm至1μm中的任一值;

45.所述带线采用材料为纯度大于90%的金,所述带线电镀的厚度为1μm至10μm中的任一值。

46.第二方面,本发明实施例提供了一种校准件,包括:采用上述任一实施例所述的校准件制备的方法制备得到。

47.本发明实施例提供一种校准件制备的方法及校准件,通过首先设计校准件的尺寸,然后根据校准件的尺寸进行校准件的工艺制备,从而得到校准件。在进行校准件的尺寸设计时,本技术中通过在计算传输线横截面尺寸后,根据传输线横截面尺寸采用多组步进尺寸进行两次验证,从而可以提高设计成功率和效率,有效克服工艺误差带来的偏差。在制备校准件时,在传输线下设计低电阻率的电阻,可以加大衰减,使传输线频响更加光滑。

附图说明

48.为了更清楚地说明本发明实施例中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动性的前提下,还可以根据这些附图获得其他的附图。

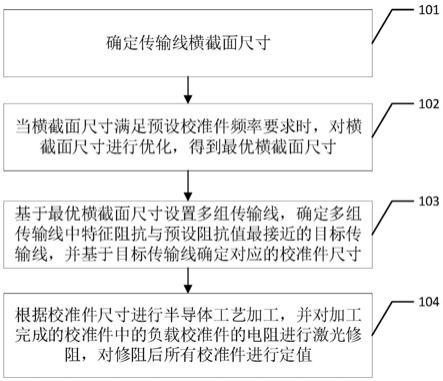

49.图1是本发明实施例提供的一种校准件制备的方法的实现流程图;

50.图2是本发明实施例提供的直通校准件侧视图;

51.图3是本发明实施例提供的直通校准件俯视图;

52.图4是本发明实施例提供的短路校准件示意图;

53.图5是本发明实施例提供的负载校准件侧视图;

54.图6是本发明实施例提供的进行校准件的半导体加工的流程图;

55.图7是本发明实施例提供的进行直通校准件的示意图。

具体实施方式

56.以下描述中,为了说明而不是为了限定,提出了诸如特定系统结构、技术之类的具体细节,以便透彻理解本发明实施例。然而,本领域的技术人员应当清楚,在没有这些具体细节的其它实施例中也可以实现本发明。在其它情况中,省略对众所周知的系统、装置、电路以及方法的详细说明,以免不必要的细节妨碍本发明的描述。

57.为使本发明的目的、技术方案和优点更加清楚,下面将结合附图通过具体实施例来进行说明。

58.图1为本发明实施例提供的一种校准件制备的方法的实现流程图,校准件一般包含solt、lrrm、lrm、trl和multiline trl五种校准件。其中常见的实现形式是直通传输线、开路校准件、短路校准件和负载校准件。直通传输线是一个两端口校准件,开路校准件、短路校准件和负载校准件都是两个单端口的校准件。负载校准件一般是50ω或100ω的电阻。校准件的设计过程详述如下:

59.步骤101,确定传输线横截面尺寸。

60.传输线横截面尺寸包括中心导体的宽度w和中心导体与对应地板的间距g,如图2所示的直通校准件侧视图,图3所示为直通校准件的俯视图,图2和图3中还包括地板宽度g1,g1=k1(2g w),k1的值为0.3至3中的任一值。这样当确定了中心导体的宽度w和中心导体与对应地板的间距g后,就可以确定地板宽度了。

61.可选的,本步骤确定传输线横截面尺寸,可以包括:

62.获取衬底厚度、衬底介电常数、设置在衬底上的金属的电导率和金属厚度;根据衬底厚度、衬底介电常数、电导率和金属厚度,得到传输线横截面尺寸。

63.这里采用仿真软件,输入衬底厚度、衬底介电常数、电导率和金属厚度,即可得到对应的传输线横截面尺寸,即得到中心导体的宽度w和中心导体与对应地板的间距g。仿真软件可以为empro。

64.步骤102,当横截面尺寸满足预设校准件频率要求时,对横截面尺寸进行优化,得到最优横截面尺寸。

65.在本步骤之前,还可以包括:检测横截面尺寸是否满足预设校准件频率要求,当横截面尺寸满足预设校准件频率要求时,执行步骤102,当横截面尺寸不满足预设校准件频率要求时,重新返回步骤101执行。

66.可选的,检测横截面尺寸是否满足预设校准件频率要求时,可以根据横截面尺寸计算校准件频率;再检测校准件频率是否大于或等于预设校准件频率。需要说明的是,预设校准件频率为需求的校准件频率,例如客户的需求等。根据横截面尺寸计算的校准件频率为传输线理论最高频率,即横截面尺寸对应的校准件频率大于或等于客户需求的校准件频率即可。

67.可选的,当校准件频率大于或等于预设校准件频率时,确定横截面尺寸满足预设校准件频率要求。

68.可选的,根据横截面尺寸计算校准件频率,包括:

69.根据计算校准件频率;

70.其中,f表示校准件频率,g表示中心导体与对应地板的间距,w表示中心导体的宽度,μ0表示空气磁导率,ε0表示空气的介电常数,εr表示衬底介电常数,h表示衬底厚度。

71.本步骤中对横截面尺寸进行优化,得到最优横截面尺寸,是以s参数中s

11

为仿真目标进行判断的。可选的,对横截面尺寸进行优化,得到最优横截面尺寸包括:

72.将横截面尺寸在第一预设步进范围内变化,得到多组横截面尺寸;

73.对多组横截面尺寸、预设长度的传输线进行仿真,将所有传输线中s

11

最小值对应的横截面尺寸确定为最优横截面尺寸。

74.可选的,第一预设步进范围为1μm~5μm。即w和g都以1μm~5μm为步进,则取值范围分别为(w-5~w 5)μm,(g-5~g 5)μm。例如多组横截面尺寸可以分别为(w-1)μm和(g-1)μm、(w-2)μm和(g-2)μm、(w 3)μm和(g 3)μm等等。

75.预设长度可以为100μm至500μm之间的任意值,例如传输线可以为100μm的传输线,200μm的传输线等。

76.我们将上述确定的传输线的多组横截面尺寸和预设长度输入到仿真软件中,可以得到每根传输线对应的s

11

,选取s

11

最小值对应的横截面尺寸确定为最优横截面尺寸。

77.本步骤中对横截面尺寸进行优化时,根据传输线横截面尺寸采用多组步进尺寸进行仿真验证,从而可以得到最优的横截面尺寸,提高设计成功率和效率,有效克服工艺误差带来的偏差。

78.步骤103,基于最优横截面尺寸设置多组传输线,确定多组传输线中特征阻抗与预设阻抗值最接近的目标传输线,并基于目标传输线确定对应的校准件尺寸。

79.确定出最优横截面尺寸后,加工版图,以确定出特征阻抗最接近50ω的传输线的尺寸。因此这里预设阻抗值为50ω。

80.可选的,本步骤可以包括:

81.将最优横截面尺寸在第二预设步进范围内变化,得到多组最优横截面尺寸,并基于所述多组最优横截面尺寸和每组最优横截面尺寸对应的至少三个长度进行不同的传输线版图加工;

82.采用预设电阻对传输线特征阻抗进行标定;

83.基于传输线版图和预设电阻,测量每根传输线的特征阻抗,确定与预设电阻的阻抗值最接近的特征阻抗对应的传输线为目标传输线。

84.这里第二预设步进范围与第一预设步进范围不同。第二预设步进范围可以为0.5μm至1μm。因此得到的多组最优横截面尺寸可以为(w-0.5)μm和(g-0.5)μm、(w-1)μm和(g-1)μm、(w 1)μm和(g 1)μm等等。

85.预设电阻可以为50ω的电阻。

86.本步骤中目标传输线时,根据传输线横截面尺寸采用多组步进尺寸,以及采用不同的传输线长度进行仿真验证,从而可以得到与预设阻抗值最接近的目标传输线,提高设计成功率和效率,有效克服工艺误差带来的偏差。

87.校准件包括开路校准件、短路校准件和负载校准件,基于目标传输线确定对应的开路校准件、短路校准件和负载校准件尺寸。一般短路校准件、开路校准件和负载校准件均是两个相同校准件同时存在,这样两个短路校准件的左右两片金属尺寸完全一样、两个开路校准件的左右两片金属尺寸完全一样和两个负载校准件的左右两片金属尺寸完全一样,且四个电阻的尺寸也保持一致,如图4所示的短路校准件和图5所示的负载校准件。参见图4和图5,两个短路校准件、两个开路校准件和两个负载校准件两片之间从最左边图形到最右边的图形距离与直通传输线距离相同。短路校准件、开路校准件和负载校准件的带线宽度一般为35μm~60μm。开路有两种表现形式,一种是在片s参数测试系统中的探针什么也不接触,实现开路,另一种是负载校准件去掉电阻后,实现开路。

88.参见图4和图5,短路校准件中的ws1=ws2,对于ws1和ws2的值大于30μm即可,一般ws1和ws2的值的范围为40μm至100μm。直通长度为(ws1 ws2 d)μm。例如图4中d=100μm,ws1=ws2=50μm,l=650μm。图5中,负载校准件的wl1=wl2=50μm,g2=260.5μm,中心导体宽度为w2。图5中的r表示电阻,电阻值可以为50ω或者100ω。

89.步骤104,根据校准件尺寸进行半导体工艺加工,并对加工完成的校准件中的负载校准件的电阻进行激光修阻,对修阻后所有校准件进行定值。

90.可选的,在确定了校准件的尺寸后,即可进行校准件的半导体加工。如图6所示,详

述如下:

91.步骤601,根据确定的校准件尺寸制备带线和电阻对应的掩模版。

92.校准件采用带线和电阻两种工艺,因此根据确定的校准件尺寸制备相应的掩模版。这里掩模版上有带线和电阻的图案,其他的图案需要清洗掉。

93.步骤602,对陶瓷衬底进行清洗和干燥,陶瓷衬底的任一面抛光。

94.陶瓷衬底可以为单面抛光的996陶瓷衬底,在制备校准件之前,需要先将衬底清洗和干燥。

95.本步骤中,对陶瓷衬底进行清洗和干燥,可以包括:

96.在第一清洗液中,将陶瓷衬底于预设温度范围内煮第一预设时间后取出,用水冲洗至陶瓷衬底的ph为中性;将经过第一步处理的陶瓷衬底在氢氟酸中浸泡第二预设时间,用水冲洗至陶瓷衬底的ph为中性;在第二清洗液中,将经过第二步处理的陶瓷衬底于预设温度下煮第一预设时间后取出,用水冲洗至陶瓷衬底的ph为中性;将陶瓷衬底使用经过干燥过滤的氮气吹干。

97.其中,第一清洗液为水、氨水和过氧化氢混合而成,其体积比依次为4:1:1;

98.第二清洗液为水、盐酸和过氧化氢混合而成,其体积比依次为4:1:1;

99.预设温度范围为80℃至90℃构成的范围。需要说明的是,在第一清洗液或者第二清洗液中煮时,只要将温度保持在80℃至90℃之间即可,不需要在煮的过程中一直保持一个温度不变。

100.第一预设时间为10min至15min中的任一时间;

101.第二预设时间为2min。

102.步骤603,在陶瓷衬底的抛光面上溅射电阻层。

103.将陶瓷衬底清洗干燥后,采用磁控溅射设备,在陶瓷衬底的抛光面上溅射电阻层。

104.可选的,电阻层采用材料为nic或tan;电阻层的厚度为40nm至100nm中的任一值。

105.在制备校准件时,在传输线下设计低电阻率的电阻,可以加大衰减,使传输线频响更加光滑。

106.步骤604,在电阻层上溅射合金层。

107.采用磁控溅射设备,在电阻层上溅射合金层。

108.可选的,合金层采用材料为ti/w,其中ti和w的比例可以为3:1;合金层的厚度为50nm至1μm中的任一值。其中,合金层的厚度可以为50nm、100nm、1μm。

109.步骤605,在合金层的表面上,将掩模版图形中的带线电镀金属。

110.采用电镀设备,在ti/w合金的表面上,将掩模版图形中的带线电镀纯度大于90%的金。例如金的纯度为90%、95%、99%等。优选采用99%的金。

111.可选的,带线采用材料为纯度为99%的金,带线电镀的厚度为1μm至10μm中的任一值,例如带线电镀厚度可以为1μm、4.7μm、6μm、10μm等。

112.在电镀之后,需要进行清洗和烘干。

113.步骤606,在制备了金属带线的校准件表面涂覆光刻胶,依次将掩模版图形外的合金和电阻腐蚀掉,得到校准件。

114.电镀完成后,需要将掩模版图形外的合金层和电阻层腐蚀掉,仅剩下图形区域对应的合金层和电阻层。如图7所示制备完成的直通校准件,其中,701为陶瓷衬底,702为nicr

电阻,703为ti/w合金,704为金。

115.需要说明的是,制备不同的校准件时,仅需加工不同的掩模版,后续的步骤601-步骤606的过程不变。

116.在执行完步骤606后,还需要对制备完成的校准件进行清洗和烘干,然后采用镜检检测校准件是否合格。这里镜检指在显微镜下看校准件是否满足条件,如果满足就是合格品,不满足就是废品。镜检的对象可以是校准件上的金是否存在明显的过粗或过细,是否存在多余的光刻胶等。

117.当加工完成校准件之后,对负载校准件中的电阻进行激光修阻,这里可以采用现有技术中的修阻系统执行,在此不进行详细描述。

118.修阻完成后,对校准件进行定值,此时可以采用多线trl校准方法对开路校准件、短路校准件和负载校准件进行定值。需要说明的是,在校准件定值过程中,保证校准件定值用的针尖距与自校准采用多线trl校准方法时针尖距一致,以减小寄生参量对校准准确度的影响。

119.上述校准件制备的方法,通过首先设计校准件的尺寸,然后根据校准件的尺寸进行校准件的工艺制备,从而得到校准件。在进行校准件的尺寸设计时,本技术中通过在计算传输线横截面尺寸后,根据传输线横截面尺寸采用多组步进尺寸进行两次验证,从而可以提高设计成功率和效率,有效克服工艺误差带来的偏差。在制备校准件时,在传输线下设计低电阻率的电阻,可以加大衰减,使传输线频响更加光滑。

120.应理解,上述实施例中各步骤的序号的大小并不意味着执行顺序的先后,各过程的执行顺序应以其功能和内在逻辑确定,而不应对本发明实施例的实施过程构成任何限定。

121.本发明实施例还提供一种校准件,其采用上述任一实施例描述的校准件制备的方法制备得到,并且具有上述任一实施例制备校准件过程中产生的有益效果。

122.以上所述实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的精神和范围,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。