1.本发明涉及半导体器件技术领域,尤其涉及一种功率半导体模块封装结构。

背景技术:

2.在未来新一代功率模块在电动汽车,轨道交通和智能电网中,多个功率模块并联形成同一桥臂再组成多相开关应用的设计在高功率组件中逐渐推广。这种方法解决和简化了将所有芯片同时并联所遇到的芯片并联电磁均衡以及多芯片或衬板键合到大尺寸的基板或者散热器上的焊接或烧结工艺所遇到的热-机失效等难题。

3.在电力电子能量转换应用中,为适应高速率高能量开关转换,功率模块内部通常采用并联多个功率芯片的方法,形成单开关或半桥电路结构。为提高多芯片并联模块的性能,功率模块需要低电感回路和低电磁干扰的模块封装结构。在使用相同模块满足不同功率等级的应用需求时,有一种易于采用的方法是将相同的模块进一步并联成为同一桥臂,如2个,3个,4个,或者更多相同的模块再度并联组成单一桥臂,三组这样的桥臂组成三相六开关的功率系统来提高功率组件系统的整体输出功率。

4.在此类多个半桥模块并联形成桥臂的更高能量功率开关过程中,多模块组成的同一桥臂在系统的开关能量交替转换过程中,共同工作在开通和关断状态。相邻的并联模块的上端或者下端在工作状态下同为开通状态或者关闭状态,同一桥臂的上开关管或下开关管形成相同的温度变化,模块间热耦合系数高。并联模块的上管或下管分别工作在相同状态时,进行冷却工作的散热流体对相邻的多个开关在高功率状况下的散热效率会受到影响,由于模块间的热耦合效应会造成模块温升过快,不利于模块的长期工作可靠性。

技术实现要素:

5.有鉴于此,本发明的目的在于提出一种功率半导体模块封装结构,以解决现有的功率模块升温过快无法实现长期可靠工作的问题。

6.基于上述目的,本发明提供了一种功率半导体模块封装结构,包括:封装基板、封装管壳、半桥型功率半导体模块;所述封装管壳与所述封装基板紧固连接,形成容纳空间;所述半桥型功率半导体模块设置在所述容纳空间内;

7.所述半桥型功率半导体模块包括并联设置在所述封装基板上的配对的上开关管和下开关管,且所述上开关管和所述下开关管在水平方向相对设置;所述上开关管包括键合在所述基板上的第一衬板和键合在所述第一衬板上的功率半导体芯片组、主功率端子和辅助控制端子;所述下开关管包括键合在所述基板上的第二衬板和键合在所述第二衬板上的功率半导体芯片组、主功率端子和辅助控制端子;所述第一衬板和所述第二衬板之间通过主功率端子辅助控制端子和模块级键合线连接,所述主功率端子和所述辅助控制端子的顶部外延伸出所述封装管壳。

8.在其中一个实施例中,所述主功率端子包括正直流功率端子、负直流功率端子和交流功率端子;其中,所述正直流功率端子与所述负直流功率端子分别设置在所述第一衬

板和第二衬板的金属层上,所述交流功率端子的底部引脚设置在所述第一衬板的金属层上;所述正直流功率端子与所述负直流功率端子呈镜像对称设置,以使所述主功率端子导通不同方向电流时电流重叠,形成耦合低电感;所述交流功率端子的顶部与所述正直流功率端子与所述负直流功率端子的顶部呈镜像对称设置。

9.在其中一个实施例中,所述正直流功率端子与所述负直流功率端子均包括安装部、第一导电部和第二导电部;所述安装部与所述第一导电部通过第一弯折部垂直连接,所述第一弯折部的形状与所述封装管壳的形状相适配,使所述安装部外延伸出所述封装管壳;所述第一导电部与所述第二导电部通过第二弯折部垂直连接;

10.所述正直流功率端子的第二导电部与所述负直流功率端子的第二导电部呈重叠耦合结构;所述第二导电部设置多个弯折管脚,多个弯折引脚分别键合在衬板上,以形成高导通电流。

11.在其中一个实施例中,所述交流功率端子包括两个交流安装部、两个交流第一弯折部、交流第一导电部和交流第二导电部;两个所述交流安装部分别通过两个所述交流第一弯折部与交流第一导电部的两个端部连接,以使所述交流功率端子的两个交流安装部分别与所述正直流功率端子的安装部与所述负直流功率端子的安装部镜像对称;所述交流第一导电部与所述交流第二导电部通过交流第二弯折部垂直连接。

12.在其中一个实施例中,所述辅助控制端子包括辅助发射极控制端子以及栅极控制端子;辅助发射极控制端子包括金属端子和设置在金属端子下部的辅助发射极端子;栅极控制端子包括金属端子和设置在金属端子下部的栅极端子;辅助发射极端子的底部引脚和栅极端子的底部引脚分别键合在所述第一衬板/第二衬板远离所述主功率端子一侧的两个端部;

13.功率半导体芯片组的栅极与栅极端子的底部引脚通过衬板键合线连接,功率半导体芯片组的发射极与所述辅助发射极端子的底部引脚通过衬板键合线连接,以通过控制辅助控制端子的辅助发射极-栅极回路形成对芯片的kevin contact控制回路。

14.在其中一个实施例中,所述第一衬板的数量设置为两个,两个所述第一衬板并联设置形成第一衬板组;两个所述第一衬板的衬板辅助控制区域和衬板栅极控制区域分别通过衬板极键合线连接,功率芯片组分别通过衬板极键合线连接;所述开关管辅助控制区域和所述开关管栅极控制区域分别设置在所述衬板辅助控制区域和所述衬板栅极控制区域靠近衬板组竖直方向两端的端部;

15.所述第一衬板组的两个功率半导体芯片组的栅极分别与对应的衬板栅极控制区域和上开关管的栅极控制区域通过衬板极键合线连接;源极/发射极分别与对应的衬板辅助控制区域和上开关管的辅助控制区域通过衬板极键合线连接,形成上管开关kevin contact控制回路。

16.在其中一个实施例中,所述第二衬板的数量设置为两个,两个所述第二衬板并联设置形成第二衬板组;两个所述第二衬板的衬板辅助控制区域和衬板栅极控制区域分别通过衬板极键合线连接,功率芯片组分别通过衬板极键合线连接;所述开关管辅助控制区域和所述开关管栅极控制区域分别设置在所述衬板辅助控制区域和所述衬板栅极控制区域靠近衬板组竖直方向两端的端部;

17.所述第二衬板组的两个功率半导体芯片组的栅极分别与对应的衬板栅极控制区

域和上开关管的栅极控制区域通过衬板极键合线连接;源极/发射极分别与对应的衬板辅助控制区域和上开关管的辅助控制区域通过衬板极键合线连接,形成上管开关kevin contact控制回路。

18.在其中一个实施例中,所述功率芯片组包括并联设置的多个芯片,相邻的两个芯片之间通过芯片键合线连接。

19.在其中一个实施例中,所述功率芯片组的数量设置为多个,多个所述功率芯片组之间并联连接,且相邻两芯片组之间对称布置并通过芯片键合线连接。

20.在其中一个实施例中,所述主功率端子和所述辅助控制端子分别超声键合至第一衬板和第二衬板上。

21.从上面所述可以看出,本发明提供的功率半导体模块封装结构,通过采用上开关管和下开关管在水平方向相对设置的布局方式,即左右布局的上下管结构。能够在多模块并联的情况下,兼顾同一模块内部上下管之间,以及不同模块的并联开关之间的芯片间均匀散热。从而在不改变模块外部散热器和外部组件结构的情况下,实现芯片控制均衡,主电流均衡,热分布均衡,降低模块间的热耦合,提升冷却效率,提高功率模块的长期工作的稳定性,延长模块的使用寿命。

附图说明

22.为了更清楚地说明本发明实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

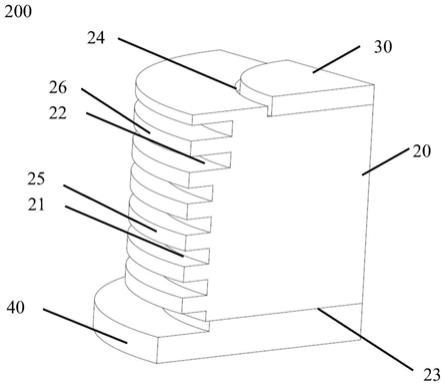

23.图1为传统的功率模块并联形成桥臂的结构示意图;

24.图2为本发明实施例的功率模块并联形成桥臂的结构示意图;

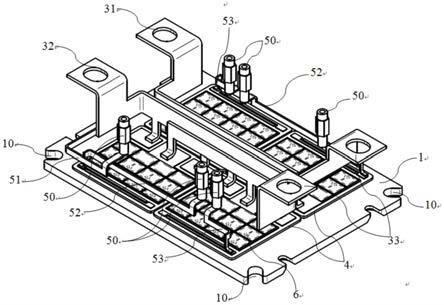

25.图3为本发明实施例的功率半导体模块封装结构的整体结构示意图;

26.图4为本发明实施例的功率半导体模块封装结构除去封装管壳之后的结构示意图;

27.图5为本发明实施例的衬板结构的示意图;

28.图6为本发明实施例的正直流功率端子结构的示意图;

29.图7为本发明实施例的负直流功率端子结构的示意图;

30.图8为本发明实施例的交流功率端子结构的示意图;

31.图9为本发明实施例的功率半导体芯片组与衬板结构的示意图;

32.其中,封装基板-1;基板紧固孔-10;封装管壳-2;正直流功率端子-31;正直流安装部-311、正直流通孔-310、正直流第一导电部-313;正直流第二导电部-315;正直流第一弯折部-312;正直流第二弯折部-314;正直流弯折-316;正直流引脚-317;负直流功率端子-32;负直流安装部-321、负直流通孔-320、负直流第一导电部-323;负直流第二导电部-325;负直流第一弯折部-322;负直流第二弯折部-324;负直流弯折-326;负直流引脚-327;交流功率端子-33;交流安装部-331、交流通孔-330、交流第一导电部-333;交流第二导电部-335;交流第一弯折部-332;交流第二弯折部-334;交流弯折-336;交流引脚-337;功率半导体芯片组-6;第一芯片-61;第二芯片-60;第一衬板-41;第一衬板陶瓷区域-410;正直流功

率端子键合区域-415;交流功率端子连接线键合区域-417;端部-418;第二衬板-40;第二衬板陶瓷区域-400;负直流功率端子键合区域-406;交流功率端子键合区域-407;辅助控制端子-5、金属端子-50、辅助集电极控制端子-51、辅助发射极控制端子-52、栅极控制端子-53、功率半导体芯片组-6;第一衬板辅助控制区域-411;第一衬板栅极控制区域-412;上开关管辅助控制区域-413;上开关管栅极控制区域-414;第二衬板辅助控制区域-401;第二衬板栅极控制区域-402;下开关管辅助控制区域-403;下开关管栅极控制区域-404。

具体实施方式

33.为使本发明的目的、技术方案和优点更加清楚明白,以下结合具体实施例,并参照附图,对本发明进一步详细说明。

34.需要说明的是,除非另外定义,本发明实施例使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。“上”、“下”、“左”、“右”等仅用于表示相对位置关系,当被描述对象的绝对位置改变后,则该相对位置关系也可能相应地改变。

35.本发明的发明人在长期的功率半导体模块封装结构的研究工作中发现,半桥型功率半导体模块在整个功率器件的性能和可靠性方面起到积极重要的作用。传统的将相同模块进一步并联成为同一桥臂以满足不同功率等级的应用需求时,通常采用如图1所示的方法,将上开关管分别设置在并联模块的上端,将下开关管分别设置在并联模块的下端。这种上下式的开关管布局模块无法兼顾同一模块的上下管之间和不同模块的并联开关之间的均匀散热。当冷却水流向为上下方向时,不同模块的并联开关之间的散热条件相同,而同一模块的上下管之间散热条件不同;当冷却水流向为左右方向时,同一模块的上下管之间散热条件相同,而不同模块的并联开关之间的散热条件不同。因此,传统的半导体模块容易产生热耦合效应,导致温升过快,极大地降低模块的使用可靠性,影响模块的使用寿命。

36.发明人从电磁,电,热,机械等方面挑战入手,提出一种新型模块左右开关管内部布局结构,示意图可以如图2所示。通过在不改变模块外部散热器和外部组件结构的情况下,降低模块间的热耦合效应,提升冷却效率,使得功率模块能够长期稳定工作。

37.请参阅图3和图5,本发明实施例提供一种功率半导体模块封装结构,包括:封装基板1、封装管壳2、半桥型功率半导体模块;所述封装管壳2与所述封装基板1紧固连接,形成容纳空间;所述半桥型功率半导体模块设置在所述容纳空间内。

38.所述半桥型功率半导体模块包括并联设置在所述封装基板1上的配对的上开关管和下开关管,且所述上开关管和所述下开关管在水平方向相对设置;所述上开关管包括键合在所述基板上的第一衬板41和键合在所述第一衬板41上的功率半导体芯片组6、主功率端子和辅助端子;所述下开关管包括键合在所述基板上的第二衬板40和键合在所述第二衬板40上的功率半导体芯片组6、主功率端子和辅助端子;所述第一衬板41和所述第二衬板40之间通过主功率端子辅助端子和模块级键合线连接,所述主功率端子和所述辅助端子的顶

部外延伸出所述封装管壳2。

39.本发明提供的功率半导体模块封装结构,通过采用上开关管和下开关管在水平方向相对设置的布局方式,即左右布局的上下管结构。能够在多模块并联的情况下,兼顾同一模块内部上下管之间,以及不同模块的并联开关之间的芯片间均匀散热。当冷却水流向为左右方向时,多模块并联的所有开关管通过控制信号按规律转换开通-关断等状态,每个开关管内的并联芯片的冷却条件更加近似,从而有利于多半导体芯片并联时的结温均匀分布和热机稳定性。从而在不改变模块外部散热器和外部组件结构的情况下,实现芯片控制均衡,主电流均衡,热分布均衡,降低模块间的热耦合,提升冷却效率,提高功率模块的长期工作的稳定性,延长模块的使用寿命。

40.请参阅图4,封装基板1的材料满足导热性能良好还有机械性能强不易受热变形,如alsic铝碳化硅材料、mgsic镁碳化硅材料或铜材料。在实际应用时,可以根据不同应用需求来选择。封装基板1可以采用不同的形状,例如板状。封装基板1上可以设置有基板紧固孔10。基板紧固孔10具体可以设置在封装基板1的四个端部。基板紧固孔10具体可以为开槽形状。通过在基板的四个端部分别设置开槽形状的基板紧固孔10,便于封装。其中,基板紧固孔10优选为基本制备时直接成型的预留孔,以降低封装成本。

41.请参阅图5,第一衬板41和第二衬板40都为陶瓷材质的衬板。可以为高耐压绝缘、高散热效率、高热-机可靠性的陶瓷材质的衬板。例如由氧化铝al2o3、氮化铝aln、氮化硅sin等材料中的至少一种制备所得的陶瓷材质的衬板。陶瓷材质的衬板的上下表面均设置导电金属层。衬板下表面键合在所述基板上,例如可以通过焊接或银烧结等工艺键合到基板上。衬板上表面的金属层经过考虑电磁均流等因素,完成导电,控制等功能。

42.如图3至图5所示,所述主功率端子包括正直流功率端子31、负直流功率端子32和交流功率端子33三种不同功能的端子。

43.其中,所述正直流功率端子31与所述负直流功率端子32分别设置在所述第一衬板41和第二衬板40的金属层上,所述交流功率端子33的底部引脚设置在所述第一衬板41的金属层上;所述正直流功率端子31与所述负直流功率端子32呈镜像对称设置,以使所述主功率端子导通不同方向电流时电流重叠,形成耦合低电感;所述交流功率端子33的顶部与所述正直流功率端子31与所述负直流功率端子32的顶部呈镜像对称设置。

44.所述正直流功率端子31与所述负直流功率端子32均包括安装部、第一导电部和第二导电部;所述安装部与所述第一导电部通过第一弯折部垂直连接,所述第一弯折部的形状与所述封装管壳2的形状相适配,使所述安装部外延伸出所述封装管壳2;所述第一导电部与所述第二导电部通过第二弯折部垂直连接。所述正直流功率端子31的第二导电部与所述负直流功率端子32的第二导电部呈重叠耦合结构;所述第二导电部设置多个弯折管脚,多个弯折引脚分别键合在衬板上,以形成高导通电流。

45.通过正直流功率端子31和负直流功率端子32的与衬板结构相匹配的简易弯折部和弯折管脚,能够实现高电流的导通;配合大电流大面积重叠的第二导电部,产生磁场耦合效应,降低整个模块的有效电感。

46.如图6所示,所述正直流功率端子31包括正直流安装部311,在正直流安装部311上开设有正直流通孔310,用于将正直流功率端子31紧固定在封装管壳2上,导通主电流。所述正直流安装部311伸出封装管壳2外。

47.所述正直流第一弯折部312的两端分别连接正直流安装部311和正直流第一导电部313,使正直流安装部311和正直流第一导电部313垂直连接。所述正直流安装部311的形状与所述封装管壳2的形状相适配,使所述正直流安装部311水平延伸出所述封装管壳2。

48.所述正直流第一导电部313与正直流第二导电部315通过正直流第二弯折部314连接。正直流第二弯折部314与所述正直流第一弯折部312相对垂直,使所述正直流第一导电部313与正直流第二导电部315垂直连接。

49.所述正直流第二导电部315靠近第一衬板的边缘设置多个正直流弯折管脚,多个正直流弯折引脚分别键合在第一衬板上,以形成高导通正直流电流。正直流弯折管脚可以设置为4个。其中,正直流弯折管脚包括正直流弯折316和正直流引脚317。

50.如图7所示,所述负直流功率端子32包括负直流安装部321,在负直流安装部321上开设有负直流通孔320,用于将负直流功率端子32紧固定在封装管壳2上,导通主电流。所述负直流安装部321伸出封装管壳2外。

51.所述负直流第一弯折部322的两端分别连接负直流安装部321和负直流第一导电部323,使负直流安装部321和负直流第一导电部323垂直连接。所述负直流安装部321的形状与所述封装管壳2的形状相适配,使所述负直流安装部321水平延伸出所述封装管壳2。所述负直流第一弯折部322与所述正直流第一弯折部312彼此靠近,重叠,使得所述负直流第一导电部323与正直流第一导电部313彼此远离。

52.所述负直流第一导电部323与负直流第二导电部325通过负直流第二弯折部324连接。负直流第二弯折部324与所述负直流第一弯折部322相对垂直,使所述负直流第一导电部323与负直流第二导电部325垂直连接。所述负直流第二导电部325与所述正直流第二导电部315彼此靠近,重叠,产生正负电流的大面积重叠。所述负直流第二导电部325的面积需与正直流第二导电部315的面积进行电磁分析,以得到合适的低电感设计。

53.所述负直流第二导电部325靠近第二衬板的边缘设置多个负直流弯折管脚,多个负直流弯折管脚分别键合在衬板上,以形成高导通负直流电流。负直流弯折管脚可以设置为4个。其中,负直流弯折管脚包括负直流弯折326和负直流引脚327。负直流弯折326和正直流弯折316彼此靠近,重叠。负直流引脚327与正直流引脚317彼此远离。

54.如图8所示,所述交流功率端子33包括两个交流安装部331、两个交流第一弯折部332、交流第一导电部333和交流第二导电部335。两个所述交流安装部331分别通过两个所述交流第一弯折部332与交流第一导电部333的两个端部连接,以使所述交流功率端子33的两个交流安装部331分别与所述正直流功率端子31的安装部与所述负直流功率端子32的安装部镜像对称。所述交流第一导电部333与所述交流第二导电部335通过交流第二弯折部334垂直连接。

55.其中,两个所述交流安装部331结构相同,两个交流第一弯折部332结构相同。在交流安装部331上开设有交流通孔330,用于将交流功率端子33紧固在封装管壳2上,导通主电流。所述交流安装部331伸出封装管壳2外。

56.所述交流第一弯折部332与交流第二弯折部334相对垂直,使所述交流第一导电部333与交流第二导电部335垂直连接。所述交流第一导电部333的形状与所述正直流第一导电部313和所述负直流第一导电部323镜像对称设置后的形状相适配。

57.如图4所示,所述功率半导体芯片组6超声键合在第一衬板41/第二衬板40的中部,

包括多个并联设置的芯片。如图9所示,并联设置的相邻两个芯片之间通过芯片键合线连接,以降低并联芯片因为大电流造成的电势差所导致的震荡和电磁干扰。多个可以为两个或三个。所述芯片的内部均设置有内电阻。

58.如图5和图9所示,在一个实施例中,功率半导体芯片组6包括三个并联设置的第一芯片61和第二芯片60。其中,第一芯片61设置为一个,第二芯片60设置为两个。第一芯片61设置在靠近主功率端子的位置,两个所述第二芯片60设置在所述第一芯片61远离所述主功率端子的一侧,且两个所述第二芯片60相邻设置。

59.所述第一芯片61与所述第二芯片60可以选自碳化硅mosfet功率芯片和igbt功率芯片。例如,第一芯片61为igbt功率芯片,所述第二芯片60为碳化硅mosfet功率芯片;或者第一芯片61为碳化硅mosfet功率芯片,所述第二芯片60为igbt功率芯片。

60.在一个实施例中,所述功率半导体芯片组6的数量设置为多个,多个所述功率半导体芯片组6之间并联连接,且相邻两个功率半导体芯片组6之间对称布置并通过芯片键合线连接,以降低并联设置的功率半导体芯片组6因为大电流造成的电势差所导致的震荡和电磁干扰。

61.对应地,在第一衬板41的金属层设置功率半导体芯片组6键合区域,两个正直流功率端子键合区域415,和交流功率端子连接线键合区域417,使正直流功率端子31与交流功率端子33通过键合线连接,形成正交流电流回路。其中,两个正直流功率端子键合区域415对称间隔设置在第一衬板41靠近第二衬板40的端部。交流功率端连接线键合区域417设置在两个所述正直流功率端子键合区域415的间隔区域内。且交流功率端子连接线键合区域417呈t型,在t型的竖直部靠近功率半导体芯片组6。

62.功率半导体芯片组6与t型的竖直部的两个端部418通过衬板键合线连接,交流功率端子连接线键合区域417与第二衬板40的交流功率端子键合区域通过连接线键合,以使功率半导体芯片组6和交流功率端子33连接;配合设置在交流功率端子连接线键合区域417两侧的正直流功率端子31键合区域,使交流功率端子33与正直流功率端子31形成连接,形成上开关管电流通路。

63.在第二衬板40的金属层设置两个负直流功率端子键合区域406,和交流功率端子键合区域407,使负直流功率端子32与交流功率端子33通过键合连接,形成负直流电流回路。其中,两个负直流功率端子键合区域406对称间隔设置在第二衬板40靠近第一衬板41的端部。交流功率端子键合区域407设置在两个所述负直流功率端子键合区域406的间隔区域内。

64.功率半导体芯片组6与两个负直流功率端子键合区域406通过衬板键合线连接,以使功率半导体芯片组6和负直流功率端子32形成负直流连接;配合设置在两个所述负直流功率端子键合区域406的间隔区域内的交流功率端子键合区域407,使负直流功率端子32与交流功率端子33形成连接,从而形成下开关管电流通路。

65.如图4所示,辅助控制端子5包括金属端子50以及设置在金属端子50下部的辅助端子。辅助端子与金属端子50通过激光键合或焊接等工艺形成一体连接。其中,金属端子50与封装管壳2固定连接,用于将辅助端子固定在封装管壳2上,且金属端子50的顶部外延伸出所述封装壳体的顶部。辅助端子可以通过螺母紧固在封装管壳2上,金属端子50上端内部设置有螺纹,可以避免尖锐端以及可能造成的尖端强电场分布。辅助端子的底部引脚与所述

第一衬板41/第二衬板40连接,可以通过超声键合usw或者焊接工艺固定到第一衬板41/第二衬板40的金属层。

66.在一个实施例中,辅助控制端子5包括辅助集电极控制端子51、辅助发射极控制端子52以及栅极控制端子53,分别构成半桥型功率半导体模块的辅助集电极、辅助发射极以及栅极。其中,辅助集电极控制端子51包括金属端子50和设置在金属端子50下部的辅助集电极端子。辅助发射极控制端子52包括金属端子50和设置在金属端子50下部的辅助发射极端子。栅极控制端子53包括金属端子50和设置在金属端子50下部的栅极端子。辅助集电极的连接,为已有的技术,此处不再赘述。

67.辅助发射极控制端子52以及栅极控制端子53相邻设置在第一衬板41/第二衬板40上金属层的中部,辅助发射极端子和栅极端子的底部引脚分别键合在第一衬板41/第二衬板40远离所述主功率端子一侧的两个端部,且辅助发射极端子的底部引脚和栅极端子的底部引脚呈镜像对称设置。功率半导体芯片组6的栅极与栅极端子的底部引脚通过衬板键合线连接,功率半导体芯片组6的发射极与所述辅助发射极端子的底部引脚通过衬板键合线连接,以通过控制辅助控制端子5的辅助发射极-栅极回路形成对芯片的kevin contact控制回路,实现对芯片的均衡控制。通过在衬板结构中实现对功率芯片的kevin contact控制,能够在该衬板简洁设计下,最大化功率芯片的有效利用面积,进而能够对多种不同尺寸,规格以及材料的芯片实现kevin contact控制。例如能够适应于高电流的硅基igbt芯片和新型宽禁带碳化硅mosfet芯片等不同类型的硅基和宽禁带功率器件。

68.请参阅图5,在第一衬板41上设置未被覆盖的第一衬板陶瓷区域410。第二衬板40上设置未被覆盖的第二衬板陶瓷区域400。所述第一衬板41和所述第二衬板40的金属层分别包括衬板辅助控制区域、衬板栅极控制区域、开关管辅助控制区域和开关管栅极控制区域;所述衬板辅助控制区域和衬板栅极控制区域分别呈长条状且相对间隔设置,且两个区域在靠近第一衬板41/第二衬板40的竖直方向的端部均设置膨大区;所述开关管辅助控制区域和所述开关管栅极控制区域分别设置在所述衬板辅助控制区域和所述衬板栅极控制区域靠近衬板竖直方向两端的端部;

69.所述第一衬板41和所述第二衬板40的功率半导体芯片组6的栅极分别与对应的衬板的栅极控制区域和开关管的栅极控制区域通过衬板极键合线连接;源极/发射极分别与对应的衬板的辅助控制区域和开关管的辅助控制区域通过衬板极键合线连接,形成kevin contact控制回路。

70.其中,所述第一衬板41上表面的金属层包括第一衬板辅助控制区域411、第一衬板栅极控制区域412、上开关管辅助控制区域413和上开关管栅极控制区域414;所述第二衬板40上表面的金属层包括第二衬板辅助控制区域401、第二衬板栅极控制区域402、下开关管辅助控制区域403和下开关管栅极控制区域404。

71.在一个实施例中,请参阅图9,所述第一衬板41的数量设置为两个,两个所述第一衬板41并联设置形成第一衬板组,也即半桥型功率半导体模块的上开关管。两个所述第一衬板41的第一衬板辅助控制区域411和第一衬板栅极控制区域412分别通过衬板极键合线连接,功率半导体芯片组分别通过衬板极键合线连接;所述上开关管辅助控制区域413和所述上开关管栅极控制区域414分别设置在所述第一衬板辅助控制区域411和所述第一衬板栅极控制区域412靠近第一衬板41组竖直方向两端的端部。

72.所述第一衬板组的两个功率半导体芯片组6的栅极分别与对应的第一衬板栅极控制区域412和上开关管栅极控制区域414通过衬板极键合线连接;源极/发射极分别与对应的第一衬板辅助控制区域411和上开关管辅助控制区域413通过衬板极键合线连接,形成上管开关kevin contact控制回路。

73.所述第二衬板40的数量设置为两个,两个所述第二衬板40并联设置形成第二衬板组,也即半桥型功率半导体模块的下开关管。两个所述第二衬板40的第二衬板辅助控制区域401和第二衬板栅极控制区域402分别通过衬板极键合线连接,功率半导体芯片组分别通过衬板极键合线连接;所述下开关管辅助控制区域403和所述下开关管栅极控制区域404分别设置在所述第二衬板辅助控制区域401和所述第二衬板栅极控制区域402靠近衬板组竖直方向两端的端部。

74.所述第二衬板40组的两个功率半导体芯片组6的栅极分别与对应的第二衬板栅极控制区域402和下开关管栅极控制区域404通过衬板极键合线连接;源极/发射极分别与对应的第二衬板辅助控制区域401和下开关管辅助控制区域403通过衬板极键合线连接,形成下管开关kevin contact控制回路。

75.本发明实施例提供的功率半导体模块封装结构,通过新型的在水平线上左右设置的上下开关管的布局,结合相应的新型低电感母排结构,并对模块内部的芯片开关控制采用kevin contact型式,能够实现在高功率多个模块并联形成半桥桥臂的状况下,降低模块在开通和关断状况下的热阻,提高有效散热效率,并实现低电感,低电磁干扰以及长期应用的高可靠性。其中,通过左右布局的上开关管结构和下开关管结构,能够在多模块并联的情况下,兼顾同一模块内部上开关管和下开关管之间,和不同模块的并联开关之间的芯片间均匀散热。通过采用与新型衬板结构相匹配的简易预弯折新型正直流功率端子31、负直流功率端子32和交流功率端子33,保证高电流的导通,并采用流经正负直流功率端子的大电流大面积的重叠,使其所产生的磁场耦合效应降低整个模块的有效电感。通过采用超声键合工艺的正直流功率端子31、负直流功率端子32、交流功率端子33,能够提高功率端子的可靠性,有更强的抗温度冲击,抗机械振动方面的能力。通过在新型衬板布局中,采用kevin contact控制回路实现对多个并联功率半导体芯片组6的均衡控制回路,并降低控制回路电感,降低电磁干扰emi的控制,且能够适用于多种不同尺寸、规格以及材料的芯片。通过采用直接超声键合到衬板的辅助控制端子5,节约传统模块所采用的控制pcb版,简化生产流程,提高辅助控制端子5的键合可靠性。

76.所属领域的普通技术人员应当理解:以上任何实施例的讨论仅为示例性的,并非旨在暗示本公开的范围(包括权利要求)被限于这些例子;在本发明的思路下,以上实施例或者不同实施例中的技术特征之间也可以进行组合,步骤可以以任意顺序实现,并存在如上所述的本发明的不同方面的许多其它变化,为了简明它们没有在细节中提供。

77.另外,为简化说明和讨论,并且为了不会使本发明难以理解,在所提供的附图中可以示出或可以不示出与集成电路(ic)芯片和其它部件的公知的电源/接地连接。此外,可以以框图的形式示出装置,以便避免使本发明难以理解,并且这也考虑了以下事实,即关于这些框图装置的实施方式的细节是高度取决于将要实施本发明的平台的(即,这些细节应当完全处于本领域技术人员的理解范围内)。在阐述了具体细节(例如,电路)以描述本发明的示例性实施例的情况下,对本领域技术人员来说显而易见的是,可以在没有这些具体细节

的情况下或者这些具体细节有变化的情况下实施本发明。因此,这些描述应被认为是说明性的而不是限制性的。

78.尽管已经结合了本发明的具体实施例对本发明进行了描述,但是根据前面的描述,这些实施例的很多替换、修改和变型对本领域普通技术人员来说将是显而易见的。

79.本发明的实施例旨在涵盖落入所附权利要求的宽泛范围之内的所有这样的替换、修改和变型。因此,凡在本发明的精神和原则之内,所做的任何省略、修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。