1.本公开大体上涉及集成电路,并且更具体来说,涉及模拟前端电路。

背景技术:

2.模拟前端电路通常用于集成电路(integrated circuit,ic)中以接收模拟信号并将所述模拟信号转换成数字输入以供在ic内使用。模拟前端电路通常包括放大器和模数转换器(analog-to-digital converter,adc)。这些模拟前端电路可例如用于生物医学应用或音频应用,在这些应用中,模拟前端电路可以将低频率和低振幅信号转换成高分辨率数字信号。这些类型的模拟前端电路还通常用于便携式电池供电装置。因此,此类模拟前端电路需要缩减成本(例如,面积)并减少功率消耗,同时仍保持模拟前端的准确性。

技术实现要素:

3.以下为本发明的各种实施例。

4.在一个实施例中,一种传感器系统包括:放大器,所述放大器具有第一输入、第二输入、第一输出和第二输出;第一采样电容器,所述第一采样电容器联接在第一组开关与所述放大器的所述第一输入之间,所述第一组开关可操作以在采样阶段期间将所述第一采样电容器联接到传感器的输出并在部分跟踪阶段期间将所述第一采样电容器联接到参考电压;第二采样电容器,所述第二采样电容器联接在第二组开关与所述放大器的所述第二输入之间,所述第二组开关可操作以在所述采样阶段期间将所述第二采样电容器联接到所述参考电压并在所述部分跟踪阶段期间将所述第二采样电容器联接到所述传感器的所述输出;以及模数转换器(analog to digital converter,adc)电路,所述模数转换器电路具有低通传递函数,所述模数转换器电路具有联接到所述放大器的所述输出的输入。在一个方面中,所述adc转换器电路是∑-δ转换器电路。在另一方面中,在所述部分跟踪阶段期间,所述adc转换器电路在高于第一采样电容器采样频率和第二采样电容器采样频率的频率下对所述放大器的所述输出进行采样。在上述实施例的另一方面中,所述第一采样电容器在所述采样阶段期间联接到传感器的第一输出,并且所述第一采样电容器在所述部分跟踪阶段期间联接到电源电压和所述传感器的第二输出中的一个。在另一方面中,所述第二采样电容器在所述采样阶段期间联接到所述电源电压和所述传感器的所述第二输出中的所述一个,并且所述第二采样电容器在所述部分跟踪阶段期间联接到所述传感器的所述第一输出。在又一方面中,所述传感器系统进一步包括第三采样电容器,所述第三采样电容器具有联接到所述放大器的所述第一输出的第一端和在所述采样阶段期间联接到所述放大器的所述第一输入并且在所述部分跟踪阶段期间联接到第二电源电压的第二端。在又一方面中,所述传感器系统进一步包括第四采样电容器,所述第四采样电容器具有联接到所述放大器的所述第二输出的第一端和在采样阶段期间联接到所述放大器的所述第二输出并且在所述部分跟踪阶段期间联接到所述第二电源电压的第二端。在再一方面中,所述第三采样电容器和所述第四采样电容器在所述部分跟踪阶段期间联接到所述第二电源电压以实

施相关双重采样功能。在再一方面中,所述第一采样电容器、所述第二采样电容器、所述第三采样电容器和所述第四采样电容器在从采样阶段到部分跟踪阶段的过渡和从部分跟踪阶段到采样阶段的过渡中的一个过渡期间利用非重叠时钟信号联接到所述放大器的所述输出。

5.在另一实施例中,一种感测装置包括:信号处理单元;模数转换器,所述模数转换器具有高于第一采样电容器采样频率的采样频率,所述模数转换器包括低通滤波器传递函数;模拟前端电路,所述模拟前端电路包括:在采样阶段期间,第一采样电容器的第一端连接到模拟输入信号,第二采样电容器的第一端连接到参考信号,并且第一保持电容器和第二保持电容器连接到接地;以及在部分跟踪阶段期间,所述第一采样电容器的所述第一端连接到所述参考电压,所述第二采样电容器的所述第一端连接到所述模拟输入信号,所述第一保持电容器连接到放大器的第一输出,并且所述第二保持电容器连接到所述放大器的第二输出,并且所述第一采样电容器的第二端联接到所述放大器的第一输入,并且所述第二采样电容器的第二端联接到所述放大器的第二输入。

6.在又一实施例中,一种操作模拟前端电路的方法包括:在采样阶段期间:将第一采样电容器的第一端连接到模拟输入信号并且将第二采样电容器的第一端连接到第一参考电压,并且将第一保持电容器和第二保持电容器连接到第一电源电压和第二参考电压中的一个;以及在部分跟踪阶段期间:将所述第一采样电容器的所述第一端连接到所述第一参考电压并且将所述第二采样电容器的所述第一端连接到所述模拟输入信号;将所述第一保持电容器的第一端连接到放大器的第一输出,并且将所述第二保持电容器的第一端连接到所述放大器的第二输出;以及在所述部分跟踪阶段期间将模数转换器联接到所述放大器的所述第一输出和所述第二输出,并且在所述采样阶段期间使所述模数转换器与所述放大器的所述第一输出和所述第二输出解除联接,其中所述第一采样电容器的第二端联接到所述放大器的第一输入,并且所述第二采样电容器的第二端联接到所述放大器的第二输入。在一个方面中,所述第一采样电容器在所述采样阶段期间联接到传感器的第一输出,并且所述第一采样电容器在所述部分跟踪阶段期间联接到第二电源电压和所述传感器的第二输出中的一个。在另一方面中,所述第二采样电容器在所述采样阶段期间联接到所述第二电源电压或所述传感器的所述第二输出中的一个,并且所述第二采样电容器在所述部分跟踪阶段期间联接到所述传感器的所述第一输出。在又一实施例的另一方面中,所述方法进一步包括:在低通滤波器电路中对所述放大器的所述第一输出和所述第二输出进行低通滤波;以及使用模数转换器将来自所述低通滤波器电路的输出从模拟信号转换成数字信号。在另一方面中,所述方法进一步包括使用∑-δ模数转换器(analog to digital converter,adc)电路将所述放大器的所述第一输出和所述第二输出从模拟信号转换成数字信号。在又一实施例的又一方面中,所述方法进一步包括:在所述采样阶段期间:联接所述放大器的所述第一输入与所述放大器的所述第一输出之间的第三电容器;以及联接所述放大器的所述第二输入与所述放大器的所述第二输出之间的第四电容器。在另一方面中,所述方法进一步包括在所述部分跟踪阶段期间将所述第三电容器和所述第四电容器联接到第二电源电压以执行相关双重采样。在另一方面中,所述放大器在所述部分跟踪阶段期间联接到所述模拟输入信号,并且所述放大器的所述输出利用增益跟踪所述模拟输入信号,所述增益取决于所述第一采样电容器与所述第一保持电容器以及所述第二采样电容器

与所述第二保持电容器中的一个的比率。在另一方面中,所述方法进一步包括使用低通滤波器电路和∑-δ模数转换器中的一个来去除所述增益放大器的所述第一输出和所述第二输出中的失真。在另一方面中,在所述部分跟踪阶段期间,所述adc电路在高于所述第一采样电容器和所述第二采样电容器的采样频率的频率下对所述放大器的所述第一输出和所述第二输出进行采样。

附图说明

7.本发明借助于例子示出并且不受附图的限制,在附图中的类似标记指示类似元件。图式中的元件为简单和清楚起见而示出并且不必按比例绘制。

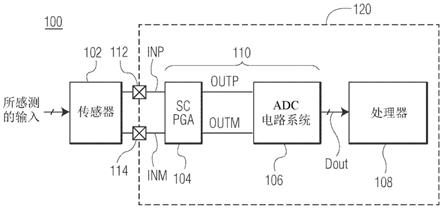

8.图1以框图形式示出根据本发明的一个实施例的系统,所述系统包括联接到具有模拟前端电路的集成电路(integrated circuit,ic)的传感器。

9.图2以框图形式示出根据本发明的一个实施例的图1的模数转换器(analog-to-digital converter,adc)电路系统的更详细视图。

10.图3以框图形式示出根据本发明的一个实施例的图1的模数转换器(analog-to-digital converter,adc)电路系统的更详细视图。

11.图4以部分示意图和部分框图形式示出根据本发明的一个实施例的图1的开关电容器可编程增益放大器(switched capacitor programmable gain amplifier,sc pga)的更详细视图。

12.图5以时序图形式示出根据本发明的一个实施例的图1的系统的各种信号。

13.图6示出图1的系统的示例频域输入和输出。

14.图7以框图形式示出根据本发明的一个实施例的图3的adc电路系统的更详细视图。

具体实施方式

15.在一个方面中,ic的模拟前端电路包括可编程增益放大器(programmable gain amplifier,pga)和模数转换器(analog-to-digital converter,adc)电路系统,其中pga以低于adc的速率进行采样。这使得pga的运算放大器的功率和大小两者均得以缩减。此外,pga使用采样与部分跟踪阶段(与采样与保持阶段或采样与跟踪阶段对照),这允许针对给定pga噪声级缩减采样电容器的大小和pga的功率。然而,采样与部分跟踪在较高频率下引入失真。因此,通过使用adc电路系统与滤波(通过使用∑-δ(sigma-delta,sd)adc或具有任何类型的adc的低通滤波器),所引入的失真和噪声由adc电路系统滤出。以此方式,可实施较小pga,同时仍维持准确的adc转换。

16.图1以框图形式示出包括联接到ic 120的传感器102的传感器系统100。在所示实施例中,传感器102示出为位于ic 120外部,但可替换的是,可位于ic 120内。在一个实施例中,传感器102是医疗传感器,例如心跳监视器。传感器102被联接以接收所感测的输入,并且被联接以经由端112和114将传感器输出提供到sc pga 104(在本文中也被称作pga 104)。在许多应用中,传感器输出提供低频率和低振幅信号。pga104的第一输入(被称作inp)联接到端112,并且pga 104的第二输入(被称作inm)联接到端114。inp和inm对应于到pga 104的差分输入。pga 104提供放大的模拟差分输出,即信号outp和outm,所述信号outp

和outm作为差分输入被提供到adc电路系统106。adc电路系统106将模拟差分输入转换成数字数据流输出dout,所述数字数据流输出dout被提供到处理器108以供进一步处理。pga 104和adc电路系统106形成ic 120的模拟前端电路110。在所示实施例中,处理器108可以是任何类型的数据处理器。

17.在一个实施例中,传感器102分别经由端112和114将模拟差分信号作为inp和inm提供到pga 104。可替换的是,传感器102可被联接以将单端模拟信号提供到端112或114中的一个,而端112或114中的另一个可接收参考电压或可联接到电压供应端,例如vdd或vss。因此,inp和inm可一起被称作差分信号,或者inp或inm中的一个可被称作输入模拟信号并且inp或inm中的另一个可被称作参考信号。

18.图4以部分框图和部分示意图形式示出了根据本发明的一个实施例的pga 104。pga 104包括放大器400、采样电容器c

sample 410和c

sample 412、部分跟踪电容器c

pt 420和c

pt 426、电容器418和436、pga控制电路450以及开关402、404、406、408、414、416、422、424、432、434、428和430。pga控制电路450接收pga时钟信号,并基于pga时钟信号而提供控制信号φpt和φs。φs的断言对应于pga 104的采样阶段,并且φpt的断言对应于pga 104的部分跟踪阶段。pga 104中的每个开关在所述开关的控制输入处接收φs或φpt中的一个,其中所接收控制信号的断言闭合对应开关,使得所述开关在其两个数据端之间导电,并且控制信号的求反(negation)断开对应开关,使得所述开关在其两个数据端之间不导电。

19.inp被提供到pga 104的第一输入并且inm被提供到pga 104的第二输入。第一输入联接到开关402的第一数据端和开关406的第一数据端。第二输入联接到开关404的第一数据端和开关408的第一数据端。开关402的第二数据端和开关404的第二数据端联接到c

sample 410的第一端。开关406的第二数据端和开关408的第二数据端联接到c

sample 412的第一端。开关402和408在其控制输入处接收φs,并且开关404和406在其控制输入处接收φpt。c

sample 410的第二端在放大器400的第一输入(例如,非反相输入)处联接到电路节点438,并且c

sample 412的第二端在放大器400的第二输入(例如,反相输入)处联接到电路节点440。在放大器400的第一输出(例如,反相输出)处的电路节点442提供pga104的第一输出outp。在放大器400的第二输出(例如,非反相输出)处的电路节点444提供pga 104的第二输出outm。放大器400可实施为运算放大器(operational amplifier,opamp)。

20.仍然参考图4,电路节点438联接到开关416的第一数据端和c

pt 420的第一端。电路节点440联接到开关428的第一数据端和c

pt 426的第一端。开关416的第二数据端联接到开关414的第一数据端和电容器418的第一端。开关414的第二数据端联接到接地。开关414的控制输入被联接以接收φpt,并且开关416的控制输入被联接以接收φs。开关428的第二数据端联接到开关430的第一数据端和电容器436的第一端。开关430的第二数据端联接到接地。开关430的控制输入被联接以接收φpt,并且开关428的控制输入被联接以接收φs。电容器418的第二端联接到电路节点442。c

pt 420的第二端联接到开关422的第一数据端和开关424的第一数据端。开关422的第二数据端联接到接地,并且开关424的第二端联接到电路节点442。电容器436的第二端联接到电路节点444。c

pt 426的第二端联接到开关434的第一数据端和开关432的第一数据端。开关434的第二数据端联接到接地,并且开关432的第二端联接到电路节点444。应注意,开关414和430中的每一个开关的第二数据端联接到接地。在一个实施例中,此接地可以是模拟接地,即,正电源与负电源之间的稳定电压,所述稳定电

压用作模拟电路的参考电压。可替换的是,此接地可以是正电源、负电源或共同接地。

21.在操作中,pga 104是开关电容器pga(switched capacitor pga,sc pga),所述sc pga放大输入信号,并且所述sc pga的增益可以数字方式编程。在所示实施例中,pga 104利用相关双重采样(correlated double sampling,cds)以及双重采样方案,双重采样方案按以下两个阶段操作:采样阶段(对应于φs)和部分跟踪阶段(对应于φpt)。应注意,在采样阶段期间对φs进行断言并且在部分跟踪阶段期间对φpt进行断言,因此在任何一个时刻仅对φs和φpt中的一个进行断言。在一个实施例中,φs和φpt可被称作时钟信号。当前已知sc pga通常使用采样与保持方案或采样与跟踪(具有一对一增益)方案进行操作。然而,通过实施双重采样以及部分跟踪方案(具有部分增益),相比于使用当前已知sc pga中的一个sc pga,采样电容器的大小可以较小,其中放大器的功率要求可以减少。

22.参考图4,对于pga 104的采样阶段,对φs进行断言,使得开关402、408、416、422、428和434闭合并且其余开关断开。以此方式,采样电容器联接到输入(例如,c

sample 410经由闭合开关402联接到inp,并且c

sample 412经由闭合开关408联接到inm),并且部分跟踪电容器联接到接地(例如,c

pt 420经由闭合开关422联接在c

sample 410与接地之间,并且c

pt 426经由闭合开关434联接在c

sample 412与接地之间)。(应注意,此接地可以是模拟接地,或可替换的是,此接地可以是正电源、负电源或共同接地。)作为cds方案的部分,电容器420和426在此阶段期间存储放大器的偏移、低频噪声和有限增益误差。采样电容器c

sample 410和c

sample 412利用输入信号vin以差分方式充电,其中vin是inp处的电压(vinp)减去inm处的电压(vinm)。在采样阶段中,电容器418经由闭合开关416联接在放大器400的第一输入(电路节点438)与放大器400的第一输出(电路节点442)之间。类似地,电容器436经由闭合开关428联接在放大器400的第二输入(电路节点440)与放大器400的第二输出(电路节点444)之间。作为cds方案的部分,电容器418和436保持输出电压。

23.对于pga 104的部分跟踪阶段,对φpt进行断言,使得开关404、406、414、424、432和430现在闭合并且其余开关断开。以此方式,采样电容器反向联接到输入inp和inm,并且部分跟踪电容器(也被称作保持电容器)联接到输出outp和outm。也就是说,并非如将在使用采样保持方案的pga中进行的那样将c

sample 410和c

sample 412与输入inp和inm断开连接,c

sample 410实际上经由闭合开关404联接到inm,并且c

sample 412实际上经由闭合开关406联接到inp。c

pt 420经由闭合开关424联接在电路节点438与outp(在电路节点442处)之间,并且c

pt 426经由闭合开关432联接在电路节点440与outm(在电路节点444处)之间。在此配置中,电容器420和426减去在采样阶段期间存储的放大器误差。电容器418和436现在经由闭合开关414和430联接到接地。(如上文所描述,此接地可以是模拟接地,但也可以是正电源电压、负电源电压或共同接地。)在此配置中,电容器418和436对输出电压进行采样,作为cds方案的部分。

24.在部分跟踪阶段中,采样电容器c

sample 410和c

sample 412利用反向输入信号vin以差分方式充电。电荷改变传递到部分跟踪电容器(例如,从c

sample 410到c

pt 420和从c

sample 412到c

pt 426)并产生输出电压vout,其中vout是outp处的电压(voutp)减去outm处的电压(voutm)。因此,vout可表示为vout=(vin-(-vin)*c

sample

/c

pt

=vin*(2c

sample

/c

pt

)。如果在部分跟踪阶段期间输入信号改变了δvin,那么采样电容器上的电荷将改变δvin*c

sample

,并且电荷的此部分还将被传递到部分跟踪电容器,从而产生输出电压vout=vin*(2c

sample

/cpt

δvin*c

sample

/c

pt

)。这是部分跟踪,因为例如当pga 104的增益为一时,c

sample

等于c

pt

的分数,例如c

sample

=0.5*c

pt

,使得输出vout以δvin的分数,例如以0.5*δvin进行跟踪。因此,应注意,部分跟踪阶段向放大的信号提供基于采样电容器与部分跟踪电容器的比率的增益。在所示实施例中,采样电容器和部分跟踪电容器中的每一个被实施为可设置到所需电容以实现所需增益的可变电容器。

25.在利用部分跟踪的所示sc pga 104的情况下,应注意,相比于当前已知采样与保持和采样与跟踪pga,采样电容器较小,这是因为双重采样针对给定噪声级需要的电路面积较小,从而节省成本。另外,在跟踪阶段中不存在用以调整增益的额外电路系统来匹配总pga增益。然而,相比于当前已知pga,通过使用部分跟踪和较小采样电容器,pga104的输出可包括更多失真。然而,在相对于pga采样速率恰当选择adc采样速率的情况下,可使此失真处于较高带外频率,如下文将描述,所述较高带外频率可由adc电路系统106滤出。

26.图2和3以框图形式说明adc电路系统106的实施例。在一个实施例中,如上文所描述,在放大所接收的差分信号时,pga 104在信号路径中引入高频失真。此失真因此由adc电路系统106去除。在例如图2所示的一个实施例中,adc电路系统106可以与adc 204以及低通滤波器202一起实施。在此例子中,低通滤波器202去除高频失真,从而由adc 204以较高准确性转换成数字信号,adc 204可以与任何类型的adc一起实施。

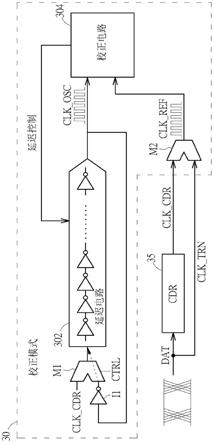

27.在例如图3所示的一个实施例中,adc电路系统106可由∑-δ(sigma delta,sd)adc 302实施。如本领域中已知,sd adc通常包括与数字滤波器串联的∑-δ调制器。调制器将模拟输入信号转换成脉冲波表示。调制器产生噪声整形的输出。在一个实施例中,二阶调制器用以将任何噪声另外整形成较高频率。在调制器中,积分器和因此反馈回路的数目指示sd adc的阶数。在sd adc中,数字滤波器对于去除已经从较低频率整形为较高频率的带外噪声已经是必不可少的。此数字滤波器还将去除由部分跟踪引起的高频失真。在所示实施例中,sd adc 302具有大于pga 104的采样速率的高输入采样速率。还可使用抽取器(decimator)作为数字滤波器的部分对低通滤波器的输出进行向下采样以便减缓输出数据速率。应注意,对于此实施例,可使用任何已知sd adc电路来实施adc电路系统106。

28.图7以框图形式示出sd adc 302(实施为二阶sd adc)的一个实施例的更详细视图,包括系数304至307、求和节点310、312和309、积分器314和316、量化器318和数字滤波器320。系数304至307按比例缩放对应的输入信号或输出信号。sd adc 302接收outp-outm作为输入,并提供dout作为输出。求和节点310在求和输入处接收b1*(outp-outm)并且在减法输入处接收a1*(量化器318的输出)。求和节点310将其结果提供到积分器314(也被称作积分器1)。积分器314的输出按比例c1缩放并被提供到求和节点312的第一求和输入。求和节点312在第二求和输入处接收b2*(outp-outm)并且在减法输入处接收a2*(量化器318的输出)。求和节点312将其结果提供到积分器316(也被称作积分器2)。积分器316的输出按比例c2缩放并被提供到量化器318。量化器318的输出被反馈回系数304和305,并且还被提供到数字滤波器320,并且数字滤波器320提供dout。系数304至307、求和节点310和312、积分器314和316以及量化器318实施将噪声整形的输出提供到数字滤波器320的二阶调制器(由于两个积分器/反馈回路)。如上文关于图3所论述,数字滤波器320包括用以去除已经由调制器整形为较高频率的带外噪声的低通滤波器,并且数字滤波器320还可包括抽取器。

29.图5示出根据本发明的一个实施例的系统100的各种信号的时序图。pga 104的采

样与部分跟踪阶段是基于例如由pga控制电路450接收的pga时钟而产生的。对φs进行断言的采样阶段在pga时钟周期的一个阶段(在所示例子中为对应于时间t0与时间t2之间的ts的高阶段)期间发生,并且对φpt进行断言的部分跟踪阶段在pga时钟周期的另一阶段(所示例子中为对应于时间t2与时间t5之间的tpt的低阶段)期间发生。在一个实施例中,ts<tpt。如图5所示,pga采样阶段对应于φs被断言,并且部分跟踪阶段对应于φpt被断言。在一个例子中,pga部分跟踪阶段和pga采样阶段中的每一个相对于pga时钟的边沿延迟。例如,φs在时间t1被断言,这在时间t0之后的延迟时发生,并且φpt在时间t3被断言,这在时间t2之后的延迟时间(td)发生。

30.在pga 104的pga采样阶段期间,停用adc电路系统106,即,不执行采样和转换。举例来说,adc电路系统106的采样阶段仅在pga104的部分跟踪阶段期间(在时间段tpt期间,具体来说,在t3与t5之间的时间期间)发生。在所示实施例中,针对adc电路系统106示出3个adc采样阶段,然而,可存在更多采样阶段,例如8个采样阶段。因此,可以看出,adc电路系统106的采样速率大于pga 104的采样速率(例如,在所示例子中为3对1)。

31.图5还示出了对应于vin=vinp-vinm的pga输入信号,以及对应于vout=voutp-voutm的pga输出信号(利用如上文所描述的部分跟踪)。在pga采样阶段期间,vout保持稳定,直到采样阶段结束而进入部分跟踪阶段,其中vout利用部分增益跟踪vin。

32.图6示出根据本发明的一个实施例的系统100的各种频域曲线图。第一曲线图对应于pga 104的vin并且包括处于频率fin下的基频分量600,频率fin是输入频率。第二曲线图对应于pga 104的vout并且包括处于频率fin下的频率分量602,而且还包括发生在频域的较高频率中的频率分量604。这些频率分量对应于由pga 104引入的失真,并且所述频率分量的频率是基于每pga采样的adc采样数(例如,f(n)=k*(fs/n) /-fin,其中n是每pga采样的adc采样数,k=正整数,并且fs是有效adc采样频率n/(ts tpt))。然而,adc电路系统106(由于例如图2中的低通滤波器或由于例如图3中的sd adc的数字滤波器)滤出,即去除这些失真分量,从而产生对应于adc输出的第三曲线图。此曲线图包括在频率fin下的基频分量606,但不具有失真分量。以此方式,由pga 104的部分跟踪方案引入的高频失真由adc电路系统解决。

33.因此,可理解可如何通过使用采样与部分跟踪pga在模拟前端电路中节省成本(电路面积)和功率,同时通过使用sd adc或其它adc以及低通滤波器来维持准确性。以此方式,模拟前端电路系统能够将低频率和低振幅信号转换成高分辨率数字信号,同时节省成本和功率。

34.本文中在提及使信号、状态位或类似设备呈现为其逻辑真或逻辑假状态时分别使用术语“断言”或“设置”和“取反”(或“解除断言”或“清除”)。如果逻辑真状态是逻辑电平一,那么逻辑假状态是逻辑电平零。并且如果逻辑真状态是逻辑电平零,那么逻辑假状态是逻辑电平一。

35.本文中所描述的每个信号可以设计为正逻辑或负逻辑,其中负逻辑可以用信号名称上的横线或名称后的星号(*)表示。在负逻辑信号的情况下,信号为低电平有效,其中逻辑真状态对应于逻辑电平零。在正逻辑信号的情况下,信号为高电平有效,其中逻辑真状态对应于逻辑电平一。应注意,本文中所描述的任何信号均可以设计为负逻辑信号或正逻辑信号。因此,在替代实施例中,描述为正逻辑信号的那些信号可以实施为负逻辑信号,并且

描述为负逻辑信号的那些信号可以实施为正逻辑信号。

36.由于实施本发明的设备大部分由本领域的技术人员已知的电子组件和电路构成,因此为了理解和了解本发明的基本概念并且为了不混淆或偏离本发明的教示,将不会以比上文所示出的认为必要的任何更大程度阐述电路细节。

37.此外,说明书和权利要求书中的术语“前”、“后”、“顶部”、“底部”、“上”、“下”等等,如果存在的话,是出于描述目的而使用,并且未必用于描述永久性相对位置。应理解,如此使用的术语在适当情况下可互换,使得本文中所描述的本发明的实施例例如能够以不是本文中所示出或以其它方式描述的那些朝向的其它朝向进行操作。

38.在适当时,以上实施例中的一些可以使用多种不同信息处理系统实施。举例来说,尽管图1和其论述描述示例性信息处理架构,但呈现这种示例性架构仅为了在论述本发明的各种方面时提供有用的参考。当然,出于论述的目的,所述架构的描述已被简化,并且所述架构只是可根据本发明使用的合适架构的许多不同类型中的一种。本领域的技术人员将认识到,逻辑块之间的边界仅为说明性的,并且替代实施例可合并逻辑块或电路元件,或在各种逻辑块或电路元件上施加功能性的替代分解。

39.此外,本领域的技术人员将认识到,上述操作的功能性之间的边界仅为说明性的。多个操作的功能性可以组合成单个操作,和/或单个操作的功能性可分布在另外的操作中。此外,替代实施例可包括特定操作的多个实例,并且操作的次序可以在各种其它实施例中进行更改。

40.虽然本文中参考特定实施例描述了本发明,但是可以在不脱离如所附权利要求书中所阐述的本发明的范围的情况下进行各种修改和改变。举例来说,模拟前端电路110可用于多种应用,并且不限于仅从传感器接收和处理信号。因此,说明书和图式应以说明性意义而不是以限制性意义看待,并且所有这些修改都意图包括在本发明的范围内。并不意图将本文中关于特定实施例描述的任何益处、优势或针对问题的解决方案理解为任何或所有权利要求的关键、所需或必不可少的特征或元件。

41.如本文中所使用,术语“联接”并不意图局限于直接联接或机械联接。

42.此外,如本文中所使用,术语“一”被限定为一个或多于一个。并且,权利要求书中对例如“至少一个”和“一个或多个”等引导性短语的使用不应被解释为暗示由不定冠词“一”引导的另一权利要求要素将包含此类引导的权利要求要素的任何特定权利要求限于仅包含一个此类要素的发明,即使是当同一权利要求包括引导性短语“一个或多个”或“至少一个”和例如“一”等不定冠词时也如此。上述情况同样适用于定冠词的使用。

43.除非另外说明,否则例如“第一”和“第二”等术语用于任意地区分此类术语所描述的元件。因此,这些术语未必意图指示这些元件的时间上的优先级或其它优先级。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。