技术特征:

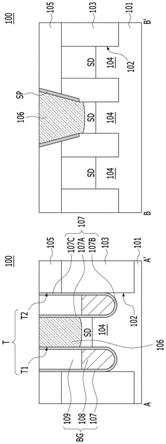

1.一种用于制造半导体器件的方法,所述方法包括:在衬底中形成接触孔;用插塞材料填充所述接触孔;通过刻蚀所述插塞材料形成接触插塞;通过刻蚀所述衬底以使其与所述接触插塞的侧壁对准而形成沟槽,所述沟槽暴露出所述接触插塞的侧壁;在所述接触插塞的暴露侧壁和所述沟槽的表面上形成栅极绝缘层;以及在所述栅极绝缘层上形成栅电极,所述栅电极部分地填充所述沟槽。2.根据权利要求1所述的方法,还包括:在用所述插塞材料填充所述接触孔之前,形成覆盖所述接触孔的侧壁的预间隔物;以及使用所述预间隔物使暴露在所述接触孔中的所述衬底进一步凹陷。3.根据权利要求2所述的方法,其中,形成所述沟槽的步骤包括:通过切割所述预间隔物而形成插塞间隔物,所述插塞间隔物覆盖所述接触插塞的未暴露侧壁。4.根据权利要求3所述的方法,其中,所述插塞间隔物还包括位于所述沟槽与所述接触插塞的底部边缘之间的底部间隔物。5.根据权利要求4所述的方法,其中,所述底部间隔物具有围绕所述接触插塞的下部外壁的形状。6.根据权利要求1所述的方法,其中,形成所述接触插塞和形成所述沟槽的步骤使用一个线型掩模来同时执行。7.根据权利要求1所述的方法,其中,所述沟槽包括一对线型沟槽,并且其中:所述一对线型沟槽与所述接触插塞的所述暴露侧壁自对准。8.根据权利要求1所述的方法,其中,形成所述接触孔的步骤包括:在所述衬底上形成层间绝缘层;在所述层间绝缘层上形成刻蚀掩模;以及使用所述刻蚀掩模来刻蚀所述层间绝缘层和所述衬底。9.根据权利要求1所述的方法,还包括:在所述衬底中形成所述接触孔之前,形成在所述衬底中限定有源区域的元件隔离层,其中所述沟槽具有与所述有源区域和所述元件隔离层交叉的线状。10.根据权利要求1所述的方法,其中,所述沟槽的底表面处于比所述接触插塞的底表面低的水平处。11.根据权利要求1所述的方法,其中,通过氧化所述接触插塞的所述暴露侧壁和所述沟槽的表面而形成所述栅极绝缘层。12.根据权利要求1所述的方法,其中,所述接触插塞的顶部部分的宽度与所述接触插塞的底部部分的宽度相同。13.根据权利要求1所述的方法,其中,所述接触插塞的顶部部分的宽度大于所述接触插塞的底部部分的宽度。14.根据权利要求1所述的方法,其中,所述接触插塞的所述暴露侧壁具有直线轮廓,并且其中,所述接触插塞的未暴露侧壁具有弯曲或弧形的轮廓。

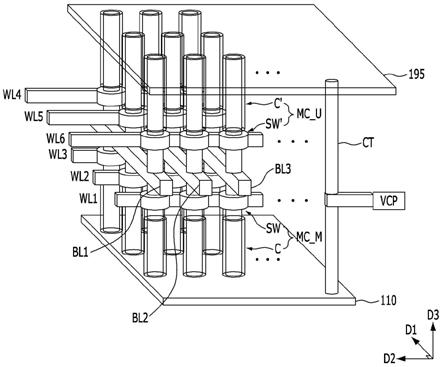

15.根据权利要求1所述的方法,其中,所述插塞材料包括多晶硅。16.根据权利要求1所述的方法,其中,所述栅电极的顶表面处于比所述接触插塞的底表面低的水平处。17.一种用于制造半导体器件的方法,所述方法包括:在衬底中形成接触孔;形成填充所述接触孔的插塞材料;通过刻蚀所述插塞材料而形成位线接触插塞;通过刻蚀所述衬底以使其与所述位线接触插塞的侧壁自对准而形成栅极沟槽,所述栅极沟槽暴露出所述位线接触插塞的侧壁;形成填充所述栅极沟槽的掩埋式栅极结构;以及在所述位线接触插塞上形成位线。18.根据权利要求17所述的方法,其中,形成所述掩埋式栅极结构的步骤包括:通过氧化所述位线接触插塞的暴露侧壁和所述栅极沟槽的表面而形成栅极绝缘层;以及在所述栅极绝缘层上形成掩埋式栅电极,使得所述掩埋式栅电极部分地填充所述栅极沟槽。19.根据权利要求17所述的方法,还包括:在形成所述插塞材料之前,形成覆盖所述接触孔的侧壁的预间隔物;以及使用所述预间隔物使暴露在所述接触孔中的所述衬底进一步凹陷,其中,形成所述栅极沟槽的步骤包括:通过切割所述预间隔物而形成插塞间隔物,所述插塞间隔物覆盖所述位线接触插塞的未暴露侧壁。20.根据权利要求17所述的方法,其中,形成所述接触孔的步骤包括:在所述衬底上形成层间绝缘层;在所述层间绝缘层上形成刻蚀掩模;以及使用所述刻蚀掩模来刻蚀所述层间绝缘层和所述衬底。21.一种半导体器件,包括:衬底;位线接触插塞,其位于所述衬底中;沟槽,其位于所述衬底中并与所述位线接触插塞的侧壁对准;栅极绝缘层,其形成在所述沟槽的表面和所述位线接触插塞的所述侧壁上;以及栅电极,其在所述栅极绝缘层上部分地填充所述沟槽,其中,所述栅极绝缘层包括第一氧化物。22.根据权利要求21所述的半导体器件,其中,所述栅极绝缘层还包括第二氧化物,以及其中,所述第二氧化物从所述第一氧化物延伸。23.根据权利要求22所述的半导体器件,其中,所述第一氧化物和所述第二氧化物包括相同的材料。24.根据权利要求22所述的半导体器件,其中,所述第一氧化物和所述第二氧化物包括

硅氧化物。25.根据权利要求21所述的半导体器件,其中,所述栅电极的顶表面处于比所述位线接触插塞的底表面低的水平处。26.根据权利要求21所述的半导体器件,还包括:栅极覆盖层,其位于所述栅电极上并填充所述沟槽,其中,所述栅极绝缘层延伸以位于所述栅极覆盖层与所述位线接触插塞之间。27.根据权利要求21所述的半导体器件,还包括:在所述衬底上的层间绝缘层,其中,所述位线接触插塞和所述沟槽穿透所述层间绝缘层并延伸到所述衬底的内部。28.根据权利要求21所述的半导体器件,还包括:储存节点接触插塞,其与所述位线接触插塞和所述栅电极间隔开并与所述衬底连接;以及插塞间隔物,其与所述沟槽不重叠并且与所述储存节点接触插塞相邻。29.根据权利要求21所述的半导体器件,还包括:底部间隔物,其位于所述沟槽与所述位线接触插塞的底部边缘之间。30.根据权利要求29所述的半导体器件,其中,所述底部间隔物具有围绕所述位线接触插塞的下部外壁的形状。31.一种半导体器件,包括:衬底,其包括有源区域;第一沟槽和第二沟槽,所述第一沟槽和所述第二沟槽彼此间隔开并在所述衬底中延伸;位线接触插塞,其位于所述第一沟槽与所述第二沟槽之间并形成在所述衬底中;第一栅极绝缘层,其形成在所述第一沟槽的表面和所述位线接触插塞的一个侧壁上;第二栅极绝缘层,其形成在所述第二沟槽的表面和所述位线接触插塞的另一侧壁上;第一栅电极,其在所述第一栅极绝缘层上部分地填充所述第一沟槽;以及第二栅电极,其在所述第二栅极绝缘层上部分地填充所述第二沟槽,其中,所述第一栅极绝缘层包括所述位线接触插塞的一个侧壁的氧化物,以及其中,所述第二栅极绝缘层包括所述位线接触插塞的另一侧壁的氧化物。32.根据权利要求31所述的半导体器件,其中,所述第一栅极绝缘层还包括所述衬底的氧化物,所述衬底的氧化物从所述位线接触插塞的所述一个侧壁的氧化物延伸,以及其中,所述第二栅极绝缘层还包括所述衬底的氧化物,所述衬底的氧化物从所述位线接触插塞的所述另一侧壁的氧化物延伸。33.根据权利要求31所述的半导体器件,其中,所述第一栅电极和所述第二栅电极的顶表面位于比所述位线接触插塞的底表面低的水平处。34.根据权利要求31所述的半导体器件,还包括:第一栅极覆盖层,其位于所述第一栅电极上并填充所述第一沟槽;以及第二栅极覆盖层,其位于所述第二栅电极上并填充所述第二沟槽,其中,所述第一栅极绝缘层延伸以位于所述第一栅极覆盖层与所述位线接触插塞之间,以及

其中,所述第二栅极绝缘层延伸以位于所述第二栅极覆盖层与所述位线接触插塞之间。35.根据权利要求31所述的半导体器件,还包括:储存节点接触插塞,其与所述位线接触插塞、所述第一栅电极和所述第二栅电极间隔开,所述储存节点接触插塞与所述衬底连接;以及插塞间隔物,其与所述第一沟槽和所述第二沟槽不重叠,所述插塞间隔物与所述储存节点接触插塞相邻。36.根据权利要求31所述的半导体器件,还包括:底部间隔物,其位于所述第一沟槽与所述位线接触插塞的底部边缘之间以及所述第二沟槽与所述位线接触插塞的所述底部边缘之间。37.根据权利要求36所述的半导体器件,其中,所述底部间隔物具有围绕所述位线接触插塞的下部外壁的形状。

技术总结

本申请公开一种半导体器件及其制造方法。一种用于制造半导体器件的方法,包括:在衬底中形成接触孔;用插塞材料填充接触孔;通过刻蚀插塞材料形成接触插塞;通过刻蚀衬底以使其与接触插塞的侧壁对准而形成沟槽,所述沟槽暴露出接触插塞的侧壁;在接触插塞的暴露侧壁和沟槽的表面上形成栅极绝缘层;以及在栅极绝缘层上形成栅电极,所述栅电极部分地填充沟槽。所述栅电极部分地填充沟槽。所述栅电极部分地填充沟槽。

技术研发人员:千宰协

受保护的技术使用者:爱思开海力士有限公司

技术研发日:2021.02.23

技术公布日:2022/2/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。