半导体装置及半导体装置的制造方法

1.[相关申请的交叉参考]

[0002]

本技术案基于2020年08月19日提出申请的现有日本专利申请案第2020-138900号的优先权利益,并主张该利益,通过引用使其全部内容包含于此。

技术领域

[0003]

本发明的实施方式涉及一种半导体装置及半导体装置的制造方法。

背景技术:

[0004]

正在开发将多个半导体芯片积层在配线衬底上来实现封装化的sip(system in package,系统级封装)。在积层多个半导体芯片时,经由daf(die attachment film,晶粒粘结膜)在下层的半导体芯片上粘接其它半导体芯片。此时,使daf熔融,将其嵌埋在下层的半导体芯片与上层的半导体芯片之间。

[0005]

然而,熔融的daf有时会从半导体芯片的端缘渗出或后缩。daf的渗出有可能在与半导体芯片相邻的焊垫上引发打线接合的连接不良。此外,daf的渗出及流失成为上层半导体芯片发生倾斜、翘曲或者破裂等的原因,导致可靠性降低。

技术实现要素:

[0006]

一实施方式提供一种能够抑制积层的多个半导体芯片间的树脂渗出及后缩的半导体装置及半导体装置的制造方法。

[0007]

实施方式的半导体装置具备:配线衬底,该配线衬底包含多个电极、第1树脂层及第2树脂层,所述多个电极设置在第1面,所述第1树脂层在所述第1面设置在所述多个电极周围,所述第2树脂层设置在所述第1树脂层;第1半导体芯片,与所述多个电极中的第1电极连接;第2半导体芯片,设置在所述第1半导体芯片上方,比该第1半导体芯片大,形成有第3电极;金属线,连接所述多个电极中的第2电极与所述多个第3电极;以及第3树脂层,设置在所述第1半导体芯片与所述第2半导体芯片之间以及所述第2树脂层与所述第2半导体芯片之间,覆盖所述第1半导体芯片。

[0008]

根据所述构成,能够提供一种能够抑制积层的多个半导体芯片间的树脂渗出及后缩的半导体装置及半导体装置的制造方法。

附图说明

[0009]

图1是表示第1实施方式的半导体装置的构成例的剖视图。

[0010]

图2是表示第1实施方式的半导体装置的构成的一例的概略俯视图。

[0011]

图3是表示安装在配线衬底上的半导体元件的构成例的剖视图。

[0012]

图4是表示第1实施方式的半导体装置的制造方法的一例的剖视图。

[0013]

图5是表示继图4之后的半导体装置的制造方法的一例的剖视图。

[0014]

图6是表示继图5之后的半导体装置的制造方法的一例的剖视图。

[0015]

图7是表示继图6之后的半导体装置的制造方法的一例的剖视图。

[0016]

图8是表示第2实施方式的半导体装置的构成例的剖视图。

[0017]

图9是表示第3实施方式的半导体装置的构成例的剖视图。

[0018]

图10是表示第4实施方式的半导体装置的构成例的俯视图。

[0019]

图11是表示第5实施方式的半导体装置的构成例的俯视图。

[0020]

图12是表示第6实施方式的半导体装置的构成例的剖视图。

[0021]

图13是表示第7实施方式的半导体装置的构成例的剖视图。

[0022]

图14是表示第8实施方式的半导体装置的构成例的剖视图。

具体实施方式

[0023]

参考附图对实施方式进行说明。本发明不限于下述实施方式。在实施方式中,“上方向”或“下方向”意指相对方向,“上方向”设为垂直于具有半导体芯片的配线衬底的表面的方向。因此,术语“上方向”或“下方向”有时不同于基于重力加速度方向的上方向或下方向。在本说明书和附图中,对和所述附图中描述的元件相同的元件标注相同的符号,并适当地省略其详细说明。

[0024]

本实施方式的半导体装置具备配线衬底,该配线衬底包含:多个电极,设置在第1面上;第1树脂层,在第1面上设置在多个电极周围;以及第2树脂层,设置在第1树脂层上。第1半导体芯片与多个电极中的第1电极连接。第2半导体芯片设置在第1半导体芯片上方,比该第1半导体芯片大,经由金属线与多个电极中的第2电极连接。第3树脂层设置在第1半导体芯片与第2半导体芯片之间以及第2树脂层与第2半导体芯片之间,被覆第1半导体芯片。

[0025]

(第1实施方式)

[0026]

图1是表示第1实施方式的半导体装置1的构成例的剖视图。本实施方式的半导体装置1例如是nand(not and,与非)型闪速存储器。半导体装置1具备配线衬底10、树脂层(ncp(non-conductive paste,非导电性胶))20、控制器芯片30、树脂层(daf(die attach film,晶粒粘结膜))40、nand型存储器芯片(以下称存储器芯片)50、粘接层60、金属线70、密封树脂80及金属凸块90。另外,本实施方式不限定于nand型闪速存储器,可以应用于所有包含积层的多个半导体芯片的半导体封装。

[0027]

配线衬底10具备:绝缘衬底11、配线12、通孔13、电极14、15、阻焊剂sr1、sr2。绝缘衬底11例如使用玻璃环氧树脂等绝缘材料。配线12设置在绝缘衬底11的正面、背面或内部,与电极14、15电连接。通孔13以贯通绝缘衬底11内的方式设置,使配线12间电连接。

[0028]

电极14、15设置在配线衬底10的正面f1上。作为第1电极的电极14在配线衬底10的正面f1与控制器芯片30的金属凸块31连接。作为第2电极的电极15在配线衬底10的正面f1经由金属线70与存储器芯片50的焊垫51连接。配线12、电极14、15例如使用铜等低电阻金属。虽未图示,也可以使用镍、焊料等在配线衬底10的背面f2侧设置金属凸块。金属凸块经由配线12与电极14、15电连接。另外,配线12及绝缘衬底11也可以是3层以上的多层配线构造。

[0029]

作为第1树脂层的阻焊剂sr1在配线衬底10的正面f1上设置在电极14、15周围。阻焊剂sr1可以设置在电极14、15以外的正面f1及整个背面f2。此外,阻焊剂sr1也可以被覆电极14、15的一部分,但不设置在金属凸块31或金属线70的连接区域,使金属凸块31或金属线

70的连接区域露出。此外,阻焊剂sr1在背面f2上使配线12的一部分连接区域露出。在该露出的配线12的连接区域设置着金属凸块90。另外,在本实施方式中,阻焊剂sr1仅为第1树脂层的一例,第1树脂层并不限定于此。

[0030]

作为第2树脂层的阻焊剂sr2设置在阻焊剂sr1上,从配线衬底10的正面f1的上方俯视时,以包围控制器芯片30的方式设置在控制器芯片30周围。阻焊剂sr2在所述俯视时设置在阻焊剂sr1的内侧,阻焊剂sr1、sr2积层为两层。因此,在阻焊剂sr2的端部存在阻焊剂sr1、sr2的阶差st。阻焊剂sr1、sr2可以是相同材料,也可以是互不相同的材料。此外,阻焊剂sr2的高度可以比控制器芯片30的上表面低,但也可以与之相同或是比它高。另外,在本实施方式中,设置着两层阻焊剂sr1、sr2,但也可以设置三层以上的阻焊剂。此外,在本实施方式中,阻焊剂sr2仅为第2树脂层的一例,第2树脂层并不限定于此。

[0031]

在作为第1半导体芯片的控制器芯片30的对向于配线衬底10的面,设置着金属凸块31。金属凸块31与配线衬底10的电极14连接。控制器芯片30以倒装芯片的方式连接在配线衬底10上。控制器芯片30的衬底(未图示)经薄化,在设置着金属凸块31的面具有未图示的半导体元件。半导体元件经由金属凸块31与配线衬底10的配线12电连接。

[0032]

树脂层(ncp)20填充于配线衬底10与控制器芯片30之间,被覆保护电极14与金属凸块31的连接部分。此外,树脂层20也填充于控制器芯片30与阻焊剂sr1、sr2、树脂层40之间,保护控制器芯片30。树脂层20与阻焊剂sr1、sr2的内壁面接触。并且,树脂层20也可以到达阻焊剂sr2的上表面。树脂层20是非导电性树脂材料(ncp),例如可以是将环氧树脂、丙烯酸树脂、二氧化硅等混合而成的糊。

[0033]

树脂层40设置在控制器芯片30与存储器芯片50之间以及阻焊剂sr2与存储器芯片50之间,被覆控制器芯片30。树脂层40例如使用晶粒粘结膜等绝缘性树脂。

[0034]

若使阻焊剂sr2的厚度变厚,使阻焊剂sr2的上表面变高,则阻焊剂sr2的上表面的高度会和控制器芯片30的上表面相同,或者也可以比它高。

[0035]

作为第2半导体芯片的存储器芯片50设置在控制器芯片30的上方。存储器芯片50通过树脂层(粘接层)40粘接在控制器芯片30及阻焊剂sr2上。存储器芯片50例如在正面具有三维配置了多个存储单元的立体型存储单元阵列。在存储器芯片50的背面事先贴附着树脂层40,在晶粒粘结步骤中,将存储器芯片50按压于配线衬底10并加热。由此,树脂层40将控制器芯片30及树脂层20嵌埋,存储器芯片50被粘接到控制器芯片30上。从正面f1的上方俯视时,存储器芯片50比控制器芯片30大。因此,贴附在存储器芯片50的背面的树脂层40也比控制器芯片30大,在晶粒粘结步骤中能够被覆控制器芯片30的整个正面。

[0036]

多个存储器芯片50也可以积层在控制器芯片30上。在图1中,积层着4个存储器芯片50,但存储器芯片50的积层数并无特别限定。在多个存储器芯片50的背面事先贴附着粘接层60。将存储器芯片50积层在下层的存储器芯片50上,利用粘接层60将双方相互粘接。

[0037]

金属线70将存储器芯片50的焊垫51与配线衬底10的任一电极15之间电连接。由此,存储器芯片50的半导体元件经由金属线70与配线衬底10的配线12连接。密封树脂80被覆保护控制器芯片30、存储器芯片50、金属线70等配线衬底10上的整体构造。

[0038]

金属凸块90在背面f2与配线12的一部分电连接。金属凸块90例如使用焊料等低电阻金属。

[0039]

图2是表示第1实施方式的半导体装置1的构成的一例的概略俯视图。图2表示从配

线衬底10的正面f1的上方观察的阻焊剂sr1、sr2、控制器芯片30、存储器芯片50等的平面布局。

[0040]

阻焊剂sr1大致被覆配线衬底10的除了电极(焊垫)14、15以外的正面f1整体。阻焊剂sr1不设置在电极14、15的形成区域,具有开口op1、op2。图2的开口op3表示阻焊剂sr2的开口部分,阻焊剂sr1显露在开口op3的内侧。在开口op3的区域内,阻焊剂sr1的开口op1几乎都隐藏在树脂层20之下。此外,在图2中未图示,在开口op1中,阻焊剂sr1使电极14露出。在开口op2中,阻焊剂sr1使电极15露出。

[0041]

阻焊剂sr2设置在阻焊剂sr1上,以从正面f1的上方观察时不堵塞阻焊剂sr1的开口op1、op2的方式设置在阻焊剂sr1的范围内。在阻焊剂sr2之下配置着阻焊剂sr1,阻焊剂sr1、sr2是两层重叠。

[0042]

从正面f1的上方俯视时,阻焊剂sr2设置在控制器芯片30周围,包围控制器芯片30。因此,阻焊剂sr2形成为在中心部具有孔(开口部op3)的大致四边形的框状。阻焊剂sr2也可以是大致多边形的框状、大致圆形的环状、大致椭圆形的环状。也就是说,阻焊剂sr2具有外缘e2_out及内缘e2_in,外缘e2_out及内缘e2_in的形状可以是大致四边形、大致多边形、大致圆形、大致椭圆形中的任一形状。并且,外缘e2_out及内缘e2_in的形状可以是互为相似形,也可以是互不相同的形状。阻焊剂sr2设置在阻焊剂sr1上,因此,在所述俯视下,外缘e2_out及内缘e2_in重叠于阻焊剂sr1上。

[0043]

阻焊剂sr2的外缘e2_out位于比控制器芯片30的外缘e30及存储器芯片50的外缘e50靠外侧之处,且不重叠于电极15的形成区域(开口op2)。因此,阻焊剂sr2的外缘e2_out位于阻焊剂sr1的开口op2与存储器芯片50的外缘e50之间。

[0044]

此外,阻焊剂sr2的内缘e2_in位于比存储器芯片50的外缘e50靠内侧之处,位于比控制器芯片30的外缘e30靠外侧之处。此外,阻焊剂sr2的内缘e2_in(开口op3的端缘)不重叠于电极14的形成区域(开口op1)。因此,阻焊剂sr2的内缘e2_in(开口op3的端缘)位于阻焊剂sr1的开口op1或控制器芯片30的外缘e30与存储器芯片50的外缘e50之间。

[0045]

从正面f1的上方俯视时,控制器芯片30以倒装芯片的方式连接在电极14,因此,重叠于电极14的形成区域(开口op1),配置在开口op3的内侧。也就是说,在所述俯视下,控制器芯片30的外缘e30位于开口op3的内侧。另外,控制器芯片30的外缘e30可以位于开口op1的内侧,也可以位于外侧。也就是说,控制器芯片30可以比阻焊剂sr1的开口op1小而位于其内侧,也可以比开口op1大。

[0046]

存储器芯片50比控制器芯片30大,在所述俯视下,存储器芯片50的外缘e50位于控制器芯片30的外缘e30的外侧。此外,为了能够通过金属线70连接存储器芯片50的焊垫51与电极15,存储器芯片50的外缘e50未到达开口op2。因此,存储器芯片50的外缘e50位于电极15的形成区域(开口op2)与控制器芯片30之间。从正面f1的上方观察时,存储器芯片50重叠于控制器芯片30、开口op1、阻焊剂sr2,配置在阻焊剂sr2的外缘e2_out的内侧。

[0047]

图2所示的存储器芯片50表示再下层的存储器芯片50的外缘e50。直接被覆控制器芯片30及阻焊剂sr2的图1的树脂层40若不发生渗出或后缩,则大小和存储器芯片50大致相同。因此,从正面f1的上方观察时,存储器芯片50的外缘e50与树脂层40的外缘大致一致而重叠。在这种情况下,从正面f1的上方观察时,阻焊剂sr2的外缘e2_out位于树脂层40的外缘靠外侧之处。

[0048]

树脂层(ncp)20在控制器芯片30与配线衬底10之间被覆保护电极14。从正面f1的上方观察时,树脂层20的外缘e20重叠于阻焊剂sr1、sr2中的任一者。

[0049]

如图1所示,树脂层(daf)40贴附在存储器芯片50的背面,当将存储器芯片50积层在控制器芯片30上时,树脂层40被覆控制器芯片30及树脂层20整体。

[0050]

此处,如图1所示,多个阻焊剂sr1、sr2积层在控制器芯片30周围,选择性地形成得较厚。因此,在积层存储器芯片50时,在树脂层40之下,多个阻焊剂sr1、sr2实质上较厚。由此,存储器芯片50与阻焊剂sr2之间的树脂层40的厚度t40变得较薄。

[0051]

如果不设置阻焊剂sr2,那么存储器芯片50与阻焊剂sr1之间的树脂层40的厚度变厚。在这种情况下,需要使事先贴附在存储器芯片50的树脂层40的厚度变厚,于是当将存储器芯片50贴附在控制器芯片30上时,树脂层40从存储器芯片50的外缘e50渗出或后缩的可能性变高。当由于树脂层40的渗出而导致树脂层40到达电极15时,则有可能导致无法打线接合于电极15。此外,存储器芯片50变得容易相对于配线衬底10的正面f1或控制器芯片30的上表面倾斜。这会引起存储器芯片50的翘曲或者破裂等,使半导体装置1的可靠性降低。

[0052]

此外,为了使树脂层40的厚度变薄,如果仅仅是使阻焊剂sr1变厚,则开口op1、op2以外的配线衬底10的正面f1上的阻焊剂的厚度会整体变厚。在这种情况下,开口op2的外缘的阻焊剂sr1变厚,有可能导致金属线70与阻焊剂sr1接触。此外,如果使阻焊剂sr1整体变厚,则如图3所示,控制器芯片30及存储器芯片50以外的其它半导体元件(电阻、电容器等)se之下的阻焊剂sr1的厚度tsr1也变厚。图3是表示安装在配线衬底10上的半导体元件se的构成例的剖视图。半导体元件se和控制器芯片30及存储器芯片50一起安装在同一配线衬底10上。在这种情况下,在将半导体元件se安装在配线衬底10上时,阻焊剂sr1干扰半导体元件se的连接,难以将半导体元件se连接在配线衬底10。

[0053]

并且,由于配线衬底10的正面f1的阻焊剂sr1和其背面f2的阻焊剂(未图示)的厚度不同,施加于配线衬底10的应力失衡,有可能导致配线衬底10翘曲。

[0054]

与之相对,在本实施方式的半导体装置1中,阻焊剂sr2和阻焊剂sr1分开,积层在阻焊剂sr1上。因此,阻焊剂sr2选择性地设置在贴附存储器芯片50的控制器芯片30周围,不设置在除此以外的阻焊剂sr1上。也就是说,阻焊剂sr2仅设置在设置树脂层40的区域。

[0055]

由此,能够使树脂层40的厚度与阻焊剂sr2的厚度相应地变薄。通过使树脂层40变薄,在将存储器芯片50贴附在控制器芯片30上时,树脂层40不易从存储器芯片50的外缘e50渗出,也不易后缩。因此,不会阻碍对电极15进行打线接合。此外,存储器芯片50不易相对于配线衬底10的正面f1或控制器芯片30的上表面倾斜,变得大致平坦。这有助于提升半导体装置1的可靠性。进而,树脂层40的嵌埋性提高,能够抑制空隙残留在树脂层40与阻焊剂sr2、树脂层20、控制器芯片30之间。

[0056]

此外,阻焊剂sr2位于阻焊剂sr1的范围内,在开口op2具有图1的阶差st。因此,阻焊剂sr1、sr2在开口op2的外缘呈阶梯状逐渐变厚,能够抑制金属线70干扰阻焊剂sr1、sr2。

[0057]

此外,阻焊剂sr2设置在控制器芯片30周围,但未设置在除此以外的阻焊剂sr1上。进而,阻焊剂sr1本身的厚度(图3的tsr1)并不那么厚,因此能够抑制在将其它半导体元件se安装在配线衬底10上时,半导体元件se干扰阻焊剂sr1。

[0058]

此外,阻焊剂sr2在配线衬底10的正面f1上设置在最小必要的范围内即可。因此,正面f1的阻焊剂sr1与其背面f2的阻焊剂的厚度差异不大,能够抑制配线衬底10翘曲。

[0059]

其次,对本实施方式的半导体装置1的制造方法进行说明。

[0060]

图4~图7是表示第1实施方式的半导体装置1的制造方法的一例的剖视图。

[0061]

首先,如图4所示,向配线衬底10的控制器芯片30的搭载位置供给树脂层20的材料(ncp)。配线衬底10具备绝缘衬底11、配线12、电极14、15、阻焊剂sr1、sr2。配线12设置在绝缘衬底11的正面及内部。电极14、15在正面f1上从绝缘衬底11、阻焊剂sr1、sr2露出。

[0062]

阻焊剂sr1设置在电极14、15周围,在电极14、15的形成区域具有开口op1、op2。阻焊剂sr2在阻焊剂sr1上设置在阻焊剂sr1的范围内。阻焊剂sr2以包围控制器芯片30的搭载位置周围的方式设置。因此,阻焊剂sr1、sr2在开口op1、op2的端部具有阶差st。也就是说,阻焊剂sr1、sr2的内缘及外缘具有阶差st。由此,树脂层20的糊状材料不易从开口op1溢出。此外,接合于电极15的金属线70不易干扰阻焊剂sr1、sr2。

[0063]

树脂层20的材料(ncp)是非导电性糊状树脂材料。在将控制器芯片30以倒装芯片的方式连接在配线衬底10时,树脂层20填充于控制器芯片30与配线衬底10之间,将它们连接。另外,树脂层20的材料不仅可以是ncp,也可以是ncf(non-conductive film,非导电性膜)、cuf(capillary under fill,毛细效应底部填充)。

[0064]

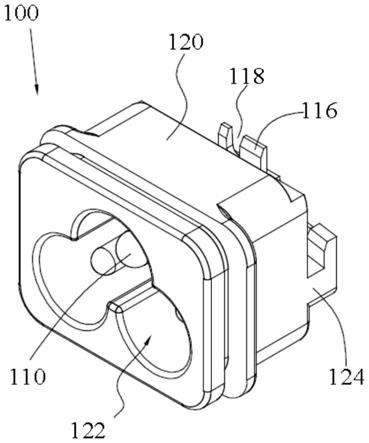

其次,如图5所示,压接装置100隔着fab(film assist bonding,膜辅助接合)膜95吸附控制器芯片30,将控制器芯片30配置在配线衬底10上。此时,压接装置100以使控制器芯片30的金属凸块31与配线衬底10的电极14对应的方式,在配线衬底10上积层控制器芯片30。

[0065]

压接装置100具有与未图示的真空泵连接的抽吸孔105,通过该抽吸孔105吸附控制器芯片30。压接装置100的吸附面将控制器芯片30压接于配线衬底10上,且使树脂层20的上表面变得大致平坦。为了不使树脂层20的材料附着于压接装置100,在压接装置100与控制器芯片30之间介置有作为树脂膜的fab膜95。

[0066]

压接装置100在将控制器芯片30积层在配线衬底10上之后,对配线衬底10及控制器芯片30施加压力并进行加热。由此,将控制器芯片30的金属凸块31连接(熔接)于配线衬底10的电极14。在将控制器芯片30积层在配线衬底10上时,树脂层20的材料填充于控制器芯片30与配线衬底10之间。树脂层20的材料也可以顺着控制器芯片30的侧面向上攀爬一些。

[0067]

其次,如图6所示,将背面贴附着树脂层40的存储器芯片50贴附在控制器芯片30及阻焊剂sr2上。此时,一面进行加热,一面将存储器芯片50朝控制器芯片30按压,用树脂层40被覆控制器芯片30及树脂层20。进而,对树脂层40进行加热、加压,消除空隙,使其硬化。像这样,将存储器芯片50经由树脂层40粘接在控制器芯片30的上方。

[0068]

从正面f1的上方俯视时,正如参照图2所说明的那样。在该俯视下,存储器芯片50及树脂层40比控制器芯片30大,且比阻焊剂sr2小。此外,阻焊剂sr2以包围控制器芯片30周围的方式配置。因此,树脂层40被覆控制器芯片30,并粘接在阻焊剂sr2上。由此,即使树脂层40的厚度比较薄,也能够嵌埋而被覆存储器芯片50及树脂层20。

[0069]

其次,在存储器芯片50上进一步积层其它存储器芯片50。此时,在存储器芯片50间设置粘接层60,多个存储器芯片50通过粘接层60相互粘接。

[0070]

其后,将其它半导体元件连接在配线衬底10上。通过金属线70将焊垫51与电极15之间接合。并且,通过密封树脂80将存储器芯片50及金属线70密封。在第2面f2的配线(或焊

垫)12上形成金属凸块90。由此,完成图1所示的半导体装置1的封装。

[0071]

根据本实施方式,通过将阻焊剂sr1、sr2重叠两层,被树脂层40嵌埋的控制器芯片30及树脂层20的厚度减少。由此,抑制树脂层40的渗出及后缩,并且使树脂层40能够充分嵌埋存储器芯片50及树脂层20。此外,通过将阻焊剂sr2重叠于阻焊剂sr1上,能够使树脂层40的厚度变薄。由此,能够相对于控制器芯片30或配线衬底10的正面f1大致平行地配置存储器芯片50。

[0072]

此外,阻焊剂sr2位于阻焊剂sr1的范围内,在开口op2具有阶差st。因此,阻焊剂sr1、sr2在开口op2的外缘呈阶梯状逐渐变厚,能够抑制金属线70干扰阻焊剂sr1、sr2。

[0073]

此外,阻焊剂sr2设置在控制器芯片30周围,但未设置在除此以外的阻焊剂sr1上。因此,在将其它半导体元件se安装在配线衬底10上时,能够抑制阻焊剂sr1干扰其它半导体元件se。

[0074]

此外,阻焊剂sr2在配线衬底10的正面f1上设置在最小必要的范围内。因此,正面f1的阻焊剂sr1与其背面f2的阻焊剂的厚度差异不大,能够抑制配线衬底10翘曲。

[0075]

(第2实施方式)

[0076]

图8是表示第2实施方式的半导体装置1的构成例的剖视图。在第2实施方式中,存储器芯片50及树脂层40向控制器芯片30的单侧错开。伴随于此,树脂层20及控制器芯片30的一部分从树脂层40露出。像这样,从正面f1的上方俯视时,存储器芯片50及树脂层40也可以向控制器芯片30的单侧错开。第2实施方式的其它构成可与第1实施方式的对应构成相同。因此,第2实施方式能够获得和第1实施方式相同的效果。

[0077]

(第3实施方式)

[0078]

图9是表示第3实施方式的半导体装置1的构成例的剖视图。在第3实施方式中,从正面f1的上方俯视时,阻焊剂sr2的内缘e2_in位于和阻焊剂sr1的内缘e2_in大致相同的位置而重叠。第3实施方式的其它构成可与第1实施方式的对应构成相同。因此,第3实施方式能够获得和第1实施方式相同的效果。

[0079]

(第4实施方式)

[0080]

图10是表示第4实施方式的半导体装置1的构成例的俯视图。在第4实施方式中,从正面f1的上方俯视时,阻焊剂sr2被分割成多个部分。阻焊剂sr2的部分各自为大致四边形,与框状的阻焊剂sr2相比,更加容易进行加工及配置。另一方面,担心树脂层40从阻焊剂sr2的间隙渗出。然而,通过以使间隙充分变窄的方式配置阻焊剂sr2,能够抑制树脂层40的渗出。第4实施方式的其它构成可与第1实施方式的对应构成相同。因此,第4实施方式能够获得和第1实施方式相同的效果。

[0081]

(第5实施方式)

[0082]

图11是表示第5实施方式的半导体装置1的构成例的俯视图。在第5实施方式中,从正面f1的上方俯视时,阻焊剂sr2的内缘e2_in被加工成与树脂层20从控制器芯片30的外缘e30渗出的形状相符。例如,当树脂层20在控制器芯片30的外缘e30周围呈大致圆形或大致椭圆形渗出时,沿树脂层20将阻焊剂sr2的内缘e2_in加工成大致圆形或大致椭圆形。由此,使树脂层20容易停留在阻焊剂sr2的内侧,能够抑制它在阻焊剂sr2上过量溢出。第5实施方式的其它构成可与第1实施方式的对应构成相同。因此,第5实施方式能够获得和第1实施方式相同的效果。

[0083]

(第6实施方式)

[0084]

图12是表示第6实施方式的半导体装置1的构成例的剖视图。在第6实施方式中,阻焊剂sr1、sr2的外侧面f3倾斜。例如,阻焊剂sr1、sr2的外侧面f3以从阻焊剂sr2的上表面朝向阻焊剂sr1的底面变宽的方式(以具有下摆的方式)相对于正面f1从大致垂直方向倾斜。另外,阻焊剂sr1、sr2的内壁面也可以倾斜。

[0085]

由此,阻焊剂sr1、sr2和金属线70更不容易相互干扰。第6实施方式的其它构成可与第1实施方式的对应构成相同。因此,第6实施方式能够获得和第1实施方式相同的效果。

[0086]

(第7实施方式)

[0087]

图13是表示第7实施方式的半导体装置1的构成例的剖视图。在第7实施方式中,阻焊剂sr1的内侧端部进入控制器芯片30之下。从正面f1的上方俯视时,阻焊剂sr1的内侧面(内缘)f4比控制器芯片30的侧面(外缘)f30靠近控制器芯片30的中心。也就是说,在所述俯视下,阻焊剂sr1的整个内周位于比最下层的控制器芯片30的整个外周靠内侧之处,阻焊剂sr1的内缘与控制器芯片30重叠。

[0088]

根据这样的构成,阻焊剂sr1与控制器芯片30之间的间隔变窄。因此,如图5所示,在将控制器芯片30粘接在配线衬底10上时,树脂层20在阻焊剂sr1与控制器芯片30之间被压缩。由此,能够抑制空隙在树脂层20产生。

[0089]

第7实施方式的其它构成可与第1实施方式相同。因此,第7实施方式能够获得和第1实施方式相同的效果。

[0090]

(第8实施方式)

[0091]

图14是表示第8实施方式的半导体装置1的构成例的剖视图。在第8实施方式中,阻焊剂sr1、sr2形成为一体。例如,阻焊剂sr1形成得较厚,省略了阻焊剂sr2。使用光刻技术及蚀刻技术,将阻焊剂sr1加工成具有阶差,使阻焊剂sr1的内侧面f4进入控制器芯片30之下。由此,省略阻焊剂sr2并获得和第7实施方式相同的构成。根据这样的构成,第8实施方式能够获得和第7实施方式相同的效果。

[0092]

对本发明的某些实施方式进行了说明,但这些实施方式仅作为例子呈现,并不意图限定发明的范围。实际上,本说明书中所描述的这些新颖的实施方式和方法能以各种其它形式实现,而且,在不脱离本发明的主旨的情况下,能够以本说明书中所描述的实施方式和方法的形式进行各种省略、置换、变更。这些实施方式及其变化旨在包含于本发明的范围及主旨中,也包含于随附的权利要求书中及其均等范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。