半导体存储装置的动作条件的调整方法

1.[相关申请]

[0002]

本技术案享有以日本专利申请案第2020-139918号(申请日:2020年8月21日)为基础申请案的优先权。本技术案通过参照所述基础申请案而包含基础申请案的全部内容。

技术领域

[0003]

本实施方式涉及一种半导体存储装置的动作条件的调整方法。

背景技术:

[0004]

已知有一种半导体存储装置,具备:衬底;多个第1导电层,排列在与衬底的表面交叉的第1方向;多个第1半导体层,在第1方向上延伸,与多个第1导电层对向;第2半导体层,在第1方向上与衬底隔开,或者是衬底的一部分,连接在多个第1半导体层的第1方向的一端部;及电荷累积层,设置在多个第1导电层与多个第1半导体层之间。

技术实现要素:

[0005]

本发明所要解决的问题在于提供一种能够实现高速动作的半导体存储装置的动作条件的调整方法。

[0006]

实施方式的半导体存储装置的动作条件的调整方法与半导体存储装置相关,所述半导体存储装置具备:衬底;多个第1导电层,排列在与衬底的表面交叉的第1方向;多个第1半导体层,在第1方向上延伸,与多个第1导电层对向;第2半导体层,在第1方向上与衬底隔开,或者是衬底的一部分,连接在多个第1半导体层的第1方向的一端部;及电荷累积层,设置在多个第1导电层与多个第1半导体层之间。所述半导体存储装置中,在编程动作的特定时序,对作为多个第1导电层中的一个的第2导电层供给编程电压或小于编程电压的写入路径电压。在所述调整方法中执行第1动作及第2动作,所述第1动作是对第2导电层供给写入路径电压,并对作为多个第1导电层中的一个的第3导电层供给编程电压,所述第2动作是对第2导电层供给小于写入路径电压的验证电压,并对第3导电层供给小于编程电压的电压。

附图说明

[0007]

图1是表示第1实施方式的半导体存储装置的构成的示意性框图。

[0008]

图2是表示所述半导体存储装置的一部分构成的示意性电路图。

[0009]

图3是表示所述半导体存储装置的一部分构成的示意性立体图。

[0010]

图4是表示所述半导体存储装置的一部分构成的示意性剖视图。

[0011]

图5是图4的a所示部分的示意性放大图。

[0012]

图6是用来针对记录4比特数据的存储单元mc的阈值电压进行说明的示意性柱状图。

[0013]

图7是用来针对读出动作进行说明的示意性剖视图。

[0014]

图8是用来针对写入顺序进行说明的示意性流程图。

[0015]

图9是用来针对编程动作进行说明的示意性剖视图。

[0016]

图10是用来针对验证动作进行说明的示意性剖视图。

[0017]

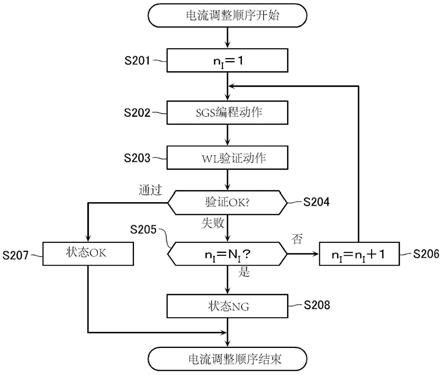

图11是用来针对第1实施方式的电流调整顺序进行说明的示意性流程图。

[0018]

图12是用来针对电流调整顺序进行说明的示意性波形图。

[0019]

图13是用来针对sgs编程动作进行说明的示意性剖视图。

[0020]

图14是用来针对sgs编程动作进行说明的示意性剖视图。

[0021]

图15是用来针对wl验证动作进行说明的示意性剖视图。

[0022]

图16是用来针对第2实施方式的电流调整顺序进行说明的示意性波形图。

[0023]

图17是用来针对sgs编程动作进行说明的示意性剖视图。

[0024]

图18是用来针对sgs编程动作进行说明的示意性剖视图。

[0025]

图19是用来针对第3实施方式的电流调整顺序进行说明的示意性波形图。

[0026]

图20是用来针对sgs编程动作进行说明的示意性剖视图。

[0027]

图21是用来针对sgs编程动作进行说明的示意性剖视图。

[0028]

图22是用来针对第4实施方式的电流调整顺序进行说明的示意性流程图。

[0029]

图23是用来针对电流调整顺序进行说明的示意性波形图。

[0030]

图24是用来针对tcwl编程动作进行说明的示意性剖视图。

[0031]

图25是用来针对wl验证动作进行说明的示意性剖视图。

[0032]

图26是表示第5实施方式的半导体存储装置的一部分构成的示意性剖视图。

具体实施方式

[0033]

接下来,参照附图,详细说明实施方式的半导体存储装置。另外,以下的实施方式只不过是一个示例,并非为了限定本发明而示出。此外,以下的附图是示意图,有时为方便说明而将一部分构成等省略。此外,有时对多个实施方式共通的部分标注相同符号并省略说明。

[0034]

此外,本说明书中称为“半导体存储装置”的情况下,有时意指存储器裸片,有时意指存储器芯片、存储卡、ssd(solid state drive:固态硬盘)等包含控制器裸片的存储器系统。进而,有时意指智能手机、平板终端、个人计算机等包含主计算机的构成。

[0035]

此外,本说明书中称为“控制电路”的情况下,有时意指设置在存储器裸片的序列发生器等外围电路,有时意指连接在存储器裸片的控制器裸片或控制器芯片,有时意指包含这两个的构成。

[0036]

此外,本说明书中,称为第1构成“电连接”在第2构成的情况下,第1构成可直接连接在第2构成,第1构成也可经由配线、半导体部件或晶体管等连接在第2构成。例如,在将3个晶体管串联连接的情况下,尽管第2个晶体管为断开(off)状态,第1个晶体管也“电连接”在第3个晶体管。

[0037]

此外,本说明书中,称为第1构成在第2构成及第3构成的“中间连接”的情况下,有时意指第1构成、第2构成及第3构成串联连接,且第2构成经由第1构成连接在第3构成。

[0038]

此外,本说明书中,称为使电路等2条配线等“导通”的情况下,例如有时意指所述电路等包含晶体管等,所述晶体管等设置在2条配线之间的电流路径,所述晶体管等成为接通(on)状态。

[0039]

此外,本说明书中,将相对于衬底的上表面平行的特定方向称为x方向,将相对于衬底的上表面平行,与x方向垂直的方向称为y方向,将相对于衬底的上表面垂直的方向称为z方向。

[0040]

此外,本说明书中,有时将沿特定面的方向称为第1方向,将沿所述特定的面与第1方向交叉的方向称为第2方向,将与所述特定的面交叉的方向称为第3方向。这些第1方向、第2方向及第3方向可与x方向、y方向及z方向的任一个对应,也可不对应。

[0041]

此外,本说明书中,“上”或“下”等表现以衬底为基准。例如,将沿所述z方向远离衬底的方向称为上,将沿z方向靠近衬底的方向称为下。此外,对于某构成称为下表面或下端的情况下,意指所述构成的衬底侧的面或端部,称为上表面或上端的情况下,意指所述构成的与衬底为相反侧的面或端部。此外,将与x方向或y方向交叉的面称为侧面等。

[0042]

[第1实施方式]

[0043]

[半导体存储装置的电路构成]

[0044]

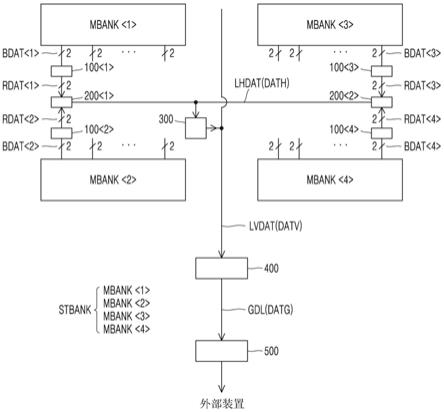

图1是表示第1实施方式的半导体存储装置的构成的示意性框图。图2是半导体存储装置的一部分构成的示意性电路图。

[0045]

另外,图1中图示多个控制端子等。所述多个控制端子有时表示为对应于高有效信号(正逻辑信号)的控制端子,有时表示为对应于低有效信号(负逻辑信号)的控制端子,有时表示为对应于高有效信号及低有效信号的两个的控制端子。图1中,对应于低有效信号的控制端子的符号包含顶划线(上线)。本说明书中,对应于低有效信号的控制端子的符号包含斜线(“/”)。另外,图1的记载为例示,具体方面可适当调整。例如,也可将一部分或全部高有效信号设为低有效信号,或将一部分或全部低有效信号设为高有效信号。

[0046]

如图1所示,半导体存储装置具备存储数据的存储单元阵列mca,及连接在存储单元阵列mca的外围电路pc。外围电路pc具备电压产生电路vg、行解码器rd、感测放大器模块sam、序列发生器sqc。此外,外围电路pc具备高速缓冲存储器cm、地址寄存器adr、命令寄存器cmr、及状态寄存器str。此外,外围电路pc具备输入输出控制电路i/o与逻辑电路ctr。

[0047]

[存储单元阵列mca的电路构成]

[0048]

如图2所示,存储单元阵列mca具备多个存储器块blk。所述多个存储器块blk分别具备多个串单元su。所述多个串单元su分别具备多个存储器串ms。所述多个存储器串ms的一端分别经由位线bl连接在外围电路pc。此外,所述多个存储器串ms的另一端分别经由共用的源极线sl连接在外围电路pc。

[0049]

存储器串ms具备:串联连接在位线bl及源极线sl间的漏极侧选择晶体管std、位线bl侧的多个虚拟存储单元dmc、多个存储单元mc、源极线sl侧的多个虚拟存储单元dmc、源极侧选择晶体管sts及源极侧选择晶体管stsb。以下,有时将漏极侧选择晶体管std、源极侧选择晶体管sts及源极侧选择晶体管stsb简称为选择晶体管(std、sts、stsb)。

[0050]

存储单元mc是场效晶体管,其具备作为通道区域发挥功能的半导体层、包含电荷累积膜的栅极绝缘膜、及栅极电极。存储单元mc的阈值电压根据电荷累积膜中的电荷量而变化。存储单元mc存储1比特或多比特的数据。另外,在对应于1个存储器串ms的多个存储单元mc的栅极电极上,分别连接有字线wl。这些字线wl分别共用连接在1个存储器块blk中的所有存储器串ms。

[0051]

虚拟存储单元dmc具备与存储单元mc相同的结构。但,虚拟存储单元dmc不存储数

据。另外,在对应于1个存储器串ms的多个虚拟存储单元dmc的栅极电极,分别连接虚设字线dwl。这些虚设字线dwl分别共用连接在1个存储器块blk中的所有存储器串ms。

[0052]

选择晶体管(std、sts、stsb)是场效晶体管,其具备作为通道区域发挥功能的半导体层、栅极绝缘膜及栅极电极。在选择晶体管(std、sts、stsb)的栅极电极上,分别连接选择栅极线(sgd、sgs、sgsb)。漏极侧选择栅极线sgd与串单元su对应设置,共用连接在1个串单元su中的所有存储器串ms。源极侧选择栅极线sgs及源极侧选择栅极线sgsb共用连接在1个存储器块blk中的所有存储器串ms。

[0053]

[电压产生电路vg的电路构成]

[0054]

如图2所示,电压产生电路vg(图1)例如连接在多条电压供给线31。电压产生电路vg例如包含调整器等降压电路及电荷泵电路32等升压电路。这些降压电路及升压电路分别连接在供给电源电压v

cc

及接地电压v

ss

的电压供给线(图1)。电压产生电路vg例如遵循来自序列发生器sqc的控制信号,在对存储单元阵列mca进行读出动作、写入动作及抹除动作时,产生施加在位线bl、源极线sl、字线wl、虚设字线dwl及选择栅极线(sgd、sgs、sgsb)的多种动作电压,并同时输出到多条电压供给线31。遵循来自序列发生器sqc的控制信号,适当调整从电压供给线31输出的动作电压。

[0055]

[行解码器rd的电路构成]

[0056]

如图2所示,行解码器rd(图1)例如具备:将地址数据d

add

解码的地址解码器22、根据地址解码器22的输出信号将动作电压传输到存储单元阵列mca的块选择电路23及电压选择电路24。

[0057]

地址解码器22具备多条块选择线blksel及多条电压选择线33。地址解码器22例如遵循来自序列发生器sqc的控制信号,依序参照地址寄存器adr(图1)的行地址ra,将所述行地址ra解码,将对应于行地址ra的特定的块选择晶体管35及电压选择晶体管37设为接通(on)状态,将除此之外的块选择晶体管35及电压选择晶体管37设为断开(off)状态。例如,将特定的块选择线blksel及电压选择线33的电压设为“h”状态,将除此之外的电压设为“l”状态。另外,使用p通道型晶体管而非n通道型的情况下,对这些配线施加反向电压。

[0058]

另外,图示例中,在地址解码器22,对1个存储器块blk各设有1条块选择线blksel。然而,所述构成可适当变更。例如,也可2个以上存储器块blk各具备1条块选择线blksel。

[0059]

块选择电路23具备对应于存储器块blk的多个块选择部34。所述多个块选择部34分别具备对应于字线wl、虚设字线dwl及选择栅极线(sgd、sgs、sgsb)的多个块选择晶体管35。块选择晶体管35例如为场效耐压晶体管。块选择晶体管35的漏极电极分别电连接在对应的字线wl、虚设字线dwl或选择栅极线(sgd、sgs、sgsb)。源极电极分别经由配线cg及电压选择电路24,电连接在电压供给线31。栅极电极共用连接在对应的块选择线blksel。

[0060]

另外,块选择电路23还具备未图示的多个晶体管。所述多个晶体管是连接在选择栅极线(sgd、sgs、sgsb)及供给接地电压v

ss

的电压供给线间的场效耐压晶体管。所述多个晶体管对非选择存储器块blk所含的选择栅极线(sgd、sgs、sgsb)供给接地电压v

ss

。另外,非选择存储器块blk所含的多条字线wl成为浮动状态。

[0061]

电压选择电路24具备对应于字线wl、虚设字线dwl及选择栅极线(sgd、sgs、sgsb)的多个电压选择部36。所述多个电压选择部36分别具备多个电压选择晶体管37。电压选择晶体管37例如为场效耐压晶体管。电压选择晶体管37的漏极端子分别经由配线cg及块选择

电路23,电连接在对应的字线wl、虚设字线dwl或选择栅极线(sgd、sgs、sgsb)。源极端子分别电连接在对应的电压供给线31。栅极电极分别连接在对应的电压选择线33。

[0062]

另外,图示例中,示出配线cg经由一个电压选择晶体管37连接在电压供给线31的例子。然而,这种构成只不过是例示,具体构成可适当调整。例如,配线cg也可经由2个以上电压选择晶体管37连接在电压供给线31。

[0063]

[感测放大器模块sam的电路构成]

[0064]

感测放大器模块sam例如具备对应于多条位线bl的多个感测放大器单元。感测放大器单元分别具备:电连接在位线bl的感测节点、电连接在感测节点的感测晶体管、电连接在感测晶体管的数据配线、及电连接在数据配线的多个锁存电路。此外,感测放大器单元分别具备:电连接在位线bl的电压传输电路,及电连接在电压传输电路的控制用锁存电路。感测节点在读出动作等的特定时序与位线bl导通。感测晶体管具备电连接在感测节点的栅极电极。感测晶体管对应于感测节点的电压成为接通(on)状态或断开(off)状态。数据配线对应于感测晶体管是接通(on)状态还是断开(off)状态而充电或放电。多个锁存电路及控制用锁存电路对应于数据配线的电压,将“1”或“0”的资料锁存。电压传输电压对应于锁存到控制用锁存电路的数据,使位线bl与2条电压供给线的任一条导通。

[0065]

[高速缓冲存储器cm的电路构成]

[0066]

高速缓冲存储器cm(图1)具备经由配线dbus连接在感测放大器模块sam内的多个锁存电路的多个锁存电路。将所述多个锁存电路所含的数据dat依序传输到感测放大器模块sam或输入输出控制电路i/o。

[0067]

此外,在高速缓冲存储器cm,连接有未图示的解码电路及开关电路。解码电路将保持在地址寄存器adr(图1)的行地址ca解码。开关电路根据解码电路的输出信号,使对应于行地址ca的锁存电路与总线db(图1)导通。

[0068]

[序列发生器sqc的电路构成]

[0069]

序列发生器sqc(图1)遵循保持在命令寄存器cmr的命令数据d

cmd

,将内部控制信号输出到行解码器rd、感测放大器模块sam及电压产生电路vg。此外,序列发生器sqc将适当表示自身状态的状态数据d

st

输出到状态寄存器str。

[0070]

此外,序列发生器sqc产生就绪/忙碌信号,输出到端子ry/(/by)。端子ry/(/by)为“l”状态期间(忙碌期间),基本禁止向半导体存储装置存取。此外,端子ry/(/by)为“h”状态期间(就绪期间),允许向半导体存储装置存取。

[0071]

[输入输出控制电路i/o的电路构成]

[0072]

输入输出控制电路i/o具备:数据信号输入输出端子dq0~dq7、触发信号输入输出端子dqs、/dqs、连接在数据信号输入输出端子dq0~dq7的比较器等的输入电路及ocd(off chip driver:芯片外驱动器)电路等输出电路。此外,输入输出电路i/o具备连接在这些输入电路及输出电路的位移寄存器,与缓冲电路。输入电路、输出电路、位移寄存器及缓冲电路分别连接在供给电源电压v

ccq

及接地电压v

ss

的端子。将经由数据信号输入输出端子dq0~dq7输入的数据对应于来自逻辑电路ctr的内部控制信号,从缓冲电路输出到高速缓冲存储器cm、地址寄存器adr或命令寄存器cmr。此外,将经由数据信号输入输出端子dq0~dq7输出的数据对应于来自逻辑电路ctr的内部控制信号,从高速缓冲存储器cm或状态寄存器str输入到缓冲电路。

[0073]

[逻辑电路ctr的电路构成]

[0074]

逻辑电路ctr(图1)经由外部控制端子/cen、cle、ale、/we、re、/re,从控制器接收外部控制信号,与此相应将内部控制信号输出到输入输出控制电路i/o。

[0075]

[半导体存储装置的结构]

[0076]

图3是表示半导体存储装置的一部分构成的示意性立体图。图4是表示半导体存储装置的一部分构成的示意性剖视图。图5是图4的a所示部分的示意性放大图。

[0077]

如图3所示,半导体存储装置例如具备:半导体衬底100、设置在半导体衬底100上的晶体管层l

tr

、设置在晶体管层l

tr

的上部的配线层d0~d2、设置在配线层d0~d2的上方的存储单元阵列层l

mca

、及设置在存储单元阵列层l

mca

的上方的多个配线层。

[0078]

[半导体衬底100的结构]

[0079]

半导体衬底100例如为包含含有硼(b)等p型杂质的p型硅(si)的半导体衬底。例如,在半导体衬底100的表面,设有包含磷(p)等n型杂质的n型阱区域、包含硼(b)等p型杂质的p型阱区域、未设置n型阱区域及p型阱区域的半导体衬底区域、及绝缘区域sti。

[0080]

[晶体管层l

tr

的结构]

[0081]

例如如图3所示,在半导体衬底100的上表面,介隔绝缘层设有多个电极gc。此外,半导体衬底100的各区域及多个电极gc分别连接在接点cs。

[0082]

半导体衬底100的n型阱区域、p型阱区域及半导体衬底分别作为构成外围电路pc(图1、图2)的多个晶体管tr的通道区域、及多个电容器的一电极等发挥功能。

[0083]

多个电极gc分别作为构成外围电路pc的多个晶体管tr的栅极电极,及多个电容器的另一电极等发挥功能。

[0084]

接点cs在z方向上延伸,在下端连接在半导体衬底100或电极gc的上表面。在接点cs与半导体衬底100的连接部分,设有包含n型杂质或p型杂质的杂质区域。接点cs例如也可包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。

[0085]

[配线层d0~d2的结构]

[0086]

例如如图3所示,配线层d0~d2所含的多条配线电连接在存储单元阵列mca中的构成及外围电路pc中的构成的至少一个。

[0087]

配线层d0~d2所含的多条配线例如也可包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。

[0088]

[存储单元阵列层l

mca

的结构]

[0089]

例如如图3所示,在存储单元阵列层l

mca

,设有存储器块blk,及氧化硅(sio2)等块间绝缘层st。存储器块blk具备:排列在z方向的多个导电层110、在z方向上延伸的多个半导体层120、及分别设置在多个导电层110及多个半导体层120间的多个栅极绝缘膜130。

[0090]

导电层110是在x方向上延伸的大致板状的导电层。导电层110也可包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。此外,导电层110也可包含例如含有磷(p)或硼(b)等杂质的多晶硅等。在排列在z方向的多个导电层110间,设有氧化硅(sio2)等绝缘层101。

[0091]

在导电层110的下方,设有导电层111。导电层111也可包含例如含有磷(p)或硼(b)等杂质的多晶硅等。此外,在导电层111及导电层110间,设有氧化硅(sio2)等绝缘层101。

[0092]

在导电层111的下方,设有导电层112。导电层112具备:连接在半导体层120的下端

的半导体层113,及连接在半导体层113的下表面的导电层114。半导体层113也可包含例如含有磷(p)等n型杂质的多晶硅等。导电层114也可包含例如钨(w)等金属、硅化钨等导电层或其它导电层。此外,在导电层112及导电层111间,设有氧化硅(sio2)等绝缘层101。

[0093]

导电层112作为源极线sl(图2)发挥功能。源极线sl对多个存储器块blk共用设置。

[0094]

导电层111作为源极侧选择栅极线sgsb(图2),及连接在源极侧选择栅极线sgsb的多个源极侧选择晶体管stsb的栅极电极发挥功能。导电层111在每个存储器块blk电独立。

[0095]

此外,多个导电层110中,位于最下层的多个导电层110作为源极侧选择栅极线sgs(图2)及连接在源极侧选择栅极线sgs的多个源极侧晶体管sts的栅极电极发挥功能。所述多个导电层110在每个存储器块blk电独立。

[0096]

此外,位于上方的多个导电层110作为虚设字线dwl及连接在虚设字线dwl的多个虚拟存储单元dmc的栅极电极发挥功能。所述多个导电层110分别在每个存储器块blk电独立。

[0097]

此外,位于上方的多个导电层110作为字线wl(图2)及连接在字线wl的多个存储单元mc(图2)的栅极电极发挥功能。所述多个导电层110分别在每个存储器块blk电独立。

[0098]

此外,位于上方的多个导电层110作为虚设字线dwl及连接在虚设字线dwl的多个虚拟存储单元dmc的栅极电极发挥功能。所述多个导电层110分别在每个存储器块blk电独立。

[0099]

此外,位于上方的一个或多个导电层110作为漏极侧选择栅极线sgd及连接在漏极侧选择栅极线sgd的多个漏极侧选择晶体管std(图2)的栅极电极发挥功能。所述多个导电层110介隔串单元间绝缘层she分断成多个部分,分别在每个串单元su电独立。

[0100]

在所述多个导电层110的x方向的端部,设有在z方向上延伸的接点cc。所述多个导电层110经由多个接点cc连接在外围电路pc。

[0101]

半导体层120在x方向及y方向以特定的图案排列。半导体层120作为一个存储器串ms(图2)所含的多个存储单元mc、多个虚拟存储单元dmc及选择晶体管(std、sts、stsb)的通道区域发挥功能。半导体层120例如为多晶硅(si)等半导体层。如图4所示,半导体层120例如具有大致有底圆筒状的形状,在中心部分设有氧化硅等绝缘层125。此外,半导体层120的外周面分别介隔栅极绝缘膜130由导电层110包围,与导电层110对向。半导体层120的外周面也由导电层111包围,介隔栅极绝缘膜130与导电层111对向。另外,图4的例子中,半导体层120的上端部及下端部由虚线表示。

[0102]

在半导体层120的上端部,设有包含磷(p)等n型杂质的杂质区域121。图4的例子中,半导体层120的上端部与杂质区域121的边界线由虚线表示。杂质区域121经由接点ch及接点vy(图3),连接在沿y方向上延伸的导电层150。导电层150作为位线bl发挥功能。导电层150例如也可包含氮化钛(tin)等障壁导电膜及铜(cu)等金属膜的积层膜等。

[0103]

如图4所示,在半导体层120的下端部,例如设有包含磷(p)等n型杂质的杂质区域122。图4的例子中,半导体层120的下端部与杂质区域122的边界线由虚线表示。杂质区域122连接在所述导电层112的半导体层113。半导体层120中,位于杂质区域122的正上的部分作为源极侧选择晶体管stsb的通道区域发挥功能。杂质区域122的外周面由导电层111包围,介隔栅极绝缘膜130与导电层111对向。

[0104]

栅极绝缘膜130具有覆盖半导体层120的外周面的大致有底圆筒状的形状。栅极绝

缘膜130例如如图5所示,具备:积层在半导体层120及导电层110间的通道绝缘膜131、电荷累积膜132及块绝缘膜133。通道绝缘膜131及块绝缘膜133例如为氧化硅(sio2)等绝缘膜。电荷累积膜132例如为氮化硅(si3n4)等可累积电荷的膜。通道绝缘膜131、电荷累积膜132及块绝缘膜133具有大致圆筒状的形状,沿半导体层120的外周面在z方向上延伸。

[0105]

另外,图5表示栅极绝缘膜130具备氮化硅等电荷累积膜132的例子。然而,栅极绝缘膜130也可具备例如包含n型或p型杂质的多晶硅等浮动栅极。

[0106]

[存储单元mc的阈值电压]

[0107]

接着,参照图6,针对存储单元mc的阈值电压进行说明。

[0108]

如上所述,存储单元阵列mca具备多个存储单元mc。对所述多个存储单元mc进行写入顺序的情况下,将这些存储单元mc的阈值电压控制为多种状态。

[0109]

图6是用来针对记录4比特数据的存储单元mc的阈值电压进行说明的柱状图。横轴表示字线wl的电压,纵轴表示存储单元mc的数量。

[0110]

图6的例子中,将存储单元mc的阈值电压控制为16种状态。例如,控制为s1状态的存储单元mc的阈值电压大于图6的读出电压v

cg1r

及验证电压v

vfy1

,小于读出电压v

cg2r

及验证电压v

vfy2

。此外,所有存储单元mc的阈值电压小于读出路径电压v

read

。

[0111]

例如,er状态与最低阈值电压(抹除状态的存储单元mc的阈值电压)对应。也可在对应于er状态的存储单元mc,例如分配数据“1111”。

[0112]

此外,s1状态与高于对应于所述er状态的阈值电压的阈值电压对应。也可在对应于s1状态的存储单元mc,例如分配数据“1011”。

[0113]

此外,s2状态与高于对应于所述s1状态的阈值电压的阈值电压对应。也可在对应于s2状态的存储单元mc,例如分配数据“0011”。

[0114]

以下同样,对应于图中的s3状态~s15状态的阈值电压分别高于对应于s2状态~s14状态的阈值电压。也可在对应于这些分布的存储单元mc,例如分配所述的“1111”、“1011”、“0011”以外的4比特数据。

[0115]

另外,记录在存储单元mc的数据的比特数、状态数、数据对各状态的分配等可适当变更。

[0116]

例如,在er状态及s1状态~s7状态的所有第4位分配有“1”,在s8状态~s15状态的所有第4位分配有“0”的情况下,读出第4位的数据时,对字线wl供给读出电压v

cg8r

。

[0117]

此外,例如在er状态及s1状态~s3状态的所有第3位分配有“1”,在s4状态~s11状态的所有第3位分配有“0”,在s12状态~s15状态的所有第3位分配有“1”的情况下,读出第3位的数据时,对字线wl供给读出电压v

cg4r

、v

cg12r

。

[0118]

[读出动作]

[0119]

接着,参照图7等,针对本实施方式的半导体存储装置的读出动作进行说明。图7是用来针对读出动作进行说明的示意性剖视图。

[0120]

另外,以下的说明中,有时将成为动作对象的字线wl称为选择字线wls,将除此之外的字线wl称为非选择字线wlu。此外,以下的说明中,针对对串单元su所含的多个存储单元mc中,连接在选择字线wls的存储单元mc(以下,有时称为“选择存储单元mc”。)执行读出动作的例子进行说明。此外,以下的说明中,有时将这种包含多个选择存储单元mc的构成称为选择页面pg。

[0121]

对存储单元mc读出时,例如进行位线bl等的充电。也就是说,对位线bl及感测放大器模块sam(图1、图2)中的感测节点供给电压v

dd

,将这些充电。此外,例如对源极线sl(图2)供给电压v

src

,开始所述充电。电压v

src

例如具有与接地电压v

ss

相同程度的大小。电压v

src

例如大于接地电压v

ss

,小于电压v

dd

。

[0122]

此外,使选择页面pg所含的多个选择存储单元mc与位线bl及源极线sl导通。例如,对选择栅极线(sgd、sgs、sgsb)供给电压v

sg

,将选择晶体管(std、sts、stsb)设为接通(on)状态。此外,对非选择字线wlu供给读出路径电压v

read

,将连接在非选择字线wlu的所有存储单元mc设为接通(on)状态。此外,对虚设字线dwl供给电压v

read'

,将所有虚拟存储单元dmc设为接通(on)状态。另外,电压v

read

'大于接地电压v

ss

,小于读出路径电压v

read

。

[0123]

此外,对选择字线wls供给读出电压v

cgsr

(图6的读出电压v

cg1r

~v

cg15r

的任一个)。由此,一般的存储单元mc成为接通(on)状态,其它存储单元mc成为断开(off)状态。

[0124]

此外,利用感测放大器模块sam(图1、图2),检测选择存储单元mc的接通(on)状态/断开(off)状态。例如,使感测放大器模块sam中的感测节点与位线bl导通,维持或放电感测节点的电荷,将感测晶体管设为接通(on)状态或断开(off)状态。此外,根据感测晶体管的状态将资料配线的电荷充电或放电,通过连接在数据配线的多个锁存电路的任一个,锁存对应于所述配线的电压的数据。由此,示出选择存储单元mc的状态的资料锁存到锁存电路。

[0125]

以下,视需要依序切换供给到选择字线wls的读出电压v

cgsr

,检测选择存储单元mc的接通(on)状态/断开(off)状态。接着,在检测出的数据间进行and、or等运算处理,算出存储在选择存储单元mc的数据。之后,将算出的数据输出到高速缓冲存储器cm。之后,例如将锁存到高速缓冲存储器cm的数据经由总线db(图1)及输入输出控制电路i/o(图1)输出。

[0126]

[写入顺序]

[0127]

接着,参照图8~图10,针对半导体存储装置的写入顺序进行说明。图8是用来针对写入顺序进行说明的示意性流程图。图9是用来针对写入顺序所含的编程动作进行说明的示意性剖视图。图10是用来针对写入顺序所含的验证动作进行说明的示意性剖视图。

[0128]

步骤s101(图8)中,将环路次数nw设定为1。环路次数nw记录在寄存器等。

[0129]

步骤s102中,进行编程动作。

[0130]

编程动作时,例如对连接在多个选择存储单元mc中进行阈值电压调整的存储单元mc(以下,有时称为“写入存储单元mc”。)的位线bl供给电压v

src

,对连接在多个选择存储单元mc中不进行阈值电压调整的存储单元mc(以下,有时称为“禁止存储单元mc”。)的位线bl供给电压v

dd

。例如,将“l”锁存到连接在感测放大器模块sam中的电压传输电路的所述控制用锁存电路中,对应于写入存储单元mc的控制用锁存电路,将“h”锁存到对应于禁止存储单元mc的控制用锁存电路。此外,经由所述2条电压供给线,对写入存储单元mc与禁止存储单元mc供给不同电压。

[0131]

此外,如图9所示,使写入存储单元mc选择性与位线bl导通。例如,对漏极侧选择栅极线sgd供给电压v

sgd

。电压v

sgd

例如小于图7的电压v

sg

。由此,对应于供给电压v

src

的位线bl的漏极侧选择晶体管std成为接通(on)状态,对应于供给电压v

dd

的位线bl的漏极侧选择晶体管std成为断开(off)状态。此外,对非选择字线wlu供给写入路径电压v

pass

。写入路径电压v

pass

例如大于图6的读出路径电压v

read

及图7的电压v

sg

。也就是说,读出路径电压v

read

及电压v

sg

小于写入路径电压v

pass

。此外,对漏极侧选择晶体管std侧的虚设字线dwl供给电压vpass

'。电压v

pass

'大于电压v

sgd

,小于写入路径电压v

pass

。此外,对源极侧选择栅极线sgs2、sgs1、sgs0、sgsb供给接地电压v

ss

。此外,对源极侧选择晶体管sts侧的虚设字线dwl供给电压v

pass”。电压v

pass”大于接地电压v

ss

,小于写入路径电压v

pass

。

[0132]

此外,如图9所示,对选择字线wls供给编程电压v

pgm

。编程电压v

pgm

大于写入路径电压v

pass

及电压v

sg

。也就是说,写入路径电压v

pass

及电压v

sg

小于编程电压v

pgm

。由此,将电子累积在写入存储单元mc的电荷累积膜132(图5),写入存储单元mc的阈值电压增大。

[0133]

步骤s103(图8)中,进行验证动作。

[0134]

验证动作时,例如进行位线bl等的充电。此外,使选择存储单元mc选择性与位线bl及源极线sl导通。此外,如图10所示,对选择字线wls供给验证电压v

vfys

(图6的验证电压v

vfy1

~v

vfy15

的任一个),检测选择存储单元mc的接通(on)状态/断开(off)状态。此外,视需要依序切换供给到选择字线wls的验证电压v

vfys

,检测选择存储单元mc的接通(on)状态/断开(off)状态。

[0135]

另外,验证动作中,也可省略针对禁止存储单元mc的接通(on)状态/断开(off)状态检测。这种情况下,也可例如在验证动作时,将“h”锁存到连接在感测放大器模块sam中的电压传输电路的所述控制用锁存电路中,连接在写入存储单元mc的锁存电路,将“l”锁存到连接在禁止存储单元mc的锁存电路。

[0136]

步骤s104(图8)中,判定验证动作的结果。例如,示出存储单元mc的状态的资料中包含一定以上“l”的情况等下,判定为验证失败(fail),进入步骤s105。另一方面,表示存储单元mc的状态的资料中不包含一定以上“l”的情况等下,判定为验证通过(pass),进入步骤s107。

[0137]

步骤s105中,判定环路次数nw是否达到特定的次数nw。未达到的情况下,进入步骤s106。达到的情况下,进入步骤s108。

[0138]

步骤s106中,对环路次数nw加上1,进入步骤s102。此外,步骤s106中,例如对编程电压v

pgm

加上特定的电压δv。

[0139]

步骤s107中,在状态寄存器str(图1),存储写入顺序正常结束的主旨的状态数据d

st

,结束写入顺序。

[0140]

步骤s108中,在状态寄存器str(图1),存储写入顺序未正常结束的主旨的状态数据d

st

,结束写入顺序。

[0141]

[流动在存储单元mc的电流的不均]

[0142]

如参照图4所说明,半导体层113包含磷(p)等n型杂质。此外,在半导体层120的下端部,设有包含磷(p)等n型杂质的杂质区域122。这种结构中,例如有时会导致在制造步骤中,半导体层113及半导体层120的杂质区域122所含的n型杂质因热等而扩散、会导致杂质区域122的范围不均。此外,有时对应于杂质区域122的范围不均,在半导体层120间,电流的大小产生不均。

[0143]

此处,所述写入顺序中,基于流动在半导体层120的电流,判定存储单元mc的阈值电压是否达到目标值。因此,在半导体层120间,电流的大小产生不均的情况下,判定对应于电流不易流动的半导体层120的存储单元mc是在较早阶段,阈值电压达到目标值的存储单元mc。另一方面,判定对应于电流易流动的半导体层120的存储单元mc是在较晚阶段,阈值电压达到目标值的存储单元mc。因此,有时会导致在这些之间,适于控制阈值电压的条件不

同、导致写入顺序(图8)中的环路次数nw增大。

[0144]

因此,本实施方式中,为抑制这种因半导体层120引起的电流不均,对应于电流的不均将电荷累积在电荷累积膜132的一部分。例如,针对电流易流动的半导体层120,将电荷累积在对应于所述半导体层120的电荷累积膜132的、对应于作为源极侧选择栅极线sgs发挥功能的多个导电层110的部分中的电荷累积膜132。由此,调整半导体层120间的电流的易流动度。

[0145]

根据这种方法,可抑制半导体层120间的电流不均。由此,能够降低写入顺序(图8)中的环路次数nw,实现半导体存储装置的高速动作。此外,有时根据情况,在写入顺序中,可省略验证动作。这种情况下,可实现半导体存储装置更高速的动作。

[0146]

[电流调整顺序]

[0147]

接着,参照图11~图14,针对本实施方式的半导体存储装置的电流调整顺序进行说明。图11是用来针对电流调整顺序进行说明的示意性流程图。图12是用来针对本实施方式的电流调整顺序进行说明的示意性波形图。图13及图14是用来针对电流调整顺序所含的sgs编程动作进行说明的示意性剖视图。图15是用来针对电流调整顺序所含的wl验证动作进行说明的示意性剖视图。

[0148]

另外,以下的说明中,针对排列在z方向的多个导电层110中,位于最下方的3个导电层110作为源极侧选择栅极线sgs发挥功能的例子进行说明。此外,以下的说明中,将对应于位于最下方的导电层110的构成称为源极侧选择栅极线sgs0,将对应于位于从下起第2个导电层110的构成称为源极侧选择栅极线sgs1,将对应于位于从下起第3个导电层110的构成称为源极侧选择栅极线sgs2。

[0149]

步骤s201(图11)中,将环路次数ni设定为1。环路次数ni记录在寄存器等。

[0150]

步骤s202(图11)中,进行sgs编程动作。

[0151]

例如,图12的例子中,在时序t101,开始sgs编程动作。

[0152]

此外,在时序t102,对字线wl供给写入路径电压v

pass

。此外,对漏极侧选择栅极线sgd供给接地电压v

ss

。此外,对源极侧选择栅极线sgs2、sgs1、sgs0供给写入路径电压v

pass

。此外,对源极侧选择栅极线sgsb供给接地电压v

ss

。此外,如图13所示,对源极线sl供给电压v

src

。此外,对源极线sl侧的虚设字线dwl供给写入脉冲电压v

pass

。此外,对位线bl侧的虚设字线dwl供给电压v

pass

'。

[0153]

此处,图13的例子中,源极侧选择晶体管stsb的一部分成为接通(on)状态,形成在与其对应的一部分半导体层120的外周面的电子的通道与导电层112导通。此外,源极侧选择晶体管stsb的一部分成为断开(off)状态,形成在与其对应的一部分半导体层120的外周面的电子的通道与导电层112电分离。这种现象例如因所述杂质区域122的范围不均而产生。

[0154]

此外,在时序t103,如图12所示,对源极侧选择栅极线sgs0、sgs1供给编程电压v

pgm

。

[0155]

此处,如图14所示,形成在对应于接通(on)状态的源极侧选择晶体管stsb的半导体层120的外周面的电子的通道与源极线sl导通,供给电压v

src

。因此,在所述通道与源极侧选择栅极线sgs0、sgs1间,产生编程电压v

pgm

程度大小的电位差。由此,将电子累积在源极侧选择晶体管sts的栅极绝缘膜所含的电荷累积膜132,这些源极侧选择晶体管sts的阈值电

压增大。

[0156]

另一方面,如图14所示,形成在对应于断开(off)状态的源极侧选择晶体管stsb的半导体层120的外周面的电子的通道与源极线sl电分离,成为浮动状态。此外,所述通道的电压通过与字线wl的电容耦合,成为写入路径电压v

pass

程度的大小。因此,在所述通道与源极侧选择栅极线sgs0、sgs1间,产生编程电压v

pgm

与写入路径电压v

pass

的差量程度大小的电位差。这种源极侧选择晶体管sts的阈值电压不增大。

[0157]

此外,在时序t104,如图12所示,对源极侧选择栅极线sgs0、sgs1供给写入路径电压v

pass

。

[0158]

此外,在时序t105,对字线wl及选择栅极线(sgd、sgs2、sgs1、sgs0、sgsb)供给接地电压v

ss

。

[0159]

步骤s203(图11)中,进行wl验证动作。

[0160]

例如,图12的例子中,在时序t111,开始wl验证动作。

[0161]

此外,在时序t111,对一条或多条字线wl供给电压v

vfyw

。此外,对其它字线wl供给读出路径电压v

read

。此外,对漏极侧选择栅极线sgd及源极侧选择栅极线sgs2、sgs1、sgs0、sgsb供给电压v

sg

。此外,如图15所示,对位线bl供给电压v

dd

。此外,对源极线sl供给电压v

src

。电压v

src

例如小于电压v

vfyw

。此外,对源极线sl侧及位线bl侧的虚设字线dwl供给电压v

read'

。

[0162]

此外,从时序t111到时序t112,检测形成在半导体层120的外周面的电子的通道所流动的电流是否为特定大小以下,取得表示电流大小的数据。其通过例如与检测存储单元mc的接通(on)状态/断开(off)状态的方法相同的方法进行。

[0163]

此外,在时序t112,如图12所示,对字线wl及选择栅极线(sgd、sgs2、sgs1、sgs、sgsb)供给接地电压v

ss

。

[0164]

步骤s204(图11)中,判定wl验证动作的结果。例如,表示电流大小的数据中包含一定以上“l”的情况等下,判定wl验证失败(fail),进入步骤s205。另一方面,表示电流大小的数据中不包含一定以上“l”的情况等下,判定wl验证通过(pass),进入步骤s207。

[0165]

步骤s205中,判定环路次数ni是否达到特定的次数ni。未达到的情况下,进入步骤s206。达到的情况下,进入步骤s208。

[0166]

步骤s206中,对环路次数ni加上1,进入步骤s202。例如,图12的例子中,在时序t121~时序t132,执行对应于时序t101~时序t112的动作。此外,步骤s206中,例如对编程电压v

pgm

加上特定的电压δv。因此,如图12所示,在时序t123供给到源极侧选择栅极线sgs1、sgs0的编程电压v

pgm

,大于在时序t103供给到源极侧选择栅极线sgs1、sgs0的编程电压v

pgm

。

[0167]

步骤s207中,在状态寄存器str(图1),存储电流调整顺序正常结束的主旨的状态数据d

st

,结束电流调整顺序。

[0168]

步骤s208中,在状态寄存器str(图1),存储电流调整顺序未正常结束的主旨的状态数据d

st

,结束电流调整顺序。

[0169]

[第2实施方式]

[0170]

接着,参照图16~图18,针对第2实施方式的半导体存储装置的电流调整顺序进行说明。图16是用来针对电流调整顺序进行说明的示意性波形图。图17及图18是用来针对电

流调整顺序所含的sgs编程动作进行说明的示意性剖视图。

[0171]

第2实施方式的电流调整顺序基本上与第1实施方式的电流调整顺序同样地执行。但,第2实施方式的电流调整顺序的一部分与第1实施方式的电流调整顺序不同。

[0172]

也就是说,第1实施方式的电流调整顺序中,对应于杂质区域122的范围的不均,选择成为sgs编程动作的对象的源极侧选择晶体管sts。

[0173]

另一方面,第2实施方式的电压调整顺序中,通过位线bl的电压调整,选择成为sgs编程动作的对象的源极侧选择晶体管sts。此外,此时,由于不论杂质区域122的范围不均,都将源极侧选择晶体管stsb设为断开(off)状态,所以对源极侧选择栅极线sgsb供给具有负极性的电压v

off

。

[0174]

以下,针对第2实施方式的电流调整顺序更具体说明。

[0175]

例如,图16的例子中,在时序t201,开始sgs编程动作。此处,本实施方式的sgs编程动作时,例如对连接在多个源极侧选择晶体管sts中进行阈值电压调整的源极侧选择晶体管sts(以下,有时称为“写入选择晶体管”。)的位线bl供给电压v

src

,对连接在多个源极侧选择晶体管sts中不进行阈值电压调整的源极侧选择晶体管sts(以下,有时称为“禁止选择晶体管”。)的位线bl供给电压v

dd

。例如,将“l”锁存到连接在感测放大器模块sam中的电压传输电路的所述控制用锁存电路中,对应于写入选择晶体管的控制用锁存电路,将“h”锁存到对应于禁止选择晶体管的控制用锁存电路。此外,经由所述2条电压供给线,对写入选择晶体管与禁止选择晶体管供给不同电压。

[0176]

此外,在时序t202,对字线wl供给写入路径电压v

pass

。此外,对漏极侧选择栅极线sgd供给电压v

sgd

。此外,对源极侧选择栅极线sgs2、sgs1、sgs0供给写入路径电压v

pass

。此外,对源极侧选择栅极线sgsb供给小于接地电压v

ss

的具有负极性的电压v

off

。此外,如图17所示,对位线bl侧的虚设字线dwl供给电压v

pass

'。此外,对源极线sl侧的虚设字线dwl供给写入路径电压v

pass

。

[0177]

此外,在时序t203,如图16及图18所示,对源极侧选择栅极线sgs0、sgs1供给编程电压v

pgm

。由此,将电子累积在写入选择晶体管的电荷累积膜132,写入选择晶体管的阈值电压增大。

[0178]

此外,在时序t204,如图16所示,对源极侧选择栅极线sgs0、sgs1供给写入路径电压v

pass

。

[0179]

此外,在时序t205,对字线wl及选择栅极线(sgd、sgs2、sgs1、sgs0、sgsb)供给接地电压v

ss

。

[0180]

此外,在时序t211~时序t212,执行wl验证动作。wl验证动作与第1实施方式的wl验证动作同样地执行。但,第2实施方式中,对应于wl验证动作中取得的表示电流大小的数据,将一部分写入选择晶体管更新为禁止选择晶体管。

[0181]

其它动作与第1实施方式的电流调整顺序中的动作同样地执行。

[0182]

[第3实施方式]

[0183]

接着,参照图19~图21,针对第3实施方式的半导体存储装置的电流调整顺序进行说明。图19是用来针对电流调整顺序进行说明的示意性波形图。图20及图21是用来针对电流调整顺序所含的sgs编程动作进行说明的示意性剖视图。

[0184]

第3实施方式的电流调整顺序基本上与第2实施方式的电流调整顺序同样地执行。

但,第3实施方式的电流调整顺序的一部分与第2实施方式的电流调整顺序不同。

[0185]

也就是说,第2实施方式的电流调整顺序中,例如如参照图16及图18所说明,在将电压v

src

供给到对应于所有写入选择晶体管的位线bl的状态下,在sgs编程动作的时序t203等,与源极侧选择栅极线sgs0、sgs1同时供给编程电压v

pgm

。

[0186]

另一方面,实施方式3的电流调整顺序中,例如如图19及图20所示,在将电压v

src

供给到对应于所有写入选择晶体管的位线bl的状态下,在时序t313,对源极侧选择栅极线sgs0供给编程电压v

pgm

。此外,例如如图19及图21所示,在将电压v

src

供给到对应于一部分写入选择晶体管的位线bl的状态下,在时序t323,对源极侧选择栅极线sgs1供给编程电压v

pgm

。

[0187]

以下,针对第3实施方式的电流调整顺序更具体地进行说明。

[0188]

例如,图19的例子中,在时序t301~时序t302,执行wl验证动作。wl验证动作与第2实施方式的wl验证动作同样地执行。但,第3实施方式中,在wl验证动作中,2次取得表示电流大小的数据。此外,取得表示电流大小的数据时,在第1次与第2次,使感测放大器模块sam(图1、图2)中的感测节点的放电时间不同。由此,取得表示流动在各半导体层120的电流是否大于第1目标值的数据,及表示流动在各半导体层120的电流是否大于第2目标值的数据。第2目标值例如大于第1目标值。

[0189]

此外,在时序t311,开始sgs编程动作。此处,本实施方式的sgs编程动作时,例如对位线bl供给电压v

src

,所述位线连接在:多个源极侧选择晶体管sts中,wl验证动作中流动的电流大于所述第1目标值、小于第2目标值的源极侧选择晶体管sts(以下,有时称为“第1写入选择晶体管”。);及大于所述第2目标值的源极侧选择晶体管sts(以下,有时称为“第2写入选择晶体管”。)。此外,对位线bl供给电压v

dd

,所述位线连接在多个源极侧选择晶体管sts中,wl验证动作中流动的电流小于第1目标值的源极侧选择晶体管sts(以下,有时称为“禁止选择晶体管”。)。

[0190]

此外,在时序t312,对字线wl供给写入路径电压v

pass

。此外,对漏极侧选择栅极线sgd供给电压v

sgd

。此外,对源极侧选择栅极线sgs2、sgs1、sgs0供给写入路径电压v

pass

。此外,对源极侧选择栅极线sgsb供给电压v

off

。此外,如图20所示,对位线bl侧的虚设字线dwl供给电压v

pass

'。此外,对源极线sl侧的虚设字线dwl供给写入路径电压v

pass

。

[0191]

此外,在时序t313,如图20所示,对源极侧选择栅极线sgs0供给编程电压v

pgm

。由此,将电子累积在第1写入选择晶体管及第2写入选择晶体管的电荷累积膜132,第1写入选择晶体管及第2写入选择晶体管的阈值电压增大。

[0192]

此外,在时序t314,如图19所示,对源极侧选择栅极线sgs0供给写入路径电压v

pass

。

[0193]

此外,在时序t315,对字线wl及选择栅极线(sgd、sgs2、sgs1、sgs0、sgsb)供给接地电压v

ss

。

[0194]

此外,在时序t321,对连接在第2写入选择晶体管的位线bl供给电压v

src

。此外,对连接在第1写入选择晶体管与禁止选择晶体管的位线bl供给电压v

dd

。

[0195]

此外,在时序t322,对字线wl供给写入路径电压v

pass

。此外,对漏极侧选择栅极线sgd供给电压v

sgd

。此外,对源极侧选择栅极线sgs2、sgs1、sgs0供给写入路径电压v

pass

。此外,对源极侧选择栅极线sgsb供给电压v

off

。此外,如图21所示,对位线bl侧的虚设字线dwl

供给电压v

pass

'。此外,对源极线sl侧的虚设字线dwl供给写入路径电压v

pass

。

[0196]

此外,在时序t323,如图21所示,对源极侧选择栅极线sgs1供给编程电压v

pgm

。由此,将电子累积在第2写入选择晶体管的电荷累积膜132,第2写入选择晶体管的阈值电压增大。

[0197]

此外,在时序t324,如图19所示,对源极侧选择栅极线sgs1供给写入路径电压v

pass

。

[0198]

此外,在时序t325,对字线wl及选择栅极线(sgd、sgs2、sgs1、sgs0、sgsb)供给接地电压v

ss

。

[0199]

[第4实施方式]

[0200]

接着,参照图22~图25,针对第4实施方式的半导体存储装置的电流调整顺序进行说明。图22是用来针对电流调整顺序进行说明的示意性流程图。图23是用来针对电流调整顺序进行说明的示意性波形图。图24是用来针对电流调整顺序所含的tcwl编程动作进行说明的示意性剖视图。图25是用来针对电流调整顺序所含的wl验证动作进行说明的示意性剖视图。

[0201]

第4实施方式的电流调整顺序基本上与第2实施方式的电流调整顺序同样地执行。但,第4实施方式的电流调整顺序的一部分与第2实施方式的电流调整顺序不同。

[0202]

也就是说,第2实施方式的电流调整顺序中,通过调整源极侧选择晶体管sts的阈值电压,而抑制半导体层120间的电流不均。

[0203]

然而,这种方法只不过是例示,具体方法等可适当调整。例如,为了抑制半导体层120间的电流不均,可调整漏极侧选择晶体管std的阈值电压,也可调整源极线sl侧或位线bl侧的虚拟存储单元dmc的阈值电压。此外,也可将多个存储单元mc中的任一个使用在半导体层120间电流不均的抑制,而非数据记录。以下,有时将这种存储单元mc称为“阈值电压调整用存储单元”。此外,有时将这种连接在存储单元mc的字线称为“阈值电压调整用字线tcwl”。

[0204]

例如,第4实施方式中,针对使用排列在z方向的多个存储单元mc中,位于最源极线sl侧的存储单元mc(与源极线sl侧的虚拟存储单元dmc相邻的存储单元mc),作为阈值电压调整用存储单元的例进行说明。

[0205]

接着,针对第4实施方式的电流调整顺序更具体说明。

[0206]

如图22所示,第4实施方式的电流调整顺序基本上与第2实施方式的电流调整顺序同样地实行。但,第4实施方式中,执行tcwl编程动作(步骤s402),取代sgs编程动作。

[0207]

例如,图23的例子中,在时序t401,开始tcwl编程动作。此处,本实施方式的tcwl编程动作时,例如对连接在多个阈值电压调整用存储单元中进行阈值电压调整的存储单元(以下,有时称为“写入调整用存储单元”。)的位线bl供给电压v

src

,对连接在多个阈值电压调整用存储单元中不进行阈值电压调整的存储单元(以下,有时称为“禁止调整用存储单元”。)的位线bl供给电压v

dd

。例如,将“l”锁存到连接在感测放大器模块sam中的电压传输电路的所述控制用锁存电路中,对应于写入调整用存储单元的锁存电路,将“h”锁存到对应于禁止调整用存储单元的锁存电路。此外,经由所述2条电压供给线,对写入调整用存储单元与禁止调整用存储单元供给不同电压。

[0208]

此外,在时序t402,对阈值电压调整用字线tcwl及其它字线wl供给写入路径电压vpass

。此外,对漏极侧选择栅极线sgd供给电压v

sgd

。此外,对源极侧选择栅极线sgs供给接地电压v

ss

。此外,如图24所示,对位线bl侧的虚设字线dwl供给电压v

pass

'。此外,对源极线sl侧的虚设字线dwl供给电压v

pass”。

[0209]

此外,在时序t403,如图24所示,对阈值电压调整用字线tcwl供给编程电压v

pgm

。由此,将电子累积在写入调整用存储单元的电荷累积膜132,写入调整用存储单元的阈值电压增大。

[0210]

此外,在时序t404,如图23所示,对阈值电压调整用字线tcwl供给写入路径电压v

pass

。

[0211]

此外,在时序t405,对阈值电压调整用字线tcwl、其它字线wl及选择栅极线(sgd、sgs、sgsb)供给接地电压v

ss

。

[0212]

此外,在时序t411~时序t412,执行wl验证动作。wl验证动作与第2实施方式的wl验证动作同样地执行。但,第4实施方式中,如图25所示,对阈值电压调整用字线tcwl供给与源极线sl侧的虚设字线dwl相同的电压v

read

'。此外,第4实施方式中,对应于表示wl验证动作中取得的电流大小的数据,将一部分写入调整用存储单元更新为禁止调整用存储单元。

[0213]

其它动作与第2实施方式的电流调整顺序中的动作同样地执行。

[0214]

另外,第4实施方式中,使用排列在z方向的多个存储单元mc中的一个作为阈值电压调整用存储单元。然而,这种方法只不过是例示,具体方法等可适当调整。例如,也可使用排列在z方向的多个存储单元mc中的二个以上,作为阈值电压调整用存储单元。

[0215]

此外,这种情况下,例如也可与第3实施方式同样,在验证动作中,取得表示流动在各半导体层120的电流是否大于第1目标值的数据,及表示流动在各半导体层120的电流是否大于第2目标值的数据。此外,也可在tcwl编程动作中,对特定的阈值电压调整用字线tcwl供给编程电压v

pgm

时,对位线bl供给电压v

src

,所述位线连接在:wl验证动作中流动的电流大于所述第1目标值、小于第2目标值的存储单元(以下,有时称为“第1写入调整用存储单元”。);及大于所述第2目标值的存储单元(以下,有时称为“第2写入调整用存储单元”。),对其它位线bl供给电压v

dd

。此外,也可在对其它阈值电压调整用字线tcwl供给编程电压v

pgm

时,对连接在第2写入调整用存储单元的位线bl供给电压v

src

,对其它位线bl供给电压v

dd

。

[0216]

[第5实施方式]

[0217]

接着,参照图26,针对第5实施方式的半导体存储装置的电流调整用顺序进行说明。图26是表示本实施方式的半导体存储装置的一部分构成的示意性剖视图。

[0218]

第5实施方式的半导体存储装置基本上与第1实施方式~第4实施方式的半导体存储装置同样地构成。但,第5实施方式的半导体存储装置的一部分构成与第1实施方式~第4实施方式的半导体存储装置不同。

[0219]

例如,第1实施方式~第4实施方式中,例如如参照图4等所说明,在多个导电层110的下方,设有作为源极侧栅极线sgsb发挥功能的导电层111,在导电层111的下方,设有作为源极线sl发挥功能的导电层112。然而,这种构成只不过是例示,具体构成等可适当调整。

[0220]

例如,图26的例子中,在多个导电层110的下方设有导电层511。导电层511包含氮化钛(tin)等障壁导电膜及钨(w)等金属膜的积层膜等。导电层511作为源极侧选择栅极线sgsb(图2),及与其连接的多个源极侧选择晶体管stsb的栅极电极发挥功能。

[0221]

此外,图26的例子中,半导体存储装置具备半导体层520取代半导体层120。半导体

层520基本上与第1实施方式~第4实施方式的半导体层120同样地构成。但,在半导体层520的下端部,未连接杂质区域122。

[0222]

此外,图26的例子中,半导体层520的下端部经由单结晶硅(si)等半导体层522,连接在半导体衬底100的p型阱区域。此外,在半导体层522与导电层511间,设有氧化硅(sio2)等绝缘膜523。

[0223]

此处,这种构成中,有时在制造步骤中,会导致半导体层520的下端与半导体层522的接触面积不均。伴随于此,有时在半导体层520间,会导致电流的大小产生不均。

[0224]

因此,第5实施方式中,执行第1实施方式~第4实施方式的任一个中的电流调整顺序。由此,可抑制半导体层520间的电流不均。

[0225]

[其它实施方式]

[0226]

以上,针对第1实施方式~第5实施方式的半导体存储装置及其动作条件的调整方法进行了说明。然而,以上的说明只不过是例示,具体的构成及方法等可适当调整。

[0227]

例如,如参照图11所例示,第1实施方式~第3实施方式的电流调整顺序中,一边增大环路次数ni,一边重复执行sgs编程动作及wl验证动作。此外,如参照图22所例示,第4实施方式的电流调整顺序中,一边增大环路次数ni,一边重复执行tcwl编程动作及wl验证动作。然而,这种动作只不过是例示,具体方法可适当调整。例如,也可在第1实施方式~第5实施方式中,仅执行1次wl验证动作,之后,仅执行1次sgs编程动作或tcwl编程动作。

[0228]

此外,例如第1实施方式~第5实施方式的半导体存储装置也可构成为根据特定命令的输入,执行所述电流调整顺序。

[0229]

[其它]

[0230]

虽说明了本发明的若干实施方式,但这些实施方式是作为例子而提出的,并非意在限定发明的范围。这些新颖的实施方式能够以其它各种方式实施,可在不脱离发明主旨的范围内进行各种省略、置换、变更。所述实施方式或其变化包含在发明的范围或主旨内,且包含在权利要求书所记载的发明及其均等的范围内。

[0231]

[符号的说明]

[0232]

mc

ꢀꢀ

存储单元

[0233]

mca 存储单元阵列

[0234]

add 地址数据

[0235]

cmd 命令数据

[0236]

pc

ꢀꢀ

外围电路。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。