1.本发明涉及电子电路技术领域,尤其涉及一种灵敏放大器及存储器。

背景技术:

2.灵敏放大器(sense amplifier,sa)是数模混合电路的关键基础组件之一,有多种类型,广泛应用于存储器中。

3.以静态随机存储器(static random access memory,sram)为例,sram中一般采用高速、低功耗的锁存型灵敏放大器。对sram执行读操作时,位线先预充,然后通过被选中存储单元进行放电,由于位线负载比较大,两个位线的电平差很小,就需要通过灵敏放大器电路快速进行放大,以保证sram的读取速度。

4.随着器件工艺尺寸越来越小,大气层中的一些粒子也能够引起器件的单粒子翻转(single event upset,seu),一般称为软错误(soft error)。单粒子翻转(single event upset,seu),指的是空间环境中单个高能粒子入射到半导体器件灵敏区后,激发电子空穴对,进而引起器件逻辑状态翻转的现象。单粒子翻转,可能会使得sram发生故障。

5.然而,现有的灵敏放大器,无法抵抗单粒子翻转。

技术实现要素:

6.本发明解决的技术问题是:提供一种能够抵抗单粒子翻转的灵敏放大器。

7.为解决上述技术问题,本发明实施例提供一种灵敏放大器,所述灵敏放大器包括:第一锁存电路及第二锁存电路,所述第一锁存电路具有电位互补的第一输入节点及第二输入节点;所述第二锁存电路具有电位互补的第一抗翻转节点及第二抗翻转节点;其中:

8.所述第一锁存电路,适于增大所述第一输入节点及第二输入节点之间的电位差,使得所述第一输入节点及第二输入节点的电位互补;

9.所述第二锁存电路,与所述第一锁存电路耦接,适于在所述第一输入节点及第二输入节点的电位互补后,当所述第一输入节点或第二输入节点出现单粒子瞬态时,通过调整所述第一抗翻转节点及第二抗翻转节点的电位,来保持另一输入节点的电位不变,并通过所述另一输入节点为出现单粒子瞬态的输入节点充电,直至恢复所述出现单粒子瞬态的输入节点的电位。

10.可选地,所述第一锁存电路由两对晶体管构成,每对晶体管包括一个pmos管及一个nmos管。

11.可选地,所述第一锁存电路包括:第一pmos管、第二pmos管、第一nmos管及第二nmos管;其中:

12.所述第一pmos管,栅极与所述第一输入节点耦接,漏极与所述第一nmos管的漏极耦接,源极与第二pmos管的源极耦接;

13.所述第一nmos管,栅极与所述第二锁存电路耦接,源极与所述第二nmos管的源极耦接;

14.所述第二pmos管,栅极与所述第二抗翻转节点耦接,漏极与所述第二nmos管的漏极耦接;

15.所述第二nmos管,栅极与所述第二输入节点耦接。

16.可选地,所述第二锁存电路由两对晶体管构成,对晶体管包括一个pmos管及一个nmos管。

17.可选地,所述第二锁存电路包括:第三pmos管、第四pmos管、第三nmos管及第四nmos管;其中:

18.所述第三pmos管,栅极与所述第一抗翻转节点耦接,漏极与所述第三nmos管的漏极耦接,源极与所述第四pmos管的源极耦接;

19.所述第三nmos管,栅极与所述第一锁存电路耦接,源极与所述第四nmos管的源极耦接;

20.所述第四pmos管,栅极与所述第一锁存电路耦接,漏极与所述第四nmos管的漏极耦接;

21.所述第四nmos管,栅极与所述第三nmos管的漏极耦接。

22.可选地,所述灵敏放大器还包括:控制电路,与所述第一锁存电路及第二锁存电路耦接,适于接收使能信号,并在所述使能信号的控制下,使得所述第一锁存电路及第二锁存电路开始工作。

23.可选地,所述控制电路包括:第五nmos管,所述第五nmos管的栅极适于输入所述使能信号,漏极与所述第一锁存电路及第二锁存电路耦接,源极接地。

24.可选地,所述第五nmos管的数量为四个,各所述第五nmos管的漏极分别与所述第一锁存电路及第二锁存电路中不同的nmos管耦接。

25.可选地,所述灵敏放大器还包括:预充电路,与所述第一锁存电路及第二锁存电路耦接,适于将所述第一输入节点、第二输入节点、第一抗翻转节点及第二抗翻转节点的电位预充至预设电位。

26.可选地,所述预充电路包括:第一预充子电路及第二预充子电路;

27.所述第一预充子电路,与所述第一锁存电路耦接,适于对所述第一输入节点及第二输入节点的电位进行预充;

28.所述第二预充子电路,与所述第二锁存电路耦接,适于对所述第一抗翻转节点及第二抗翻转节点的电位进行预充。

29.可选地,所述第二预充子电路,包括:第五pmos管及第六pmos管;所述第五pmos管及第六pmos管,栅极适于接收预充控制信号,源极与电源电压输出端耦接,栅极与所述第二锁存电路耦接。

30.可选地,所述第一预充子电路,包括:第七pmos管、第八pmos管及第九pmos管;其中:

31.所述第七pmos管、第八pmos管及第九pmos管,栅极适于接收所述预充控制信号;所述第七pmos管及第八pmos管,漏极与所述第一锁存电路耦接,源极与电源电压输出端耦接;所述第九pmos管的漏极与所述第七pmos管耦接;所述第九pmos管的源极与所述第八pmos管耦接。

32.可选地,所述灵敏放大器还包括:输出电路,适于将所述第一输入节点及所述第二

输入节点的电位输出。

33.本发明实施例还提供了一种存储器,具有互补位线对,所述存储器还包括:上述任一种所述的灵敏放大器;所述灵敏放大器的第一输入节点及第二输入节点,与同一位线对中不同位线耦接。

34.与现有技术相比,本发明实施例的技术方案具有以下有益效果:

35.采用上述方案,通过在灵敏放大器中设置第二锁存电路,所述第二锁存电路可以在第一输入节点或第二输入节点出现单粒子瞬态时,保持另一输入节点的电位不变,并通过所述另一输入节点为出现单粒子瞬态的输入节点充电,直至恢复所述出现单粒子瞬态的输入节点的电位,由此可以使得灵敏放大器能够抵抗单粒子翻转。并且,本发明实施例中的灵敏放大器,电路结构简单,对存储器的读出速度影响较小,实用性较强。

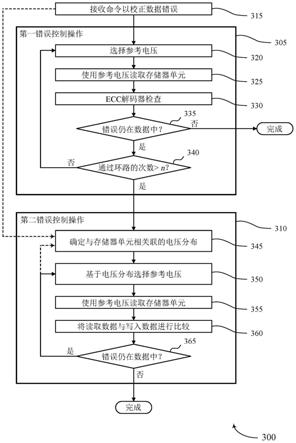

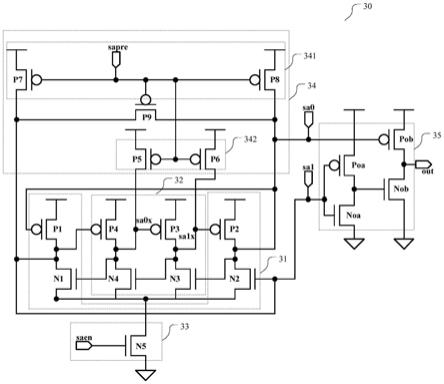

附图说明

36.图1是一种现有灵敏放大器的电路结构示意图;

37.图2是图1中灵敏放大器的工作时序示意图;

38.图3是本发明实施例中一种灵敏放大器的电路结构示意图;

39.图4是图3中灵敏放大器的工作时序示意图;

40.图5是本发明实施例中另一种一种灵敏放大器的电路结构示意图;

41.图6是本发明实施例中一种存储器的结构示意图。

具体实施方式

42.图1为现有技术中一种灵敏放大器10的电路结构示意图。参照图1,在灵敏放大器10中,pmos管ka、pmos管kb及pmos管kc组成预充电路11,由预充控制信号sapre控制。pmos管k1、nmos管m1、pmos管k2及nmos管m2四个晶体管组成锁存电路12。节点sa1及sa0为互补输入端,与存储器中同一位线对的不同位线连接。nx为尾电流管,由使能信号saen控制。pmos管koa、nmos管moa、pmos管kob及nmos管mob四个晶体管,组成输出电路13,输出端为out。

43.图2为图1中灵敏放大器10的工作时序图。结合图2及图1,对上述灵敏放大器10的工作过程说明如下:

44.预充控制信号sapre置为低电平,节点sa1及sa0分别被预充到固定电位。然后,将预充控制信号sapre置为高电平,存储器某一位线对上两条位线之间的电位差,会传输至节点sa1及节点sa0上,进而在节点sa1及节点sa0之间建立相应的电位差。

45.以节点sa1的电位被被往下拉为例,将使能信号saen置为高电平,使得尾电流管mx打开,尾电流管mx的电阻会快速变小。由于节点sa1的电位被下拉,故图1中nmos管m2的电阻增大,pmos管k2的电阻减小,节点sa0维持在高电平,nmos管m1管的电阻不变、pmos管k1管的电阻不变,pmos管k1、nmos管m1、pmos管k2及nmos管m2四个晶体管互相促进,使得pmos管k1及nmos管m1这一对晶体管的电阻,与pmos管k2及nmos管m2这一对晶体管的电阻,二者之间的电阻差逐渐变大,进而快速拉大了节点sa1与节点sa0之间的电位差。

46.最后,通过输出电路13实现双端转单端输出,得到输出信号。

47.参照图1,假设节点sa1与节点sa0之间的电位差被拉大后,最终使得节点sa1的电位为1,而节点sa0的电位为0,将sa1=1、sa0=0作为初值,此状态下,pmos管k1将开启,nmos

管m1将关闭,pmos管k2将关闭,nmos管m2将开启,输出端out电平为1。

48.某个时刻,单粒子入射到nmos管m1的漏端,使得节点sa1的电位值由1往下跳变,产生一个向下的脉冲,引起pmos管k2开启,nmos管m2关闭,进一步使得节点sa0的电位开始升高,从而引起pmos管k1关闭,nmos管m2开启,最终节点sa1的电位值跳变为0,节点sa0的电位值变为1。灵敏放大器10输出端out的电位值由1变0发生翻转,即发生单粒子翻转。

49.同样,如果初值为sa1=0、sa0=1,单粒子入射到nmos管m2时,也会导致单粒子翻转,过程与前述类似。

50.单粒子翻转会引发存储器故障。

51.为了解决上述问题,本发明实施例提供了一种灵敏放大器,所述灵敏放大器中设置第二锁存电路,所述第二锁存电路可以在第一输入节点或第二输入节点出现单粒子瞬态时,保持另一输入节点的电位不变,并通过所述另一输入节点为出现单粒子瞬态的输入节点充电,直至恢复所述出现单粒子瞬态的输入节点的电位,由此可以使得灵敏放大器能够抵抗单粒子翻转。

52.为使本发明的上述目的、特征和优点能够更为明显易懂,下面结合附图对本发明的具体实施例作详细地说明。

53.图3为本发明实施例中一种灵敏放大器30的电路结构示意图。参照图3,所述灵敏放大器30可以包括:第一锁存电路31及第二锁存电路32。

54.所述第一锁存电路31具有电位互补的第一输入节点sa0及第二输入节点sa1。所述第二锁存电路32具有电位互补的第一抗翻转节点sa0x及第二抗翻转节点sa1x。其中:

55.所述第一锁存电路31,适于增大所述第一输入节点sa0及第二输入节点sa1之间的电位差,使得所述第一输入节点sa0及第二输入节点sa1的电位互补。

56.所述第二锁存电路32,与所述第一锁存电路31耦接,适于在所述第一输入节点sa0及第二输入节点sa1的电位互补后,当所述第一输入节点sa0或第二输入节点sa1出现单粒子瞬态时,通过调整所述第一抗翻转节点sa0x及第二抗翻转节点sa1x的电位,来保持另一输入节点的电位不变,并通过所述另一输入节点为出现单粒子瞬态的输入节点充电,直至恢复所述出现单粒子瞬态的输入节点的电位。

57.在具体实施中,单粒子瞬态(single event transient,set),是由带能粒子入射引起的,一般表现为电压脉冲的形式。入射节点为高电平时,入射节点出现单粒子瞬态,表现为入射节点产生负向脉冲。入射节点为低电平时,入射节点出现单粒子瞬态,表现为入射节点产生正向脉冲。因单粒子瞬态而产生的脉冲(简称为单粒子脉冲,如图4所示),在传播过程中可能消减也可能被扩展,如果被时序元件(比如锁存电路)捕获就会引起单粒子翻转错误。如果全局信号的发生单粒子瞬态,则可能引起全局性故障。

58.具体地,当第一输入节点sa0出现单粒子瞬态时,所述第二锁存电路32可以保持第二输入节点sa1的电位不变,并通过第二输入节点sa1为第一输入节点sa0充电,直至恢复第一输入节点sa0的电位。

59.当第二输入节点sa1出现单粒子瞬态时,所述第二锁存电路32可以保持第一输入节点sa0的电位不变,并通过第一输入节点sa0为第二输入节点sa1充电,直至恢复第二输入节点sa1的电位。

60.由于第二锁存电路32,可以在任意输入节点出现单粒子瞬态时,保持另一输入节

点的电位不变,从而可以基于第一抗翻转节点sa0x、第二抗翻转节点sa1x及第一输入节点sa0的电位,使得出现单粒子瞬态的输入节点快速恢复,从而可以有效抵抗单粒子翻转。

61.在具体实施中,所述第一锁存电路31可以存在多种电路结构,具体不作限制,只要能够增大所述第一输入节点sa0及第二输入节点sa1之间的电位差,使得所述第一输入节点sa0及第二输入节点sa1的电位互补即可。

62.在本发明的一实施例中,所述第一锁存电路31可以由两对晶体管构成,每对晶体管包括一个pmos管及一个nmos管。

63.在具体实施中,所述两对晶体管可以采用多种方式连接,具体不作限制。

64.在本发明的一实施例中,所述第一锁存电路31可以包括:第一pmos管p1、第二pmos管p2、第一nmos管n1及第二nmos管n2。

65.其中:

66.所述第一pmos管p1的栅极与所述第一输入节点sa0耦接,漏极与所述第一nmos管n1的漏极耦接,源极与第二pmos管p2的源极耦接;

67.所述第一nmos管n1,栅极与所述第二锁存电路32耦接,源极与所述第二nmos管n1的源极耦接;

68.所述第二pmos管p2,栅极与所述第二抗翻转节点sa1x耦接,漏极与所述第二nmos管n2的漏极耦接;

69.所述第二nmos管n2,栅极与所述第二输入节点sa1耦接。

70.在实际应用中,可以在第二nmos管n2及第一nmos管n1的源极接入低电压,使得第一nmos管n1及第二nmos管n2导通。假设存储器位线对中两条位线的电压差,被传输至第一输入节点sa0及第二输入节点sa1,且第二输入节点sa1的电位被下拉,则第二nmos管n2倾向于关闭,故第二nmos管n2的电阻增大,而第二pmos管p2导通,故第二pmos管p2的电阻减小,进而使得第一输入节点sa0维持在高电平。此时,第一nmos管n1及第一pmos管p1的电阻不变,由此使得第一pmos管p1及第一nmos管n1这一晶体管对的电阻,与第二nmos管n2及第二pmos管p2这一晶体管对的电阻,之间的差值逐渐增大,从而使得第一输入节点sa0及第二输入节点sa1的电位快速拉开。

71.在具体实施中,所述第二锁存电路32可以存在多种电路结构,具体不作限制。

72.在本发明的一实施例中,所述第二锁存电路32可以由两对晶体管构成,对晶体管包括一个pmos管及一个nmos管。

73.在具体实施中,所述第二锁存电路32中两对晶体管之间的连接方式,可以存在多种,只要能够在其中输入节点出现单粒子瞬态时,使得出现单粒子瞬态的输入节点尽快恢复电位即可。

74.在本发明的一实施例中,所述第二锁存电路32可以包括:第三pmos管p3、第四pmos管p4、第三nmos管n3及第四nmos管n4。其中:

75.所述第三pmos管p3,栅极与所述第一抗翻转节点sa0x耦接,漏极与所述第三nmos管n3的漏极耦接,源极与所述第四pmos管p4的源极耦接;

76.所述第三nmos管n3,栅极与所述第一锁存电路31耦接,源极与所述第四nmos管n4的源极耦接;

77.所述第四pmos管p4,栅极与所述第一锁存电路31耦接,漏极与所述第四nmos管n4

的漏极耦接;

78.所述第四nmos管n4,栅极与所述第三nmos管n3的漏极耦接。

79.当所述第一锁存电路31由第一pmos管p1、第二pmos管p2、第一nmos管n1及第二nmos管n2构成时,第三nmos管n3的栅极可以与第二nmos管n2的漏极耦接,第四pmos管p4的栅极可以与第一pmos管的漏极耦接。

80.在具体实施中,第一抗翻转节点sa0x及第二抗翻转节点sa1x,可以在第一输入节点sa0或第二输入节点sa1出现单粒子瞬态时,基本不受影响,进而使得另一未出现单粒子瞬态的输入节点的电位保持不变。而另一未出现单粒子瞬态的输入节点的电位,可以使得相应晶体管开启,进而能够间接通过该相应晶体管,为出现单粒子瞬态的输入节点充电。

81.图4为本发明实施例中灵敏放大器30的工作时序图。假设第一锁存电路31将第一输入节点sa0的电位升高至高电平,而第二输入节点sa1的电位被下拉至低电平,即sa1=1,sa0=0,第一抗翻转节点sa0x的电位为低电平而第二抗翻转节点sa1x为高电平,结合图4及图3,对所述灵敏放大器30的工作过程详细描述如下:

82.若单粒子入射到第一nmos管n1的漏端,会使得第二输入节点sa1出现向下的脉冲,该脉冲会使第四nmos管n4倾向于关闭。

83.但,由于第四pmos管p4管仍处于关闭状态,第二抗翻转节点sa1x的值未受到单粒子影响,仍为高电平,即sa1x=1,所以第一输入节点sa0点的值仍保持低电平,不会立即翻转。

84.单粒子脉冲发生期间,第一输入节点sa0的电位能够使得第二pmos管p2开启,通过第二pmos管p2给第二输入节点sa1充电,第一抗翻转节点sa0x的电位使得第二nmos管n2关闭。

85.在单粒子脉冲经过之后,第二输入节点sa1点的电平就会恢复,从而起到抗单粒子翻转的作用,即第二输入节点sa1的电位恢复为初值。

86.在本发明的一实施例中,参照图3,所述灵敏放大器30还可以包括:控制电路33。所述控制电路33可以与所述第一锁存电路31及第二锁存电路32耦接,适于接收使能信号saen,并在所述使能信号saen的控制下,使得所述第一锁存电路31及第二锁存电路32开始工作。

87.在具体实施中,所述控制电路33可以采用多种电路结构实现,具体不作限制。

88.在本发明的一实施例中,参照图3,所述控制电路33可以包括:第五nmos管n5。所述第五nmos管n5的栅极适于输入所述使能信号saen,漏极与所述第一锁存电路31及第二锁存电路32耦接,源极接地。

89.在具体实施中,第五nmos管n5的漏极可以与第一锁存电路31及第二锁存电路中各nmos管的源极连接。将所述使能信号saen置为高电平,使得第五nmos管n5打开,第五nmos管n5的电阻会快速变小,由此可以使得第一锁存电路31及第二锁存电路32中开始工作。

90.在具体实施中,所述控制电路33可以仅包括一个第五nmos管n5,也可以包括多个第五nmos管n5,具体数量不作限制。

91.在本发明的一实施例中,如图5所示,为了使得第一锁存电路31及第二锁存电路32中每一对晶体管可以使用独立的尾电流管,所述第五nmos管n5的数量至少为四个,由此可以进一步避免输入节点发生单粒子瞬态时,影响抗翻转节点的电位,增强输入节点与抗翻

转节点之间的隔离性能,降低第五nmos管n5被单粒子击中而引起单粒子翻转的风险。

92.比如,参照图5,第五nmos管n5的数量为四个,各所述第五nmos管n5的漏极分别与所述第一锁存电路31及第二锁存电路32中不同的nmos管耦接。

93.在本发明的一实施例中,参照图3,所述灵敏放大器30还可以包括:预充电路34。所述预充电路34与所述第一锁存电路31及第二锁存电路32耦接,适于将所述第一输入节点sa0、第二输入节点sa1、第一抗翻转节点sa0x及第二抗翻转节点sa1x的电位预充至预设电位。

94.在具体实施中,所述预设电位可以为电源电压值,或其它约定值,具体不作限定。

95.在本发明的一实施例中,参照图3,所述预充电路34可以包括:第一预充子电路341及第二预充子电路342;

96.所述第一预充子电路341,与所述第一锁存电路31耦接,适于对所述第一输入节点sa0及第二输入节点sa1的电位进行预充;

97.所述第二预充子电路342,与所述第二锁存电路32耦接,适于对所述第一抗翻转节点sa0x及第二抗翻转节点sa1x的电位进行预充。

98.在本发明的一实施例中,所述第二预充子电路342可以包括:第五pmos管p5及第六pmos管p6。所述第五pmos管p5及第六pmos管p6,栅极适于接收预充控制信号sapre,源极与电源电压输出端耦接,栅极与所述第二锁存电路32耦接。

99.在本发明的一实施例中,所述第一预充子电路341可以,包括:第七pmos管p7、第八pmos管p8及第九pmos管p9。其中:

100.所述第七pmos管p7、第八pmos管p8及第九pmos管p9,栅极适于接收所述预充控制信号sapre;所述第七pmos管p7及第八pmos管p8,漏极与所述第一锁存电路31耦接,源极与电源电压输出端耦接;所述第九pmos管p9的漏极与所述第七pmos管p7耦接;所述第九pmos管p9的源极与所述第八pmos管p8耦接。

101.在本发明的一实施例中,参照图3,所述灵敏放大器还可以包括:输出电路35。所述输出电路35适于将所述第一输入节点sa0及所述第二输入节点sa1的电位输出。

102.在具体实施中,所述输出电路35可以包括pmos管poa、nmos管noa、pmos管pob及nmos管nob。通过该四个晶体管,可以实现双端转单端输出,在输出端out输出相应的信号。其中,第二输入节点sa1的信号,一般与输出端out输出的信号同相。第一输入节点sa0的信号,一般与输出端out输出的信号反相。

103.本发明实施例还提供了一种存储器,所述存储器具有互补位线对。所述存储器还包括上述实施例中任一种所述的灵敏放大器30,所述灵敏放大器30的第一输入节点sa0及第二输入节点sa1,与同一位线对中不同位线耦接。

104.在具体实施中,参照图6,除灵敏放大器30外,存储器可以包括:位线预充电路61、存储阵列62及字线读选择电路63。

105.具体地,pmos管p0、pmos管p1及pmos管p2三个晶体管是位线预充电路61,由位线预充信号blpre控制。

106.位线预充电路61下方为存储阵列62。所述存储阵列62包括较多呈阵列分布的存储单元(比如128个、256个或512个),每行存储单元字线各不相同。比如,存储单元nwx1及存储单元nwx0所在行使用位线wl_xx,而存储单元nws1及存储单元nws0所在行使用位线wl_sel。

所有存储单元可以共用由位线bl1及位线bl0组成的位线对。

107.pmos管prs0及pmos管prs1组成字线读选择电路63,由列选择信号bl_rsel控制。由位线bl1及位线bl0组成的位线对,通过pmos管prs0及pmos管prs1与灵敏放大器30的第一输入节点sa0及第二输入节点sa1相连。

108.可以理解的是,位线预充电路61、存储阵列62及字线读选择电路63仅是一具体实施例,在具体实施中,也可以采用其它电路结构实现,此处不作限制。

109.下面结合图3、图4及图6,对存储器的读出过程进行详细描述:

110.在一个读周期中,首先位线预充信号blpre置为低电平,位线bl1及bl0分别被预充到固定电位,预充控制信号sapre置为低电平,第一输入节点sa0及第二输入节点sa1被预充到固定电位。

111.之后,将位线预充信号blpre及预充控制信号sapre置为高电平,同时将字线wl_sel置为高电平,列选择信号bl_rsel置为低电平,存储单元mcell_sel开始拉动位线对,使得位线bl1及bl0之间逐渐建立起电压差,进而通过pmos管prs0及pmos管prs1传输到第一输入节点sa0及第二输入节点sa1上,在第一输入节点sa0及第二输入节点sa1之间建立相应的压差。

112.假设位线bl1的电位被下拉,进而使得第二输入节点sa1的电位被下拉,故将使能信号saen置为高电平时,第五nmos管n5将打开,第五nmos管n5的电阻快速变小,而第三nmos管n3的电阻增大,第三pmos管p3的电阻减小,由此使得第一输入节点sa0的电位维持在高电平。同时,第二nmos管n2的电阻不变,第二pmos管p2的电阻不变,进而使得第三nmos管n3及第三pmos管p3这一侧的电阻,与第二nmos管n2及第二pmos管p2的电阻,二者之间的差值逐渐变大,从而快速拉大第一输入节点sa0及第二输入节点sa1之间的电位差。最后通过输出电路35输出相应的信号。

113.在实际应用中,输出端out输出的信号会被后续电路锁存,然后可以关闭字线wl_sel和使能信号saen,恢复位线预充信号blpre和预充控制信号sapre,重复执行预充操作。

114.在本发明的实施例中,所述存储器可以为静态随机存储器,也可以为动态随机存取存储器(dynamic random access memory,dram)、阻变式存储器(resistive random access memory,rram)、铁电存储器(ferroelectric ram,feram)或闪存(flash)等,具体不作限制。在所述存储器中设置所述灵敏放大,实现存储器整体电路的抗单粒子翻转能力。

115.由上述内容可知,本发明实施例中的灵敏放大器30,由于设置有第二锁存电路32,所述第二锁存电路32可以在第一输入节点或第二输入节点出现单粒子瞬态时,保持另一输入节点的电位不变,并通过所述另一输入节点为出现单粒子瞬态的输入节点充电,直至恢复所述出现单粒子瞬态的输入节点的电位,由此可以使得灵敏放大器能够抵抗单粒子翻转。

116.另外,本发明实施例中的灵敏放大器30,对位线电压没有限制,不仅可以适用于位线电压在2.5v、3.3v甚至5v的高压情况,还可以适用于位线电压在1.2v甚至0.8v的低压情况,即可以适用于更先进工艺节点,而且结构简单,实现更加方便,消耗的电路面积也更少。并且,本发明中,灵敏放大器30的电阻,相对于图1中示出的灵敏放大器10,电阻增加较小,故对灵敏放大器的读出速度影响较小,实用性更高。

117.虽然本发明披露如上,但本发明并非限定于此。任何本领域技术人员,在不脱离本

发明的精神和范围内,均可作各种更动与修改,因此本发明的保护范围应当以权利要求所限定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。