1.本发明涉及一种多存储体型半导体存储器装置,并且更具体地,涉及一种能够减少数据线中的电流消耗的多存储体型半导体存储器装置。

背景技术:

2.通常,半导体存储器装置以其中包括多个存储体的多存储体结构实现。在这样的多存储体型半导体存储器装置中,在一个存储体上执行数据读取操作的同时,在另一存储体上执行数据读取操作之前所需的预充电操作。因此,多存储体型半导体存储器装置在实现高速方面具有很大的优势。

3.但是,在现有的多存储体型半导体存储器装置中,从每个存储体读取的数据通过相同数据输入/输出线(称为“全局数据线”)从芯片传输到外部装置。

4.因此,在现有的多存储体型半导体存储器装置中,数据输入/输出线变长,因此在数据输入/输出线中形成较大的负载。如此大的负载成为限制数据传输速度的因素。

5.另选地,为了补偿根据大负载的数据传输速度的降低,在现有的多存储体型半导体存储器装置中,甚至可以使用高电平的电源电压。

6.然而,在这种情况下,出现的问题是半导体存储器装置的数据线中的电流消耗变大。

技术实现要素:

7.本发明针对一种多存储体型半导体存储器装置,其允许在保持适当的数据传输速度的同时减少数据线中的电流消耗。

8.本发明涉及一种多存储体型半导体存储器装置。根据本发明的一个方面,提供了一种多存储体类型的半导体存储器装置,该多存储体类型的半导体存储器装置包括:存储体组,该存储体组包括第一存储体、第二存储体、第三存储体和第四存储体,第一存储体、第二存储体、第三存储体和第四存储体中的每一个输出存储体数据,其中,第二存储体被设置在第一存储体的下方,第三存储体被设置在第一存储体的右侧,并且第四存储体被设置在第三存储体的下方;水平数据线,该水平数据线沿横向方向在第一存储体和第二存储体之间以及第三存储体和第四存储体之间延伸;垂直数据线,该垂直数据线沿垂直方向在第一存储体和第三存储体之间以及第二存储体和第四存储体之间延伸;第一存储体读取放大器、第二存储体读取放大器、第三存储体读取放大器和第四存储体读取放大器,该第一存储体读取放大器、第二存储体读取放大器、第三存储体读取放大器和第四存储体读取放大器被设置为与第一至第四存储体相对应,并且被配置为放大第一至第四存储体的存储体数据段,以根据对第一至第四存储体的选择输出读取数据段;第一读取驱动器,该第一读取驱动器被配置为驱动第一存储体读取放大器和第二存储体读取放大器的读取数据段,以根据对第一存储体和第二存储体的选择提供读取数据段作为水平数据线的水平局部数据段;第二读取驱动器,该第二读取驱动器被配置为驱动第三存储体读取放大器和第四存储体读取放

大器的读取数据段,以根据对第三存储体和第四存储体的选择提供读取数据段作为水平数据线的水平局部数据段;高阻抗驱动器,该高阻抗驱动器被配置为根据对第一至第四存储体中的一个的选择来驱动水平局部数据以输出水平局部数据作为垂直数据线的垂直局部数据;以及全局放大器,该全局放大器被配置为放大垂直局部数据,以提供放大后的垂直局部数据作为全局数据线的全局数据,其中,全局数据线电连接到输入/输出缓冲器。当上拉时,以高电源电压驱动第一至第四存储体中的每一个的存储体数据和全局数据,并且当上拉时,以低于高电源电压的低电源电压控制水平局部数据和垂直局部数据。

附图说明

9.通过参照附图详细描述本发明的示例性实施方式,本发明的上述和其他目的、特征和优点对于本领域技术人员将变得更加明显,在附图中:

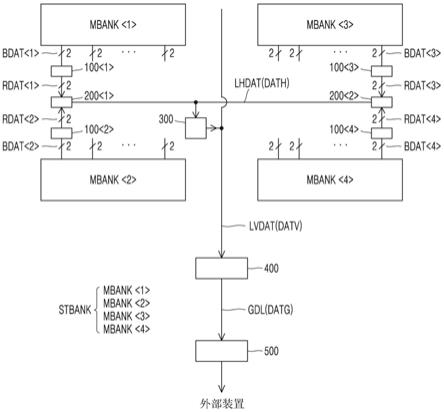

10.图1是示出根据本发明的一种实施方式的多存储体(multi-bank)型半导体存储器装置的图;

11.图2是示出图1的存储体读取放大器的图;

12.图3a是示出图1的第一读取驱动器的详细图;

13.图3b是示出图1的第二读取驱动器的详细图;

14.图4是示出图1的高阻抗驱动器的详细图;以及

15.图5是示出图1的全局放大器的详细图。

具体实施方式

16.图1是示出根据本发明的一种实施方式的多存储体型半导体存储器装置的图。注意,在本发明的半导体存储器装置中,当上拉时,要传输的数据根据传输位置在高电源电压hvdd或低电源电压lvdd处被上拉。这里,高电源电压hvdd是相对较高的电平,并且低电源电压lvdd是相对较低的电平。

17.参照图1,本发明的半导体存储器装置包括具有第一存储体mbank《1》至第四存储体mbank《4》的存储体组stbank。在这种情况下,以不交叠的方式选择第一存储体mbank《1》至第四存储体mbank《4》。另外,第一存储体mbank《1》至第四存储体mbank《4》中的每一个都输出存储体数据bdat。

18.第一个存储体mbank《1》向下输出存储体数据bdat《1》。第二存储体mbank《2》设置在第一存储体mbank《1》的下方,并且向上输出存储体数据bdat《2》。第三存储体mbank《3》设置在第一存储体mbank《1》的右侧,并向下输出存储体数据bdat《3》。另外,第四存储体mbank《4》设置在第一存储体mbank《1》的下方,并且向上输出存储体数据bdat《4》。

19.在这种情况下,当上拉时,以高电源电压hvdd控制从第一至第四存储体mbank《1》至mbank《4》输出的存储体数据段bdat。因此,使由于电压降引起的存储体数据段bdat的数据损失最小化。

20.作为参考,在本公开中,为了描述简单,典型地示出并描述了一个存储体组stbank。但是,存储体组stbank的数量可以增加到两个或更多。

21.另外,本发明的半导体存储器装置还包括水平数据线lhdat、垂直数据线lvdat、第一存储体读取放大器100《1》至第四存储体读取放大器100《4》、第一读取驱动器200《1》、第

二读取驱动器200《2》、高阻抗300以及全局放大器400。

22.在本公开中,水平数据线lhdat、垂直数据线lvdat、第一存储体读取放大器100《1》至第四存储体读取放大器100《4》、第一读取驱动器200《1》、第二读取驱动器200 2、高阻抗300、全局放大器400和输入/输出缓冲器500中的每一个被示出为一个组件。然而,这仅是为了描述的简洁和清楚,并且上述组件中的每一个根据从每个存储体mbank中一次读取的数据段的数量,通常实现为多个组件。

23.例如,当每个存储体mbank具有其中一次读取128个数据段的结构时,水平数据线lhdat、垂直数据线lvdat、第一存储体读取放大器100《1》至第四存储体读取放大器100《4》、第一读取驱动器200《1》、第二读取驱动器200《2》、高阻抗300和全局放大器400中的每一个可以被实现为128个组件。另外,当突发长度是八时,输入/输出缓冲器500可以被实现为十六个输入/输出缓冲器。

24.水平数据线lhdat沿横向方向在第一存储体mbank《1》和第二存储体mbank《2》之间以及第三存储体mbank《3》和第四存储体mbank《4》之间延伸为很长。

25.垂直数据线lvdat沿垂直方向在第一存储体mbank《1》和第三存储体mbank《3》之间以及第二存储体mbank《2》和第四存储体mbank《4》之间延伸为很长。

26.第一存储体读取放大器100《1》至第四存储体读取放大器100《4》被设置为分别与第一存储体mbank《1》至第四存储体mbank《4》相对应。

27.具体地,第一存储体读取放大器100《1》被设置为与第一存储体mbank《1》相对应。另外,根据对与第一存储体读取放大器100《1》相对应的第一存储体mbank《1》的选择,第一存储体读取放大器100《1》放大第一存储体mbank《1》的存储体数据bdat《1》,以输出放大的存储体数据bdat《1》作为读取数据rdat《1》。优选地,当上拉时,以高电源电压hvdd控制第一存储体mbank《1》的读取数据rdat《1》。

28.第二存储体读取放大器100《2》被设置为与第二存储体mbank《2》相对应。另外,根据对与第二存储体读取放大器100《2》相对应的第二存储体mbank《2》的选择,第二存储体读取放大器100《2》放大第二存储体mbank《2》的存储体数据bdat《2》,以输出放大的存储体数据bdat《2》作为读取数据rdat《2》。优选地,当上拉时,以高电源电压hvdd控制第二存储体mbank《2》的读取数据rdat《2》。

29.第三存储体读取放大器100《3》被设置为与第三存储体mbank《3》相对应。另外,根据对与第三存储体读取放大器100《3》相对应的第三存储体mbank《3》的选择,第三存储体读取放大器100《3》放大第三存储体mbank《3》的存储体数据bdat《3》,以输出放大的存储体数据bdat《3》作为读取数据rdat《3》。优选地,当上拉时,以高电源电压hvdd控制第三存储体mbank《3》的读取数据rdat《3》。

30.另外,第四存储体读取放大器100《4》被设置为与第四存储体mbank《4》相对应。另外,根据对与第四存储体读取放大器100《4》相对应的第四存储体mbank《4》的选择,第四存储体读取放大器100《4》放大第四存储体mbank《4》的存储体数据bdat《4》,以输出放大的存储体数据bdat《4》作为读取数据rdat《4》。优选地,当上拉时,以高电源电压hvdd控制第四存储体mbank《4》的读取数据rdat《4》。

31.随后,将详细描述图1的第一存储体读取放大器100《1》至第四存储体读取放大器100《4》的配置。在这种情况下,第一存储体读取放大器100《1》至第四存储体读取放大器100

《4》可以以相同的形式实现。

32.图2是示出图1的存储体读取放大器100《i》的图(这里,i是大于或等于1且小于或等于4的自然数)。

33.参照图2,存储体读放大器100《i》包括存储体读取放大单元110和存储体读取禁止单元120。

34.存储体读取放大单元110使用高电源电压hvdd作为上拉电压,并且响应于第i个存储体读取放大器使能信号brden《i》而被启用,该第i个存储体读取放大器使能信号brden《i》根据对与存储体读取放大单元110相对应的存储体mbank《i》的选择而被激活。另外,驱动存储体读取放大单元110以差分放大与存储体读取放大单元110相对应的存储体mbank《i》的存储体数据bdat《i》和反相存储体数据/bdat《i》,从而输出读取数据rdat《i》和反相读取数据/radt《i》。在这种情况下,在上拉时,以高电源电压hvdd控制存储体mbank《i》的读取数据rdat《i》和反相读取数据/radt《i》。

35.响应于当未选择存储体mbank《i》时停用的第i个存储体读取放大器使能信号brden《i》,存储体读取禁用单元120控制存储体mbank《i》的读取数据rdat《i》和反相读取数据/radt《i》二者在接地电压vss下被停用。

36.再次参照图1,根据对第一存储体mbank《1》和第二存储体mbank《2》中的一个的选择来启用第一读取驱动器200《1》。

37.也就是说,根据对第一存储体mbank《1》的选择,第一读取驱动器200《1》驱动第一存储体读取放大器100《1》的读取数据rdat《1》,以提供读取数据rdat《1》作为水平数据线lhdat的水平局部数据dath。

38.另外,根据对第二存储体mbank《2》的选择,第一读取驱动器200《1》驱动第二存储体读取放大器100《2》的读取数据rdat《2》,以提供读取数据rdat《1》作为水平数据线lhdat的水平局部数据dath。

39.图3a是示出图1的第一读取驱动器200《1》的详细图。参照图3a,第一读取驱动器200《1》包括第一上拉控制器210、第一下拉控制器220和第一读取驱动器230。

40.第一上拉控制器210接收第一存储体读取放大器100《1》的读取数据rdat《1》和第二存储体读取放大器100《2》的读取数据rdat《2》以生成第一上拉控制信号/xpu1。在这种情况下,根据在逻辑状态“h”下的第一存储体读取放大器100《1》的读取数据rdat《1》和第二存储体读取放大器100《2》的读取数据rdat《2》中的一个的激活,第一上拉控制信号/xpu1在逻辑状态“l”下被激活。

41.第一下拉控制器220接收第一存储体读取放大器100《1》的反相读取数据/rdat《1》和第二存储体读取放大器100《2》的反相读取数据/rdat《2》以生成第一下拉控制信号xpd1。在这种情况下,根据在逻辑状态“h”下的第一存储体读取放大器100《1》的读取数据rdat《1》和第二存储体读取放大器100《2》的读取数据rdat《2》二者的激活,第一下拉控制信号xpd1在逻辑状态“l”下被停用。

42.这里,将更详细地描述第一上拉控制器210和第一下拉控制器220的操作。

43.首先,假设是选择第一存储体mbank《1》的情况。在这种情况下,由于未与第一存储体mbank《1》冗余地选择第二存储体mbank《2》,因此未选择第二存储体mbank《2》。因此,如上所述,在接地电压vss(即,逻辑状态“l”)下控制第二存储体mbank《2》的读取数据rdat《2》和

反相读取数据/rdat《2》。

44.因此,根据第一存储体mbank《1》的读取数据rdat《1》和反相读取数据/rdat《1》,第一上拉控制信号/xpu1和第一下拉控制信号xpd1中的一个被激活。

45.然后,假设是选择第二存储体mbank《2》的情况。在这种情况下,由于未与第二存储体mbank《2》冗余地选择第一存储体mbank《1》,因此未选择第一存储体mbank《1》。因此,在接地电压vss(即,逻辑状态“l”)下控制第一存储体mbank《1》的读取数据rdat《1》和反相读取数据/rdat《1》。

46.因此,根据第二存储体mbank《2》的读取数据rdat《2》和反相读取数据/rdat《2》,第一上拉控制信号/xpu1和第一下拉控制信号xpd1中的一个被激活。

47.响应于在逻辑状态“l”下的第一上拉控制信号/xpu1的激活,第一读取驱动器230以低电源电压lvdd上拉水平数据线lhdat。另外,响应于在逻辑状态“h”下的第一下拉控制信号xpd1的激活,第一读取驱动器230下拉水平数据线lhdat。

48.在具有上述配置的第一读取驱动器200《1》中,根据对第一存储体mbank《1》和第二存储体mbank《2》中的一个的选择,水平局部数据dath具有有效值。在这种情况下,当上拉时,水平局部数据dath被控制在低电源电压lvdd。

49.当第一存储体mbank《1》和第二存储体mbank《2》二者均未被选择时,第一上拉控制信号/xpu1和第一下拉控制信号xpd1均被停用。在这种情况下,水平局部数据dath取决于第二读取驱动器200《2》的操作。

50.再次参照图1,根据对第三存储体mbank《3》和第四存储体mbank《4》中的一个的选择,启用第二读取驱动器200《2》。

51.也就是说,根据对第三存储体mbank《3》的选择,第二读取驱动器200《2》驱动第三存储体读取放大器100《3》的读取数据rdat《3》,以提供读取数据rdat《3》作为水平数据线lhdat的水平局部数据dath。

52.另外,根据对第四存储体mbank《4》的选择,第二读取驱动器200《2》驱动第四存储体读取放大器100《4》的读取数据rdat《4》,以提供读取数据rdat《4》作为水平数据线lhdat的水平局部数据dath。

53.图3b是示出图1的第二读取驱动器200《2》的详细图。参照图3b,第二读取驱动器200《2》包括第二上拉控制器260、第二下拉控制器270和第二读取驱动器280。

54.第二上拉控制器260接收第三存储体读取放大器100《3》的读取数据rdat《3》和第四存储体读取放大器100《4》的读取数据rdat《4》以生成第二上拉控制信号/xpu2。在这种情况下,根据在逻辑状态“h”下的第三存储体读取放大器100《3》的读取数据rdat《3》和第四存储体读取放大器100《4》的读取数据rdat《4》中的一个的激活,第二上拉控制信号/xpu2在逻辑状态“l”下被激活。

55.第二下拉控制器270接收第三存储体读取放大器100《3》的反相读取数据/rdat《3》和第四存储体读取放大器100《4》的反相读取数据/rdat《4》以生成第二下拉控制信号xpd2。在这种情况下,根据在逻辑状态“h”下的第三存储体读取放大器100《3》的读取数据rdat《3》和第四存储体读取放大器100《4》》的读取数据rdat《4》的激活,第二下拉控制信号xpd2在逻辑状态“l”下被停用。

56.这里,将更详细地描述第二上拉控制器260和第二下拉控制器270的操作。

57.首先,假设是选择了第三存储体mbank《3》的情况。在这种情况下,由于未与第三存储体mbank《3》冗余地选择第四存储体mbank《4》,所以未选择第四存储体mbank《4》。因此,第四存储体mbank《4》的读取数据rdat《4》和反相读取数据/rdat《4》二者都被控制在接地电压vss(即,逻辑状态“l”)。

58.因此,根据第三存储体mbank《3》的读取数据rdat《3》和反相读取数据/rdat《3》,第二上拉控制信号/xpu2和第二下拉控制信号xpd2中的一个被激活。

59.然后,假设是选择了第四存储体mbank《4》的情况。在这种情况下,由于未与第四存储体mbank《4》冗余地选择第三存储体mbank《3》,所以未选择第三存储体mbank《3》。因此,读取数据rdat《3》和反相读取数据/rdat《3》的反相读取数据/rdat《3》二者都被控制在接地电压vss(即,逻辑状态“l”)。

60.因此,根据第四存储体mbank《4》的读取数据rdat《4》和反相读取数据/rdat《4》,第二上拉控制信号/xpu2和第二下拉控制信号xpd2中的一个被激活。

61.响应于在逻辑状态“l”下的第二上拉控制信号/xpu2的激活,第二读取驱动器280以低电源电压lvdd上拉水平数据线lhdat。另外,响应于在逻辑状态“h”下的第二下拉控制信号xpd2的激活,第二读取驱动器280下拉水平数据线lhdat。

62.在具有上述配置的第二读取驱动器200《2》中,根据对第三mbank《3》和第四存储体mbank《4》中的一个的选择,水平局部数据dath具有有效值。在这种情况下,当上拉时,水平局部数据dath被控制在低电源电压lvdd。

63.当第三存储体mbank《4和第四存储体mbank《4》二者都未被选择时,第二上拉控制信号/xpu2和第二下拉控制信号xpd2二者均被停用。在这种情况下,水平局部数据dath取决于第一读取驱动器200《1》的操作。

64.再次参考图1,根据对第一存储体mbank《1》至第四存储体mbank《4》中的一个的选择来启用高阻抗300。在这种情况下,高阻抗300驱动水平局部数据dath以输出水平局部数据dath作为垂直数据线lvdat的垂直局部数据datv。这里,当上拉时,垂直局部数据datv被控制在低电源电压lvdd。

65.图4是示出图1的高阻抗300的详细图。参照图4,高阻抗300具体包括水平局部锁存器310和高阻抗驱动器330。

66.水平局部锁存器310锁存从第一读取驱动器200《1》或第二读取驱动器200《2》提供的水平局部数据dath。

67.高阻抗驱动器330响应于高阻抗使能信号hizen而被启用,该高阻抗使能信号hizen根据对第一存储体mbank《1》至第四存储体mbank《4》中的一个的选择在逻辑状态“h”下被激活。

68.在这种情况下,高阻抗驱动器330接收低电源电压lvdd并驱动水平局部数据dath以输出水平局部数据dath作为垂直数据线lvdat的垂直局部数据datv。在这种情况下,当上拉时,水平局部数据dath被控制在低电源电压lvdd。

69.再次参照图1,全局放大器400放大垂直局部数据datv以提供放大的垂直局部数据datv作为全局数据线gdl的全局数据datg。这里,全局数据线gdl电连接到输入/输出缓冲器500。在这种情况下,当上拉时,全局数据datg被控制在高电源电压hvdd。

70.因此,充分开发了从本发明的半导体存储器装置输出的数据段,从而可以顺利地

与外部装置进行通信。

71.图5是示出图1的全局放大器400的详细示图。参照图5,全局放大器400具体包括全局参考电压发生器410、全局放大器420、全局驱动器430、全局重复部件440和全局禁用部件450。

72.响应于在读取操作期间在逻辑状态“h”下激活的初始(preliminary)使能信号pramen,启用全局参考电压发生器410以生成全局参考电压vgrf。

73.响应于在读取操作期间以逻辑状态“h”激活的全局使能信号gamen,启用全局放大器420。在这种情况下,全局放大器420相对于全局参考电压vgrf检测并放大垂直局部数据datv的电压电平,以生成全局初始数据dpg。

74.此处,全局使能信号gamen的激活在初始使能信号pramen的激活发生之后执行。

75.全局驱动器430根据全局初始数据dpg生成全局驱动数据dagd。

76.全局重复部件440锁存并放大全局驱动数据dagd以将全局驱动数据dagd生成为全局数据datg。在这种情况下,当上拉时,全局数据datg被控制在低电源电压lvdd。

77.另外,当禁用时,全局禁用部件450被驱动以在高电源电压hvdd下控制全局初始数据dpg和全局初始数据dpg的反相数据/dpg。因此,全局驱动数据dagd直接保持由全局重复部件440锁存的值。

78.如上所述,在本发明的半导体存储器装置中,当上拉时,第一存储体mbank《1》至第四存储体mbank《4》的存储体数据bdat《1》至bdat《4》和全局数据datg被控制在高电源电压hvdd。因此,从存储体的mbank输出的数据段的损失最小化。另外,当上拉时,提供给输入/输出缓冲器500的全局数据datg也被控制在高电源电压hvdd,从而可以顺利地与外部装置进行通信。

79.同时,在本发明的半导体存储器装置中,存储体mbank与输入/输出缓冲器500之间的数据线被划分为水平数据线lhdat和垂直数据线lvdat。另外,提供高阻抗300以驱动水平数据线lhdat的水平局部数据dath以提供水平局部数据dath作为垂直数据线lvdat的垂直局部数据datv。

80.因此,与其中存储体mbank和输入/输出缓冲器500通过一条数据线连接的半导体存储器装置相比,在本发明的半导体存储器装置中,数据线的负载显著降低。

81.因此,在本发明的半导体存储器装置中,即使将水平局部数据dath和垂直局部数据datv控制在低电源电压lvdd,也几乎不会发生整体工作速度的降低。

82.另外,在本发明的半导体存储器装置中,当上拉时,水平局部数据dath和垂直局部数据datv被控制在低电源电压lvdd,从而减少了数据线中的电流消耗。

83.此外,在本发明的半导体存储器装置中,实现了这样一种结构:第一读取驱动器200《1》由第一存储体mbank《1》和第二存储体mbank《2》共享,并且第二读取驱动器200《2》由第三存储体mbank《3》和第四存储体mbank《4》共享。

84.因此,根据本发明的半导体存储器装置,显著减小了总体布局面积。

85.根据具有上述结构的本发明的半导体存储器装置,每个存储体与输入/输出缓冲器之间的数据线被分为水平数据线和垂直数据线。提供高阻抗驱动器以驱动水平数据线的水平局部数据,以提供将水平局部数据作为垂直数据线的垂直局部数据。因此,根据本发明的半导体存储器装置,即使将水平局部数据和垂直局部数据控制在低电源电压下,也几乎

不会发生整体工作速度的降低。另外,根据本发明的半导体存储器装置,大大减少了数据线中的电流消耗。

86.对于本领域技术人员显而易见的是,在不脱离本发明的精神或范围的情况下,可以对本发明的上述示例性实施方式进行各种修改。因此,本发明旨在涵盖所有这些修改,只要它们落入所附权利要求及其等同物的范围内即可。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。