1.本发明涉及半导体技术领域,具体涉及一种半导体器件和半导体器件的制备方法。

背景技术:

2.现有dram的晶体管与电容器之间导线连接方法为多晶硅-金属插头式连接,当制程微缩时,其尺寸随之微缩,多晶硅-金属之间的联结电阻和接触面表现显得非常重要。随着制程微缩,位线越高的深宽比沟槽填充多晶硅越容易出现多晶硅中留有空洞的情况,极大的增大导线阻值。为了消除空洞缝隙的影响,通常采用沉积-刻蚀-沉积的方法来解决空洞缝隙带来的影响,但是采用在对多晶硅层进行刻蚀时,空洞缝隙被蚀刻开,刻蚀溶液和刻蚀气体进入空洞缝隙内,使得位于空洞缝隙处的多晶硅层刻蚀较快,在填充层的表面形成了v形界面,v形界面会形成一层大面积的天然氧化硅面,极大影响了半导体器件的导电。

技术实现要素:

3.本发明的目的在于提供一种半导体器件的制备方法,能够避免形成v形氧化硅面,提高半导体器件的导电性。

4.为解决上述技术问题,本发明中提供了一种半导体器件的制备方法。

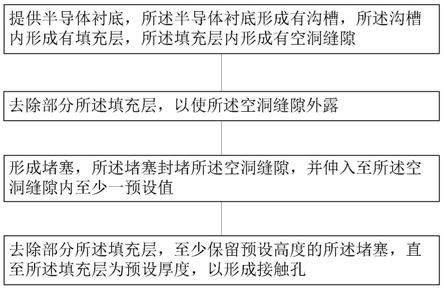

5.根据本发明实施例的半导体器件的制备方法包括:提供半导体衬底,所述半导体衬底形成有沟槽,所述沟槽内形成有填充层,所述填充层内形成有空洞缝隙;去除部分所述填充层,以使所述空洞缝隙外露;形成堵塞,所述堵塞封堵所述空洞缝隙,并伸入至所述空洞缝隙内至少一预设值;去除部分所述填充层,至少保留预设高度的所述堵塞,直至所述填充层为预设厚度,以形成接触孔。

6.根据本发明的一些实施例,所述堵塞采用氮化硅材料形成。

7.根据本发明的一些实施例,所述堵塞伸入所述空洞缝隙的深度h与所述空洞缝隙深度h满足2/3h≤h≤3/4h。

8.根据本发明的一些实施例,形成所述堵塞的步骤包括:于所述填充层表面和所述空洞缝隙内沉积氮化硅材料层;去除位于所述填充层表面的氮化硅材料层;保留位于所述空洞缝隙内的氮化硅材料以形成所述堵塞。

9.可选地,在去除部分所述填充层,以使所述空洞缝隙外露之后,在于所述填充层的表面和所述空洞缝隙内沉积氮化硅材料之前,还包括以下步骤:部分去除所述沟槽侧壁。

10.可选地,采用低压化学气相沉积法或原子层沉积法沉积氮化硅材料。

11.根据本发明的一些实施例,在去除部分所述填充层,至少保留预设高度的所述堵塞,直至所述填充层为预设厚度以形成所述接触孔之后还包括以下步骤:去除所述堵塞;于所述接触孔内形成导线连接结构,所述导线连接结构包括粘附层、第一导电层和第二导电层。

12.可选地,所述粘附层为金属硅化物层。

13.可选地,所述粘附层为硅化钴层或硅化镍层。

14.可选地,在于所述接触孔内形成导线连接结构中包括以下步骤;于所述填充层表面形成所述粘附层;于所述粘附层表面和所述接触孔侧面形成所述第一导电层;于所述第一导电层表面形成所述第二导电层以填充所述接触孔。

15.可选地,在于所述填充层表面形成所述粘附层的步骤中包括:于所述填充层的表面溅射金属材料,并进行快速热退火工艺以在所述填充层的表面形成所述粘附层。

16.可选地,所述第一导电层为氮化钛层,所述第二导电层为金属钨层。

17.根据本发明的一些实施例,所述半导体衬底包括基底和形成在所述基底上方的支撑层,所述支撑层内形成有所述沟槽。

18.根据本发明的一些实施例,所述填充层为多晶硅层。

19.本发明还提出了一种半导体器件,包括:半导体衬底,所述半导体衬底上形成有支撑层,所述支撑层内形成有沟槽;填充层,所述填充层部分填充所述沟槽且所述填充层的厚度a和所述沟槽的深度b满足:1/3b≤a≤1/2b;粘附层,所述粘附层形成在所述填充层的表面且位于所述沟槽内;第一导电层和第二导电层,所述第一导电层形成在所述粘附层表面和所述支撑层表面,所述第二导电层形成在所述第一导电层内且填充所述沟槽。

20.根据本发明的一些实施例,还包括氮化硅膜,所述填充层内形成有空洞缝隙,所述氮化硅膜形成在所述空洞缝隙的内壁面上。

21.根据本发明的一些实施例,所述半导体器件还包括位线结构,所述位线结构形成在所述基底表面且位于所述支撑层内。

22.可选地,所述半导体器件还包括:氧化物层,氧化物层形成在所述支撑层内且位于所述位线结构的两侧。

23.本发明还提出了一种半导体器件,包括半导体衬底,所述半导体衬底上形成有支撑层,所述支撑层内形成有沟槽;填充层,所述填充层部分填充所述沟槽且所述填充层内形成有空洞缝隙;堵塞,所述堵塞形成在所述沟槽内且至少部分伸入至所述空洞缝隙内。

24.根据本发明的一些实施例,所述堵塞伸入所述空洞缝隙的深度h与所述空洞缝隙深度h满足2/3h≤h≤3/4h

附图说明

25.图1-图12为根据本发明一个实施例的半导体器件的制备方法的形成过程结构示意图;

26.图13-图24是根据本发明另一个实施例的半导体器件的制备方法的形成过程结构示意图;

27.图25是根据本发明实施例的半导体器件的制备方法的流程图。

28.附图标记:

29.100:半导体器件;

30.1:半导体衬底,11:基底,12:氧化硅层,13:支撑层,14:沟槽,15:接触孔;

31.2:填充层,21:空洞缝隙;

32.3:氮化硅材料层,31:堵塞;

33.4:粘附层;

34.5:导线连接结构,51:第一导电层,52:第二导电层;

35.6:位线结构,61:第一位线层,62:第二位线层;

36.7:氧化物层。

具体实施方式

37.以下结合附图和具体实施方式对本发明提出的一种半导体器件100的制备方法和半导体器件100作进一步详细说明。

38.下面参考附图描述根据本发明实施例的半导体器件100的制备方法。

39.如图25所示,根据本发明实施例的半导体器件100的制备方法可以包括:提供半导体衬底1,半导体衬底1形成有沟槽14,沟槽14内形成有填充层2,填充层2内形成有空洞缝隙21;去除部分填充层2,以使空洞缝隙21外露;形成堵塞31,堵塞31封堵空洞缝隙21,并深入至空洞缝隙21内至少一预设值;去除部分填充层2,至少保留预设高度的堵塞31,直至填充层2为预设厚度,以形成接触孔15。

40.如图1所示,提供半导体衬底1,半导体衬底1可以包括基底11、氧化硅层12和支撑层13,其中,氧化硅层12形成在基底11内,支撑层13形成在氧化硅层12和基底11的表面,通过刻蚀工艺在支撑层13内形成沟槽14,以暴露基底11,以便于在沟槽14内填充填充层2。

41.其中基底11材料可以为硅(si)、锗(ge)、硅锗(gesi)、或碳化硅(sic);也可以是绝缘体上硅(soi),绝缘体上锗(goi);或者还可以为其它的材料,例如砷化镓等

ⅲ-ⅴ

族化合物。支撑层13可以为氮化物层,例如可以为氮化硅层。

42.如图1-图24所示,半导体衬底1还可以包括位线结构6,位线结构6形成在氧化硅层12表面上且位于支撑层13内,支撑层13包括位线结构6,位线结构6可以包括层叠设置的第一位线层61和第二位线层62,其中第一位线层61可以为氮化钛层,第二位线层62可以为金属钨层,第二位线层62位于第一位线层61的上方。在本发明的另一些示例中,如图13-图24所示,半导体衬底1还可以包括氧化物层7,氧化物层7形成在氧化硅层12上方且位于支撑层13内,并形成在位线结构6的两侧。其中氧化物层7可以为氧化硅层,如图13-图24所示的半导体衬底1的结构为n-o-n结构,也就是说位线结构6的保护层设置为氮化硅-氧化硅硅-氮化硅的叠层结构。

43.如图2和图14所示,于支撑层13表面和沟槽14内沉积填充层2,填充层2填满沟槽14,填充层2可以为多晶硅层,对于填充层2的形成方法而言,填充层2可以采用化学气相沉积法或低压化学气相沉积法等形成,或者填充层2也可以采用其他的阶梯式覆盖填充法,其中填充层2还可以掺杂含砷元素、硼元素、磷元素、碳元素等或者多种元素混合掺杂,对于掺杂方法,可以是原位掺杂,也可以是通过植入或混合掺杂加入掺杂元素。

44.由于沟槽14具有一定的深度,在进行沉积时,填充层2内容易形成空洞缝隙21,空洞缝隙21的产生极大增加了半导体器件100的导线阻值。因此需要消除或减小空洞缝隙21以减小半导体器件100的导线阻值。可选地,在沉积填充层2之前,可先种种子层然后大量沉积填充层2,种子层形成致密且晶粒较小,这样在进行阶梯式覆盖形成填充层2时,也能够减小空洞缝隙21的形成。

45.如图3和图15所示,去除部分填充层2,以使空洞缝隙21外露,具体地,可对填充层2进行轻微的凹口蚀刻,去除顶部的部分填充层2以打开空洞缝隙21,对于去除的填充层2的

厚度,只要能够露出空洞缝隙21即可。如图5-图6以及图17-图18所示,形成堵塞31,堵塞31封堵空洞缝隙21,并伸入至空洞缝隙21内至少一预设值,这样通过形成堵塞31,再对填充层2进行刻蚀,从而能够避免在刻蚀过程中刻蚀溶液或刻蚀气体进入空洞缝隙21内,进而可避免形成v形界面。其中堵塞31可以由氮化硅材料形成。

46.如图4和图16所示,去除部分填充层2后,在沟槽14的上部形成有去除部分填充层2后形成的凹槽,去除部分沟槽14侧壁,即去除于凹槽对应的部分支撑层13侧壁,其中去除的部分支撑层13侧壁的高度与去除的部分填充层2相对应,这样在沉积形成堵塞31时,若未去除部分沟槽14侧壁,则沉积材料沉积在沟槽14侧壁处,容易使得沟槽14上部的开口缩小,导致沟槽14侧壁的沉积材料遮盖了其底部的填充层2,这样在后续对填充层2进行刻蚀时容易导致部分填充层2无法刻蚀。若去除部分沟槽14侧壁,沉积形成堵塞31时,沉积材料同时沉积形成在沟槽14侧壁处以填补去除的沟槽14侧壁,同时也能够避免遮挡其下方的填充层2。

47.其中在去除部分沟槽14侧壁时可采用湿法刻蚀,具体可采用氢氟酸、磷酸或两者的混合酸等能够对支撑层13进行蚀刻且对填充层2能够选择性蚀刻的蚀刻化学溶液,例如支撑层13材料为氮化物,填充层2材料为多晶硅,则湿法刻蚀的刻蚀溶液能够刻蚀氮化物,同时能够对多晶硅材料进行选择性刻蚀且对多晶硅材料的刻蚀速率较低。

48.下面参考附图5-图6以及图17-图18所示描述形成堵塞31的形成方法。形成堵塞31的步骤可以包括:于填充层2表面和空洞缝隙21内沉积氮化硅材料层3,去除位于填充层2表面的氮化硅材料层3;保留位于空洞缝隙21内的氮化硅材料以形成堵塞31。这样通过沉积氮化硅材料能够填充暴露的空洞缝隙21,并在填充层2蚀刻过程中将堵塞31作为蚀刻塞封堵空洞缝隙21,以消除填充层2的v形界面的形成,提高半导体器件100的性能。

49.具体地如图5和图17所示,在填充层2表面和空洞缝隙21内沉积氮化硅材料层3,沉积方法可以为低压化学气相沉积法或原子层沉积。氮化硅材料层3沉积形成在填充层2的上表面,由于空洞缝隙21打开暴露,这样,氮化硅材料层3能够部分沉积在空洞缝隙21内,但由于空洞缝隙21细小狭长,氮化硅材料无法完全填满整个空洞缝隙21,可形成在空洞缝隙21的上部以封堵空洞缝隙21的开口。

50.如图6和图18所示,去除位于填充层2表面的氮化硅材料层3,保留位于空洞缝隙21内的氮化硅材料以形成堵塞31,其中堵塞31位于空洞缝隙21的深度h与空洞缝隙21的深度h满足2/3h≤h≤3/4h,也就是说,此时位于空洞缝隙21内的堵塞31的高度为空洞缝隙21总高度的三分之二到四分之三。

51.如图7和图19所示,在形成堵塞31后,对剩余填充层2进行蚀刻,此时堵塞31封堵了空洞缝隙21,在对填充层2进行蚀刻时,能够避免蚀刻溶液或者气体进入空洞缝隙21内。其中可采用干法蚀刻等工艺去除填充层2至目标深度,具体地可采用sf6/cf4/cl2/ar等气体中的一种或多种混合蚀刻。由于多晶硅材料和氮化物材料的刻蚀速率不同,在对填充层2进行蚀刻时,氮化物的刻蚀速率小于多晶硅的刻蚀速率,堵塞31相对填充层2刻蚀较慢,从而堵塞31相对填充层2上表面突出,这样堵塞31能够始终封堵空洞缝隙21。对于填充层2刻蚀深度,可将填充层2刻蚀至堵塞31的下端为止,即可将填充层2刻蚀至填充层2的上表面不低于堵塞31的下表面即可,以避免填充层2过刻蚀导致空洞缝隙21暴露。进一步地,剩余填充层2的高度可以为沟槽14深度的二分之一到三分之二,这样,不仅便于在填充层2上方形成导线连接结构5,也能够尽量减小剩余填充层2的高度以减小其内的空洞缝隙21。

52.如图8-图9以及图20-图21所示,去除堵塞31,以便于在沟槽14内形成导线连接结构5,也避免堵塞31影响半导体器件100的导电性。在本发明的一些示例中,由于堵塞31体积较小,可采用刻蚀工艺直接刻蚀去除。在本发明的另一些示例中,如图8和图20所示,可在填充层2表面沉积氮化物材料以覆盖填充层2上表面,然后如图9和图21所示,通过干法刻蚀或者湿法刻蚀去除沉积的氮化硅材料和堵塞31,这样,不仅便于蚀刻堵塞31,而且在蚀刻过程中也能够避免刻蚀剂腐蚀沟槽14侧壁,能够保护沟槽14侧壁。

53.如图10-图12以及图22-图24所示,于接触孔15内形成导线连接结构5,导线连接结构5包括粘附层4、第一导电层51和第二导电层52,其中粘附层4形成在填充层2表面,第一导电层51形成在粘附层4表面和沟槽14侧壁,第二导电层52形成在第一导电层51内且填充接触孔15,即第一导电层51形成为u形结构且包裹第二导电层52,粘附层4、第一导电层51和第二导电层52填满接触孔15。

54.粘附层4不仅能够粘附其上方的第一导电层51和其下方的填充层2,以提高结构稳定性,同时粘附层4具有良好的导电作用,能够降低导线连接结构5的电阻电抗。可选地,粘附层4的材料可以为金属硅化物,例如,粘附层4材料可以为硅化钴或者硅化镍等。

55.下面参考图10-图12以及图22-图24所示描述导线连接结构5的形成方法,导线连接结构5的形成步骤,可以包括:

56.如图10和图22所示,于填充层2表面形成粘附层4;具体地,可在填充层2表面溅射金属钴或者金属镍,然后经过快速退火工艺,推动金属钴或者镍与底部填充层2进行反应,然后通过amp或spm湿法去除未反应的金属钴或镍以在填充层2表面形成金属硅化物。

57.如图11和图23所示,于粘附层4表面和接触孔15侧面形成第一导电层51;如图12和图24所示,于第一导电层51表面形成第二导电层52以填充接触孔15。具体地,接触孔15形成在粘附层4上方,第一导电层51覆盖支撑层13的上表面、接触孔15侧面和粘附层4上表面,第二导电层52形成在第一导电层51表面且与第一导电层51填满接触孔15以形成导线连接结构5。其中第一导电层51可以形成为阻挡层,从而能够防止第二导电层52的金属扩散,进一步地,在形成第二导电层52的过程中,第二导电层52材料的前驱体可以为氯化物,氯化物分解会产生氯离子,通过第一导电层51也能够防止第二导电层52形成过程中氯离子的扩散,例如第一导电层51可以为氮化钛材料,第二导电层52可以为金属钨层,在填充金属钨的过程中,会用到前驱体六氯化钨,六氯化钨解离会产生氯离子,通过第一导电层51能够防止氯离子扩散。

58.下面参考附图描述根据本发明实施例的半导体器件100。

59.如图12和图24所示,半导体器件100可以包括半导体衬底1、填充层2、粘附层4、第一导电层51和第二导电层52。

60.半导体衬底1可以包括基底11、氧化硅层12和形成在氧化硅层12上方的支撑层13,支撑层13内通过图像化形成有沟槽14,沟槽14暴露其下方的基底11表面。填充层2形成在沟槽14内,填充层2部分填充沟槽14,其中填充层2的厚度a和沟槽14的深度b满足:1/3b≤a≤1/2b,即填充层2的高度可以为沟槽14深度的三分之一倍到二分之一倍。

61.粘附层4形成在填充层2表面且位于沟槽14内,第一导电层51形成在粘附层4表面、沟槽14侧壁和支撑层13表面,第二导电层52形成在第一导电层51内且填充沟槽14。粘附层4不仅能够粘附其上方的第一导电层51和其下方的填充层2,以提高结构稳定性,同时粘附层

4具有良好的导电作用,能够降低导线连接结构5的电阻电抗。可选地,粘附层4的材料可以为金属硅化物,例如,粘附层4材料可以为硅化钴或者硅化镍等,支撑层13材料可以为氮化硅,填充层2材料可为多晶硅。第一导电层51的材料可以为氮化钛,第二导电层52的材料可以为金属钨材料。

62.如图12和图24所示,半导体器件100还可以包括位线结构6,位线结构6形成在基底11表面且位于支撑层13内,位线结构6可以包括层叠设置的第一位线层61和第二位线层62,其中第一位线层61可以为氮化钛层,第二位线层62可以为金属钨层,第二位线层62位于第一位线层61的上方。在本发明的一些示例中,如图24所示,半导体衬底1还可以包括氧化物层7,氧化物层7形成在氧化硅层12的上方且位于支撑层13内,并形成在位线结构6的两侧,其中氧化物层7可以为氧化硅层。

63.如图12和图24所示,半导体器件100还可以包括氮化硅膜,填充层2内形成有空洞缝隙21,空洞缝隙21的深度小于填充层2的深度,氮化硅膜形成在空洞缝隙21的内壁面上,从而这样在对填充层2进行刻蚀时能够减小刻蚀溶液或气体对填充层2形成空洞缝隙21的侧壁的刻蚀损伤。

64.本发明还提出了一种半导体器件100。如图6所示和图18所示,根据本发明实施例的半导体器件100可以包括半导体衬底1、填充层2和堵塞31。

65.半导体衬底1可以包括基底11、氧化硅层12和形成在氧化硅层12上方的支撑层13,支撑层13内通过图像化形成有沟槽14,沟槽14暴露其下方的基底11表面。填充层2形成在沟槽14内,填充层2部分填充沟槽14。

66.堵塞31形成在沟槽14内且至少部分伸入空洞缝隙21内,这样,通过堵塞31能够封堵空洞缝隙21,在后续对填充层2进行刻蚀时,能够避免刻蚀溶液或气体进入空洞缝隙21内,进而能够避免在后续中填充层2表面形成v形界面而影响半导体器件100的性能。

67.其中堵塞31位于空洞缝隙21的深度h与空洞缝隙21的深度h满足2/3h≤h≤3/4h,也就是说,此时位于空洞缝隙21内的堵塞31的高度为空洞缝隙21总高度的三分之二到四分之三,由此沉积堵塞31时能够使得堵塞31填充部分空洞缝隙21以封堵空洞缝隙21的开口,而在后续填充层2刻蚀以形成沉积导线连接结构5的接触孔15时,能够保证在在填充层2刻蚀至目标深度之前避免空洞缝隙21暴露导致刻蚀溶液或气体进入空洞缝隙21,以避免形成v形界面而降低半导体器件100的性能。

68.以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。