1.本发明涉及一种半导体元件及其制作方法,尤其是涉及一种磁阻式随机存取存储器(magnetoresistive random access memory,mram)及其制作方法。

背景技术:

2.已知,磁阻(magnetoresistance,mr)效应是材料的电阻随着外加磁场的变化而改变的效应,其物理量的定义,是在有无磁场下的电阻差除上原先电阻,用以代表电阻变化率。目前,磁阻效应已被成功地运用在硬盘生产上,具有重要的商业应用价值。此外,利用巨磁电阻物质在不同的磁化状态下具有不同电阻值的特点,还可以制成磁性随机存储器(mram),其优点是在不通电的情况下可以继续保留存储的数据。

3.上述磁阻效应还被应用在磁场感测(magnetic field sensor)领域,例如,移动电话中搭配全球定位系统(global positioning system,gps)的电子罗盘(electronic compass)零组件,用来提供使用者移动方位等信息。目前,市场上已有各式的磁场感测技术,例如,各向异性磁阻(anisotropic magnetoresistance,amr)感测元件、巨磁阻(gmr)感测元件、磁隧穿结(magnetic tunneling junction,mtj)感测元件等等。然而,上述现有技术的缺点通常包括:较占芯片面积、制作工艺较昂贵、较耗电、灵敏度不足,以及易受温度变化影响等等,而有必要进一步改进。

技术实现要素:

4.本发明一实施例揭露一种制作半导体元件的方法。首先形成一第一金属间介电层于基底上,然后形成一第一图案化掩模于第一金属间介电层上,其中第一图案化掩模包含一第一开口沿着一第一方向延伸。接着形成一第二图案化掩模于第一图案化掩模上,其中第二图案化掩模包含一第二开口沿着一第二方向延伸并与该第一开口交错而形成一第三开口,之后再形成一第一金属内连线于第三开口内。

5.本发明另一实施例揭露一种半导体元件,其主要包含一金属内连线设于一基底上且该金属内连线依据上视角度包含一四边形以及一磁性隧穿结(magnetic tunneling junction,mtj)设于金属内连线上,其中mtj依据上视角度包含一圆弧形。

附图说明

6.图1为本发明一实施例制作一mram单元的俯视图;

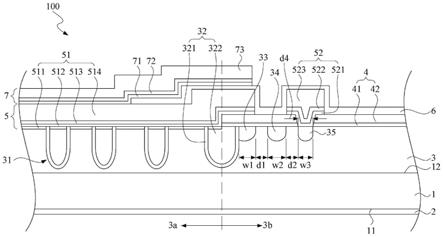

7.图2至图5为本发明一实施例沿着图1中切线aa’方向制作mram单元的方法示意图;

8.图6为本发明图5中mtj重叠金属内连线的一实施例的上视图;

9.图7为本发明图5中mtj重叠金属内连线的一实施例的上视图;

10.图8为本发明图5中mtj重叠金属内连线的一实施例的上视图。

11.主要元件符号说明

12.12:基底

13.14:mram区域

14.16:层间介电层

15.18:金属内连线结构

16.20:金属间介电层

17.22:金属内连线

18.24:金属间介电层

19.26:第一图案化掩模

20.28:第二图案化掩模

21.30:第一开口

22.32:第二开口

23.34:第三开口

24.36:接触洞

25.38:金属内连线

26.42:下电极

27.44:固定层

28.46:阻障层

29.48:自由层

30.50:上电极

31.52:mtj

32.56:遮盖层

33.58:金属间介电层

34.60:金属内连线

35.62:停止层

具体实施方式

36.请参照图1至图5,图1为本发明一实施例制作一半导体元件,或更具体而言一mram单元的俯视图,图2至图5则为本发明一实施例沿着图1中切线aa’方向制作mram单元的方法示意图。如图1至图2所示,首先提供一基底12,例如一由半导体材料所构成的基底12,其中半导体材料可选自由硅、锗、硅锗复合物、硅碳化物(silicon carbide)、砷化镓(gallium arsenide)等所构成的群组,且基底12上较佳定义有一mram区域14以及一逻辑区域(图未示)。

37.基底12上可包含例如金属氧化物半导体(metal-oxide semiconductor,mos)晶体管等主动(有源)元件、被动(无源)元件、导电层以及例如层间介电层(interlayer dielectric,ild)16等介电层覆盖于其上。更具体而言,基底12上可包含平面型或非平面型(如鳍状结构晶体管)等mos晶体管元件,其中mos晶体管可包含栅极结构(例如金属栅极)以及源极/漏极区域、间隙壁、外延层、接触洞蚀刻停止层等晶体管元件,层间介电层16可设于基底12上并覆盖mos晶体管,且层间介电层16可具有多个接触插塞电连接mos晶体管的栅极以及/或源极/漏极区域。由于平面型或非平面型晶体管与层间介电层等相关制作工艺均为本领域所熟知技术,在此不另加赘述。

38.然后于层间介电层16上依序形成金属内连线结构18电连接前述的接触插塞,其中金属内连线结构18包含一金属间介电层20、一选择性停止层(图未示)以及金属内连线22镶嵌于金属间介电层20中。在本实施例中,金属内连线结构18中的金属内连线22较佳包含一沟槽导体(trench conductor),其中金属内连线结构18中的各金属内连线22均可依据单镶嵌制作工艺或双镶嵌制作工艺镶嵌于金属间介电层20以及/或停止层中并彼此电连接。例如各金属内连线22可更细部包含一阻障层以及一金属层,其中阻障层可选自由钛(ti)、氮化钛(tin)、钽(ta)以及氮化钽(tan)所构成的群组,而金属层可选自由钨(w)、铜(cu)、铝(al)、钛铝合金(tial)、钴钨磷化物(cobalt tungsten phosphide,cowp)等所构成的群组,但不局限于此。由于单镶嵌或双镶嵌制作工艺是本领域所熟知技术,在此不另加赘述。此外在本实例中金属内连线22中的金属层较佳包含铜,金属间介电层20较佳包含氧化硅或超低介电常数介电层,而停止层则可包含氮掺杂碳化物层(nitrogen doped carbide,ndc)、氮化硅、或氮碳化硅(silicon carbon nitride,sicn),但不局限于此。

39.然后形成金属间介电层24于金属间介电层20以及金属内连线22上,再依序形成第一图案化掩模26于金属间介电层24上以及第二图案化掩模28于第一图案化掩模26上。在本实施例中,第一图案化掩模26较佳包含一金属掩模其可由例如钛或氮化钛所构成而第二图案化掩模28则较佳包含一图案化光致抗蚀剂。

40.需注意的是,第一图案化掩模26较佳为图1中沿着第一方向例如x方向延伸的多个长条形掩模图案且第一图案化掩模26的多个长条形掩模图案之间包含多个第一开口30同样沿着一第一方向延伸,其中第一开口30边缘约略切齐下方设于金属间介电层20内的金属内连线22边缘。第二图案化掩模28则较佳为图1中沿着第二方向例如y方向延伸的多个长条形掩模图案且第二图案化掩模28的多个长条形掩模图案之间包含多个第二开口32同样沿着第二方向延伸并与第一开口30相互交错。

41.整体来看,图1中沿着x方向延伸由约略长方形虚线所构成的部分较佳为第一图案化掩模26而沿着y方向延伸的同样由约略长方形虚线所构成的部分则为第二图案化掩模28的第二开口32。值得注意的是,本实施例中的第一开口30及第二开口32较佳相互交错并于交错处形成多个呈现约略正方形的第三开口34,其中各第三开口34即定义出后续用来连接金属内连线22的另一金属内连线位置且第三开口34边缘较佳切齐下方的金属内连线22边缘。

42.如图3所示,接着利用第一图案化掩模26以及第二图案化掩模28为掩模以蚀刻方式去除第三开口34内的金属间介电层24以形成接触洞36暴露出下面的金属内连线22。由于接触洞36为第三开口34的延伸因此其边缘也较佳切齐下方的金属内连线22边缘。

43.然后如图4所示,可先去除由光致抗蚀剂材料所构成的第二图案化掩模28,再于接触洞36中填入所需的金属材料,例如包含钛(ti)、氮化钛(tin)、钽(ta)、氮化钽(tan)等的阻障层材料以及选自钨(w)、铜(cu)、铝(al)、钛铝合金(tial)、钴钨磷化物(cobalt tungsten phosphide,cowp)等低电阻材料或其组合的低阻抗金属层。接着进行一平坦化制作工艺,例如以化学机械研磨(chemical mechanical polishing,cmp)制作工艺去除部分金属材料以及第一图案化掩模26以形成接触插塞或金属内连线38于接触洞36内电连接金属内连线22。

44.如图5所示,接着形成一mtj堆叠结构(图未示)于金属内连线38及金属间介电层24

上。在本实施例中,形成mtj堆叠结构的方式可先依序形成一下电极42、一固定层(fixed layer)44、一阻障层(barrier layer)46、一自由层(free layer)48以及一上电极50。在本实施例中,下电极42以及上电极50较佳包含导电材料例如但不局限于钽(ta)、铂(pt)、铜(cu)、金(au)、铝(al)。固定层44可包含铁磁性材料例如但不局限于钴铁硼(cobalt-iron-boron,cofeb)、钴铁(cobalt-iron,cofe)、铁(fe)、钴(co)等,用以固定或限制邻近层的磁矩方向。阻障层46可由包含氧化物的绝缘材料所构成,例如氧化铝(alo

x

)或氧化镁(mgo),但均不局限于此。自由层48可以是由铁磁性材料所构成者,例如铁、钴、镍或其合金如钴铁硼(cobalt-iron-boron,cofeb),镍铁(nickel-iron,nife)等,但不限于此。其中,自由层48的磁化方向会受外部磁场而「自由」改变。

45.随后利用一图案化掩模(图未示)为掩模进行一道或一道以上蚀刻制作工艺去除部分mtj堆叠结构以形成mtj 52于金属内连线38上,其中各mtj 52下方设有下电极42而mtj 52上方则设有上电极50。值得注意的是,本实施例于图案化上述mtj堆叠结构及金属间介电层24所进行的蚀刻制作工艺可包含反应性离子蚀刻制作工艺(reactive ion etching,rie)以及/或离子束蚀刻制作工艺(ion beam etching,ibe),由于离子束蚀刻制作工艺的特性,剩余的金属间介电层24上表面较佳略低于金属内连线38上表面且金属间介电层24上表面较佳呈现一弧形或曲面。

46.然后形成一遮盖层56于mtj 52上并覆盖金属间介电层24表面,一金属间介电层58于遮盖层56上,再进行一道或一道以上光刻暨蚀刻制作工艺去除部分金属间介电层58及部分遮盖层56形成接触洞(图未示)。接着填入导电材料于各接触洞内并搭配平坦化制作工艺如cmp以形成金属内连线60连接下方的上电极50。最后再形成另一停止层62于金属间介电层58上并覆盖金属内连线60。

47.在本实施例中,遮盖层56较佳包含氮化硅,但又可依据制作工艺需求选用其他介电材料,例如又可包含氧化硅、氮氧化硅或氮碳化硅。停止层62可选自由氮掺杂碳化物层(nitrogen doped carbide,ndc)、氮化硅、以及氮碳化硅(silicon carbon nitride,sicn)所构成的群组且又最佳包含氮碳化硅。如同前述所形成的金属内连线,设于金属间介电层58内的各金属内连线60均可依据单镶嵌制作工艺或双镶嵌制作工艺镶嵌于金属间介电层内。例如各金属内连线60可更细部包含一阻障层以及一金属层,其中阻障层可选自由钛(ti)、氮化钛(tin)、钽(ta)以及氮化钽(tan)所构成的群组,而金属层可选自由钨(w)、铜(cu)、铝(al)、钛铝合金(tial)、钴钨磷化物(cobalt tungsten phosphide,cowp)等所构成的群组,但不局限于此。由于单镶嵌或双镶嵌制作工艺是本领域所熟知技术,在此不另加赘述。至此即完成本发明一实施例的半导体元件的制作。

48.请继续参照图6至图8,图6至图8为本发明图5中mtj 52重叠金属内连线38的不同实施例的上视图。如图6至图8所示,本实施例包含由钨所构成的金属内连线38设于mram区域14以及mtj 52设于金属内连线38正上方且mtj 52底部经由下电极42接触金属内连线38顶部。从上视角度来看,金属内连线38的上视剖面包含一四边形或矩形而mtj 52的上视剖面则包含一圆弧形重叠金属内连线38的矩形但不接触或超过矩形边缘,其中金属内连线38由于是以两道图案化掩模交错的开口所形成因此其形状较佳为矩形例如图6所示的正方形或图7所示的长方形,而mtj 52则以ibe等蚀刻方式形成因此其形状可包含图6所示的正圆形或图7所示的椭圆形。需注意的是,本实施例图6虽以正方形的金属内连线38搭配圆形的

mtj 52而图7则以长方形的金属内连线38搭配椭圆形的mtj 52,但不局限于这两个组合,依据本发明其他实施例又可依据制作工艺需求任意搭配金属内连线38以及mtj 52的形状以形成例如正方形金属内连线38与椭圆形mtj 52的上视组合或长方形金属内连线38与圆形mtj 52的上视组合,这些变化型均属本发明所涵盖的范围。

49.此外如图8所示,相较于图6至图7的实施例中mtj 52均完全设于金属内连线38的边界内且不超过金属内连线38的任何边界,依据本发明另一实施例又可调整mtj 52的大小或位置将mtj 52的圆形或椭圆形形状略微超出金属内连线38的边界范围,使mtj 52重叠金属内连线38的至少一边缘例如单一边缘、二边缘、三边缘甚至四边缘,这些变化型均属本发明所涵盖的范围。

50.综上所述,本发明主要先形成第一金属间介电层于基底上,然后形成第一图案化掩模于第一金属间介电层上且第一图案化掩模包含一第一开口沿着一第一方向延伸。接着形成一第二图案化掩模于第一图案化掩模上,其中第二图案化掩模包含一第二开口沿着一第二方向延伸并与该第一开口交错而形成一第三开口,之后再形成一金属内连线于第三开口内并于金属内连线上形成mtj。依据本发明的优选实施例利用上述双层图案化掩模的方式来制备mram元件可在存储器元件尺寸越缩越小以及制作工艺空间(process window)越变越窄的情况下于mtj正下方制备出具有更小线宽的金属内连线。

51.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。