调制器电路、对应的设备及方法

1.相关申请的交叉引用

2.本技术要求2020年6月16日提交的意大利专利申请第102020000014302号的优先权,该申请通过引用结合于此。

技术领域

3.本说明书涉及脉宽调制(pwm)调制器电路。例如,可以在高频pwm调制器中应用一个或多个实施例。一个或多个实施例可以有利地应用在d类音频功率放大器中。

背景技术:

4.现今,d类功率放大器的切换频率有明显的提高趋势。

5.d类(或切换)放大器的操作涉及电子开关经由使用脉宽调制(pwm)或相关技术的调制器交替接通和断开(即,使其导通和非导通),以将(音频)输入信号编码成脉冲串。经由诸如lc滤波器的低通滤波器来恢复(解调)放大的信号,以应用于例如扬声器。

6.高切换频率可有助于降低lc解调滤波器的成本。

7.然而,高切换频率会有可能的后果,例如由于切换斜率的增加而引起的干扰的增加,并且在很大程度上丧失了同相调制相对于异相调制的好处。

8.因此,改进的pwm调制器具有增强的抗扰动鲁棒性和减小的面积/电流消耗对于各种应用是理想的。

技术实现要素:

9.一个或多个实施例的目的是有助于提供这种改进的解决方案。

10.根据一个或多个实施例,这样的目的可以通过具有所附权利要求中所述的特征的电路来实现。

11.一个或多个实施例可涉及对应的设备。在音频系统中使用的d类功率放大器可以是这种设备的示例。

12.一个或多个实施例可涉及对应的方法。

13.权利要求是本文提供的关于实施例的技术教导的组成部分。

14.一个或多个实施例可以提供一种改进的全差分pwm调制器,其表现出对干扰的增强的鲁棒性和减小的面积/电流规格。

15.一个或多个实施例可以表现出以下优点中的一个或多个:由于扩展使用全差分电路装置,提高了对共模噪声的抗扰度;作用于比较器的输入阻抗的可能性有助于创建开环极点和零点:可以在参考信号的顶部(顶点)创建峰值,这些峰值不一定是“平方”的,并且呈现有限斜率,这有助于在接近饱和时进行控制;并且可能不存在共模控制导致组件数量的减少,这在所占面积和功耗方面都是有利的。

16.一个或多个实施例可以有利地应用于消费者音频应用中,例如应用于汽车音频系统中。

17.一个或多个实施例可以有利地应用于具有全桥末级的d类放大器中。

18.一个或多个实施例可以有利地省去共模反馈:因此,在存在共模负载(例如,朝向地的负载或两个输出处的电源电压)的情况下,两个输出的共模占空比不改变。

附图说明

19.现在将参考附图仅以示例的方式描述一个或多个实施例,其中:

20.图1a是用不同驱动信号驱动的全桥电路的示例性电路图;

21.图1b是用公共驱动信号驱动的全桥电路的示例性电路图;

22.图2是根据本公开并包括多个电流比较器的pwm调制器电路的示例性框图;

23.图3是根据本公开并包括单个电流比较器的pwm调制器电路的示例性框图;

24.图4是电流比较器的操作示例性电路图;以及

25.图5a至图5d是示出在本公开的实施例中可能发生的信号的可能时间行为的时间图。

具体实施方式

26.在随后的描述中,示出了一个或多个具体细节,旨在提供对本描述的实施例的示例的深入理解。可以在没有一个或多个特定细节的情况下,或者通过其它方法、部件、材料等来获得实施例。在其它情况下,未详细说明或描述已知的结构、材料或操作,使得实施例的某些方面不会被遮蔽。

27.在本说明书的框架中对“实施例”或“一个实施例”的提及旨在指示关于实施例描述的特定配置、结构或特征包括在至少一个实施例中。因此,在本说明书的一个或多个点中可能存在的诸如“在实施例中”或“在一个实施例中”的短语不一定指的是一个且相同的实施例。

28.此外,特定构象、结构或特征可以在一个或多个实施例中以任何适当的方式组合。

29.本文使用的标题/参考仅仅是为了方便而提供的,因此不限定实施例的保护程度或范围。

30.通过对当前详细描述的介绍,可以注意到,同相调制的优点在高频pwm调制器中比在低频pwm调制器中更不相关。

31.事实上:同相调制的一个优点与差分模式有关,只要切换发生在双倍频率和信号摆幅减半;这导致耦合到调制器的负载上的纹波减小,这有助于避免出于相同目的而不希望地增大lc元件的尺寸:在高调制频率下,lc滤波器的尺寸减小,这使得可能的尺寸增大更可容忍;同相调制减少了pwm时钟噪声向差分输出的传递:利用高调制频率,可以提供在音频带中具有非常高增益的调整环,这导致对此类噪声的高抑制能力;当pwm信号导通/关断时,同相调制避免了差分信号中的不连续性,防止了砰的(pop)噪声:在高调制频率下,这些不连续性被移至可听范围之外的高频。

32.相反,与同相调制相比,异相调制的优点与共模有关,只要共模谐波比差模谐波分量重;这可能有利于发射。异相调制提供了一个“稳固的”共模,并且随着调制频率的增加,共模的不明显调制仍然是显著的,共模通常被认为比差分模更不受关注。

33.图1a和图1b是创建本质上差动的末级的可能性的示例(这在本领域中可视为常规

的),其中半桥(总是)用相反的相位驱动(反相操作)。

34.图1a和图1b示出了两个半桥,其包括布置在电源节点或线vcc和接地gnd之间的电子开关,例如晶体管(场效应晶体管,例如金属氧化物半导体(mosfet)晶体管可以是这些开关的示例)。

35.负载ld如虚线所示,耦合在输出节点outp和outm之间,位于每个半桥中的两个晶体管之间。

36.在图1a和图1b的相当一般的表示中,负载ld可以代表相当复杂的网络。

37.例如,在包括如图1a和图1b所例示的末级的d类音频放大器的情况下,负载ld可以包括例如lc解调器滤波器、输出阻尼网络和适当的负载,例如可能包括交叉网络的扬声器系统。

38.图1a和图1b所示的半桥中的开关被配置为在pwm工作模式下通过具有互补输出的驱动器级交替接通和关断(图1a和图1b所示,为简单起见未标号),该驱动器级接收不同的驱动信号drvinp和drvinm(图1a)或相同的公共驱动信号drvin(图1b)。

39.在图1b的情况下,两个半桥只接收一个输入信号,即drvin,专用于控制差分模式。这样的公共工作模式无法从外部控制,并且本质上(名义上)固定在vcc/2。

40.如前所述,图1a和图1b所示的每一个半桥中的开关(mosfet晶体管)以相反的相位被驱动(反相操作),目的是避免交叉导通。

41.在如图1a所例示的布置中,两个半桥中的每一个可以用相应的驱动信号drvinp、drvinm(例如,具有值“0”或“1”的逻辑信号)驱动。

42.该信号可以以本领域技术人员已知的方式经由提供有调制信号和载波信号(例如三角波)的比较器产生。

43.用于驱动“p”半桥的载波与用于驱动“m”半桥的载波有一定的相位关系:在同相调制的情况下,用于产生drvinp和drvinm的两个载波同相,即具有0

°

的互相移,而在异相调制的情况下,用于产生drvinp和drvinm的两个载波反相,即具有180

°

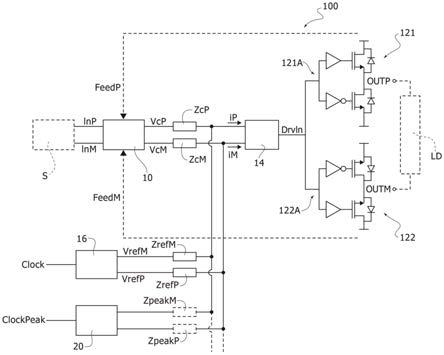

的互相移。

44.这些载波信号之间的相位关系被驱动信号drvinp和drvinm之间的对应相位关系所镜像(如所讨论的,这些可以是具有电压电平0和vcc的二进制信号,对应于具有值“0”或“1”的逻辑信号),其也适用于节点outp和outm处的输出信号。

45.如果(仅)需要异相调制,则可以修改图1a所示的布置,如图1b所示,其中使用单个输入信号drvin(从单个载波获得)来驱动两个半桥,一个与另一个反相:参见图1b中驱动级的“交叉”布置,与图1a中驱动器级的“对称”布置相反,驱动器级具有互补输出。

46.图1b的解决方案比图1a的解决方案简单,后者涉及两个不同的载波(和两个相关的比较器)。此外,图1a所示的包括两个不同的输入drvinp、drvinm的解决方案可能涉及共模的单独调节。

47.仍然通过对本详细描述的介绍,文献us 2015/0207498a1(与us 2017/0155381a1、us 2018/0323774a1、us 9 595 946 b2、us 10 027 315 b2和us 10 615 784 b2相对应)公开了一种用于减少脉冲跳变的方法,该脉冲跳变来自影响输入到脉宽调制(pwm)调制器的积分器的调制信号的特性,以及用于产生pwm调制器的三角波形的方波载波信号。这种方法可以包括在积分器输出的三角形波形的顶点处产生宽的同步峰值。

48.如这些文献中所讨论的那样,发现在载波信号的顶点上添加一个峰值,可以改善

放大器在接近饱和时的行为。

49.利用反馈电路在高调制频率下提供这样的峰值几乎不可避免地涉及使用具有(非常)快速响应和高压摆率的放大器。

50.如本文所例示的电路可以包括全差分pwm调制器,该全差分pwm调制器一方面可受益于由前面提到的末级的特性导出的优点,同时克服现有技术的某些限制。

51.如本文所例示的电路可以应用于开环和闭环pwm调制器。

52.在后一种情况下,调节环路可以包括或可以不包括lc解调滤波器,和/或可以包括一个或多个嵌套环路。

53.图2是pwm调制器电路的示例性体系结构的框图,整体标记为100。

54.图2是在其它常规pwm调制器电路中应用本文所讨论的实施例基础概念(即,使用电流比较器代替电压比较器)的可能性的示例。

55.图2所示的电路100可以被配置为接收由信号源s提供的施加在两个输入节点inp、inm之间的差分输入信号(例如音频信号),并且在两个输出节点outp、outm之间产生要施加到负载ld的相应的pwm调制(差分)信号。

56.源s和负载ld都以虚线示出,只要它们之一或两者可以是与实施例的电路100不同的元件。

57.正如在前面讨论的图1a和图1b的情况下,图2(和图3)中的负载ld实际上可以代表相当复杂的网络(例如lc解调器滤波器、输出阻尼网络、在包括如本文所例示的电路100的d类音频放大器的情况下的扬声器系统)。

58.此外,在整个描述中,为了简洁起见,可以使用相同的标记来引用电路中的某些节点或线以及在该节点或线处出现的信号。这例如可适用于从源s接收差分输入信号的输入节点inp、inm。

59.如图2所示,这样的差分输入信号(简写为inp,inm)被施加到差分级10(例如,全差分放大器)的输入,该差分级10从差分输入信号(例如,inp

‑

inm)开始,生成两个控制信号vcp和vcm,以便在电路的末级中被转发到半桥121、122。

60.否则,本领域技术人员将理解,全差动放大器只是本文所考虑的差分级10的一个示例性可能实现。

61.通过另一可能的示例性实施例,差分级10可以包括两个单端放大器:第一放大器,接收信号inp并向半桥121转发控制信号vcp,以及第二放大器,接收信号inm并向半桥122转发控制信号vcm。

62.这里再次地(如图1a和图1b的情况),两个半桥121、122可以包括电子开关,例如晶体管。诸如mosfet晶体管的场效应晶体管可以是这些开关的示例。

63.负载ld如虚线所示,耦合在每个半桥中的两个晶体管之间的输出节点outp和outm之间。

64.这里再次地,半桥中的开关被配置为经由具有互补输出的互补驱动器级121a、122a交替接通和断开,该互补驱动器级由不同的驱动信号drvinp和drvinm控制。

65.如图所示,驱动信号drvinp和drvinm作为来自相应的电流比较器141、142的输出被提供。这些比较器对载波信号vrefp、vrefm(三角形波形,如下文所述)以及来自差分级10(例如,全差动放大器或一对互补单端放大器)的控制信号vcp和vcm敏感。这可能通过中间

电压到电流转换器阻抗zmuxp、zmuxm和zcp、zcm发生。

66.为了产生载波信号vrefp、vrefm,图2所示的示例性电路包括两个参考生成器161、162,它们被配置为由来自时钟源的相应时钟信号clockp、clockm计时,为了简单起见,时钟源不可见。

67.该时钟源可包括用于该目的的本领域技术人员已知的任何类型的时钟电路装置。

68.例如,在电路100包括在d类音频放大器中的情况下,可以已经提供这样的时钟源以便于放大器的操作:这样的放大器可以常规地包括用时钟信号定时的数字块,例如,可以经由时钟分频器从该时钟信号获得本文所讨论的时钟。

69.图2的示例性电路中的参考生成器161、162可以包括单端放大器。

70.例如,参考生成器161、162可以包括积分器配置中的单端放大器,其从时钟信号clockp、clockm开始产生例如具有三角形形状的(载波)信号vrefp、vrefm。

71.参考载波信号vrefp、vrefm旨在被施加(例如分别经由中间电压到电流转换器阻抗zmuxp和zmuxm转换成电流信号)到电流比较器141、142以与差分控制信号vcp、vcm(例如也分别经由中间电压到电流转换器阻抗zcp和zcm转换成电流信号)比较,从而作为电流比较器141、142中比较的结果产生用于驱动第一半桥级121和第二半桥级122的pwm调制的驱动信号drvinp、drvinn。

72.一般而言,这种类型的操作(pwm调制信号的产生)在本领域中其它方面是常规的,这使得不需要在此提供更详细的描述。如下文所述,本文所述的调制器100的特征在于,导致产生pwm调制信号的比较是作为电流的比较而不是作为电压的比较来执行的。

73.在图2的示例性电路100中,参考信号vrefp、vrefm经由两个多路复用器(mux)181、182被发送到比较器141、142以与控制信号vcp、vcm进行比较,多路复用器被配置为接收信号vrefp、vrefm以及来自参考阈值源的阈值信号vpeakp、vpeakm和来自时钟源的时钟信号clockppeak、clockmpeak。为了简单起见,这些阈值/时钟源(其可包括本领域技术人员为此目的已知的任何类型的电路装置)是不可见的。

74.例如,图2的示例性电路100中的两个多路复用器181、182可包括模拟多路复用器,模拟多路复用器基于围绕诸如vrefp、vrefm的“载波”信号的顶点切换的定时信号clockppeak、clockmpeak,可以将它们的输出切换(强制)到固定电平(电位),目的是产生峰值。

75.例如在us 2019/0123731 a1(对应于us 10 560 082 b2)中公开了相应的布置。

76.简而言之,在这些文献中公开的pwm调制电路包括:第一电路块,被配置为接收方波输入信号并从所述方波输入信号产生三角波信号;第二电路块,被配置为接收调制信号并通过将调制信号与载波信号进行比较来产生pwm信号;切换电路块,耦合在所述第一电路块和所述第二电路块之间,并且对具有上参考值和下参考值的参考信号敏感,并且可选择性地在载波传输设置和一个或多个载波强制设置之间切换,在载波传输设置中,所述切换电路块将所述第一电路块耦合到所述第二电路块以传输所述三角波信号作为载波信号,所述载波强制设置用于优化或抑制所述pwm信号中的脉冲跳过,其中所述切换电路块分别将所述载波信号强制到所述上参考值和下参考值。

77.来自多路复用器181、182的输出(例如,分别经由中间电压到电流转换器阻抗zmuxp和zmuxm)被提供给电流比较器141、142,电流比较器141、142被配置为在末级中产生

用于半桥121、122的驱动信号drvinp、drvinm。

78.图2的示例性电路还包括耦合到生成器161、162以作用在载波信号vrefp、vrefm的基线上的共模反馈线feedcm(以虚线示出)以及作用在产生控制信号vcp、vcm的差分级10(例如全差动放大器或一对互补单端放大器)上的差模反馈线feedp和feedm(同样以虚线示出)。

79.这样的反馈布置和相关的操作原理在其他方面在本领域中是常规的,这使得这里没有必要提供更详细的描述。

80.图2的示例性电路的有利特征在于,比较器141、142包括(差分)电流比较器141、142,以代替电压比较器,这些电流比较器在其输入处接收分别经由电压到电流转换器阻抗zcp、zcm和zmuxp、zmuxm提供的待比较的电流信号。

81.注意,已知电压比较器显示出预期的高输入阻抗(例如,由诸如mosfet晶体管的场效应晶体管的栅极端子提供)。这与电流比较器形成对比,电流比较器已知表现出预期的低输入阻抗(例如由场效应晶体管(例如mosfet晶体管)的源极端子提供)。

82.在如本文所例示的电路中(使用电流比较器代替电压比较器),逻辑值可以用于驱动半桥121、122,该逻辑值表示进入比较器141、142的两个输入端的电流之差的符号。

83.在图3的图中进一步例示了该概念,其中,类似于结合前面的附图已经讨论的实体、元件或部件的实体、元件或部件用类似的参考符号指示;为简洁起见,将不再重复相应的详细描述。

84.如所指出的,图2的图是调制器电路100的示例,其中在末(功率)级中的半桥121、122由相应的驱动信号drvinp、drvinm控制,类似于图1a所示的解决方案的情况。

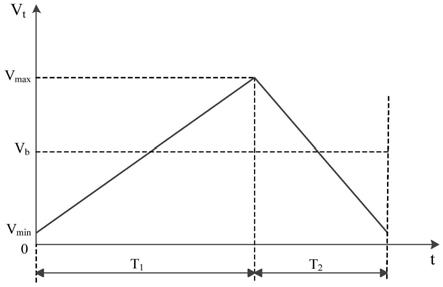

85.相反地,图3的图是调制器电路100的示例,其中半桥中的开关被配置为经由具有互补输出的互补驱动器级121a、122a交替接通和断开,该互补驱动器级121a、122a由单个驱动信号drvin控制,类似于图1b所示的解决方案的情况。

86.此外,应理解,为了简明起见,在下文中说明的与图3的体系结构相关的某些特征可应用于图2的体系结构,该特征包括指定为14的单个电流比较器,该图2的体系结构包括两个电流比较器141、142。同样,已经结合图2的双比较器架构说明的某些特性可以应用于图3的单比较器架构。

87.在图3的示例性电路中,用于驱动半桥121、122的单个驱动信号drvin再次经由代替电压比较器的电流比较器14获得。

88.这样,可以使用逻辑值来驱动半桥121、122,该逻辑值表示进入比较器14的两个输入端的电流之差的符号(即ip

‑

im)。

89.需要注意的是,电流比较器如14(以及141、142)理想地呈现零输入阻抗,因此不同的信号对可以连接到它们的输入,所有信号都彼此去耦。

90.第一对输入信号可对应于从控制电压vcp和vcm获得的差分控制信号,该差分控制信号通过诸如zcp、zcm的电压到电流转换器接入阻抗(参见例如图3中施加到电流比较器14的ip

‑

im)被转换成电流。

91.第二对输入信号可对应于载波参考信号vrefm、vrefp,载波参考信号vrefm、vrefp源自由(单个)时钟信号clock(参见图2中的clockp和clockm)计时的差分参考生成(differential reference generation),通过电压到电流转换器阻抗如zrefm、zrefp(参

见例如图3中具有耦合在其输出处的阻抗zrefm、zrefp的来自生成器16的差分输出电压vrefp

‑

vrefm)再次转换成电流。

92.第三对输入信号可对应于施加在载波信号vrefm、vrefp的顶点处的峰值:参见前面在讨论图2所示的体系结构时引用的各专利文献。

93.这些峰值可由操作中的差分峰值生成器20产生,所述差分峰值生成器20由(单个)差分时钟信号clockpeak(参见图2中的clockppeak和clockmpeak以及下面图4和图5a至图5d的讨论)计时。

94.差分峰值生成器20可以被配置为产生差分电压,该差分电压然后被通过电压到电流转换器访问阻抗zpeakm、zpeakp转换成电流。可选地,差分峰值生成器20可以被配置为直接产生相应的差分电流(为此,阻抗zpeakm、zpeakp以虚线示出)。

95.其它信号对可以根据可能需要连接到电流比较器14的输入,利用前面讨论的相互去耦特征。

96.匹配成对的阻抗(即zcp=zcm,zrefp=zrefm,zpeakp=zpeakm),发现有利于促进图3所示的全差分架构的充分工作。只要失配导致差分信号可能产生(小)共模信号,实现非常严格的匹配就并不是强制性的。布置在下游的电路是差分电路,导致这种小的共模信号很难传输。

97.多晶硅电阻器被发现提供了足够用于本文目的的匹配,具有良好的线性行为和对来自衬底的扰动的降低的灵敏度的优点。

98.此外,采用如g.palmisano和g.palumbo所公开的电流比较器架构,“an offset compensated full differential cmos current comparator”,第38届midwest symposium on circuits and systems。proceedings,riode janeiro,brazila,1995,卷2第1038

‑

1041页,doi:10.1109/mwscas.1995.510271被发现对于例如本文所示的14、141、142的比较器是有利的。

99.用电流比较代替电压比较是有利的,例如,只要通过使相关电路装置更简单和更灵活(特别是当采用图3所示的布局时),它可以促进在三角形载波的顶点提供峰值。

100.图4是如图3所示的差动电流比较器14的示例,该差动电流比较器14被提供有差动峰值电压vpeakdiff=vpeakp

‑

vpeakm,该差动峰值电压用于经由阻抗(电阻器)r1p、r1m对电容器c充电。如图所示,电容器c两端的电压通过另外的阻抗(电阻器)r2p、r2m传递到比较器14的差分(电流)输入,使得电流ipeakdiff循环通过比较器输入。

101.假设如前面所讨论的匹配条件,即r1p=r1m=r1和r2p=r2m=r2,vpeakp和vpeakm的可能时间行为可以如图5a和图5b中针对公共(横坐标)时标所例示。即,vpeakp和vpeakm可以包括具有相同峰值v0p=v0m的脉宽(持续时间)tpeak的脉冲信号;则vpeakdiff和ipeakdiff可针对图5a和图5b的相同公共(横坐标)时标表现出如图5c和图5d所例示的时间行为。

102.用数学术语来说,这可以表示为:

103.ipeakdiff/vpeakdiff=1/(r1 r2)

·

1/1 [sc(2r1.r2)/(r1 r2)]=k/(1 sτ)

[0104]

电流峰值的幅度(见图5d)表示为:

[0105]

i0p=i0m=v0

·

k(1

‑

e

‑

tpeak/τ

)。

[0106]

如本文所例示的(pwm调制器)电路(例如,100)可以包括:第一半桥级(例如,121)

具有第一输出节点(例如,outp)和第二半桥级(例如,122)具有第二输出节点(例如,outm),所述第一输出节点和所述第二输出节点被配置为具有耦合在其间的电负载(例如,ld)以向其施加pwm调制的输出信号、具有输入节点(例如,inp、inm)的差分级(例如,10:这可以是全差动放大器或一对互补单端放大器)、以及至少一个电流比较器(例如,14;141,142);所述差分级被配置为接收施加在所述输入节点之间的输入信号并产生用于所述第一半桥级和所述第二半桥级的差分控制信号(例如,vcp、vcm);所述至少一个电流比较器位于差分级和第一半桥级和第二半桥级之间,所述至少一个电流比较器被配置为根据施加在差分级中的输入节点之间的输入信号产生至少一个pwm调制的驱动信号(例如,drvin;drvinp、drvinn)以驱动第一半桥级和第二半桥级。

[0107]

如反复讨论的,本文所考虑的差分级10适合于以不同的方式实现。例如,全差动放大器的一种可能的替代方案可能涉及将差分级10“分成”两个单端放大器:第一放大器接收信号inp并向半桥121转发控制信号vcp,第二放大器接收信号inm并向半桥122转发控制信号vcm。

[0108]

如本文所例示的电路可以包括位于差分级与第一半桥级和第二半桥级之间的电流比较器,电流比较器被配置为根据施加在差分级中的输入节点之间的输入信号产生施加到第一半桥级和第二半桥级两者的公共pwm调制驱动信号(例如,drvin)。

[0109]

如本文所例示的电路可包括:第一电流比较器(例如,141)在差分级和第一半桥级之间,所述第一电流比较器被配置为根据施加在所述差分级中的输入节点之间的输入信号产生施加到所述第一半桥级的第一pwm调制的驱动信号(例如,drvinp),以及在所述差分级和所述第二半桥级之间的第二电流比较器(例如,142),所述第二电流比较器被配置为根据施加在所述差分级(10)中的输入节点之间的输入信号产生施加到所述第二半桥级的第二pwm调制的驱动信号(例如,drvinm)。

[0110]

如本文所例示的电路可包括耦合到至少一个电流比较器的输入的至少一对匹配阻抗(例如,zcp、zcm;zmuxp、zmuxm;r1p、r1m、r2p、r2m),以提供施加到至少一个电流比较器的信号的电压到电流转换。

[0111]

如本文所例示的电路可以包括耦合(例如zmuxp、zmuxm;zrefp、zrefm)到至少一个电流比较器的至少一个参考信号生成器(例如16、161、162),所述至少一个参考信号生成器被配置为产生至少一个载波信号(例如vrefp、vrefm)以与电流比较器处的差分控制信号进行比较,其中用于驱动第一半桥级和第二半桥级的至少一个pwm调制的驱动信号是(电流)比较的结果。

[0112]

如本文所例示的电路可包括峰值生成电路装置(例如,图3中的20、zpeakp、zpeakm或图2中的181、182、vpeakp、vpeakm或图4中的vpeakp、vpeakm、r1p、r1m、c、r2p、r2m、14),所述峰值生成电路装置被配置为将所述至少一个载波信号的顶点强制到固定值(例如,vpeakp、vpeakm)。

[0113]

在如本文所例示的电路中,峰值生成电路装置可以包括电流峰值生成器电路装置,电流峰值生成器电路装置被配置为在至少一个载波信号的顶点处将电流峰值(参见图4中的14和ipeakdiff)注入到至少一个电流比较器中。

[0114]

如所讨论的,这样的峰值生成器电路装置(例如,参见图3中的20)可被配置为根据需要直接生成电流,而不是要转换成电流的电压(例如,参见图3中虚线所示的zpeakm和

zpeakp)。

[0115]

在如本文所例示的电路中,第一半桥级可包括第一对电子开关,在第一对电子开关之间具有第一输出节点,并且第二半桥级可包括第二对电子开关,在第二对电子开关之间具有第二输出节点;所述对中的电子开关可被配置为经由具有互补输出的驱动器级(例如121a、122a)交替地接通和断开。

[0116]

如本文所例示的设备可以包括:如本文所例示的电路(例如100)、耦合到差分级的输入节点(例如inp、inm)并被配置为在输入节点之间施加输入信号的信号源(例如s),以及电负载(例如ld),电负载耦合在第一半桥级的第一输出节点和第二半桥级的第二输出节点之间,以将pwm调制的输出信号施加到其上。

[0117]

如本文所例示的设备可包括d类(例如音频)放大器。

[0118]

例如,与实施输出电流控制策略的d类放大器(例如,经由触发器,其在每个时钟周期被设置并作为输出电感器电流达到阈值电平的结果而复位)相比,本文所例示的调制器电路可有利地用于实施输出电压控制策略的d类放大器中。

[0119]

如本文所例示的驱动电路或设备的方法可包括:在差分级的输入节点(inp,inm)之间施加输入信号,以及在第一半桥级中的第一输出节点和第二半桥级中的第二输出节点之间收集pwm调制的输出信号,该输出信号是在差分级(10)中的输入节点之间施加的输入信号的函数。

[0120]

在不损害基本原理的情况下,在不偏离保护范围的情况下,细节和实施例可以相对于仅以示例的方式描述的内容变化,甚至显著地变化。

[0121]

保护范围由所附权利要求决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。