技术特征:

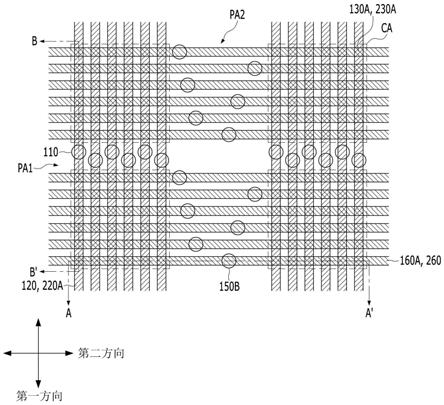

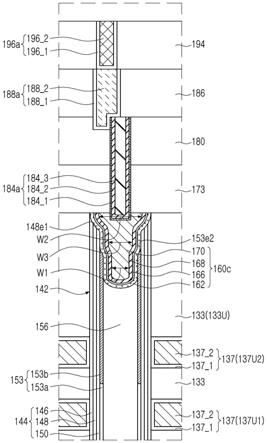

1.一种电子器件,包括半导体存储器,所述半导体存储器包括:衬底,其包括单元区域、在第一方向上设置在所述单元区域的第一侧的第一外围电路区域和在与所述第一方向交叉的第二方向上设置在所述单元区域的第二侧的第二外围电路区域;多个第一线路,其设置在所述衬底之上并且在所述第一方向上延伸穿越所述单元区域和所述第一外围电路区域;多个第二线路,其设置在所述第一线路之上并且在所述第二方向上延伸穿越所述单元区域和所述第二外围电路区域;接触插塞,其设置在所述第二外围电路区域中并且具有耦接到所述第二线路的上表面;多个第三线路,其设置在所述第二线路之上并且分别与所述第二线路交叠;多个第四线路,其设置在所述第三线路之上并且分别与所述第一线路交叠;多个第一存储单元,其设置在所述单元区域中并且位于所述第一线路和所述第二线路的相交处在所述第一线路和所述第二线路之间;以及多个第二存储单元,其设置在所述单元区域中并且位于所述第三线路和所述第四线路的相交处在所述第三线路和所述第四线路之间,其中,所述第三线路的位于所述单元区域中的第一部分以及所述第三线路的位于所述接触插塞之上的第二部分接触所述第二线路,以及所述第三线路的剩余部分的至少部分与所述第二线路隔开。2.如权利要求1所述的电子器件,其中,所述第二线路与所述第三线路的剩余部分的所述至少部分之间的空间填充有绝缘材料。3.如权利要求1所述的电子器件,其中,所述接触插塞的上表面的高度等于或高于所述第一存储单元的上表面的高度。4.如权利要求3所述的电子器件,其中,所述半导体存储器还包括:层间绝缘层,其设置在所述第二线路之下,以及其中,所述层间绝缘层的在所述第二外围电路区域中的部分包括凹入部分,所述凹入部分低于所述第一存储单元的上表面和所述接触插塞的上表面。5.如权利要求4所述的电子器件,其中,所述单元区域中的所述层间绝缘层具有与所述第一存储单元的上表面实质上共面的上表面。6.如权利要求4所述的电子器件,其中,所述凹入部分的高度随着距所述单元区域的距离在第一距离上增大而减小并且随着距所述单元区域的距离在第二距离上增大而增大。7.如权利要求4所述的电子器件,其中,所述第二线路沿所述第一存储单元的上表面、所述接触插塞的上表面和所述层间绝缘层的上表面形成。8.如权利要求7所述的电子器件,其中,所述第二线路在所述凹入部分之上具有凹入的下表面和凹入的上表面。9.如权利要求8所述的电子器件,其中,所述半导体存储器还包括:绝缘材料,其设置在所述第二线路的凹入的上表面之上,所述绝缘材料具有高度与所述单元区域中的所述第二线路的上表面实质上相同的上表面。10.如权利要求9所述的电子器件,其中,所述第三线路的下表面接触所述单元区域中

的所述第二线路的上表面、所述绝缘材料的上表面和所述接触插塞之上的所述第二线路的上表面。11.如权利要求1所述的电子器件,其中,除了所述第三线路的剩余部分的所述至少部分之外,所述第三线路具有平坦的下表面。12.如权利要求1所述的电子器件,其中,所述第三线路在所述单元区域和所述第二外围电路区域中具有平坦的下表面。13.如权利要求1所述的电子器件,其中,所述第三线路在所述单元区域和所述第二外围电路区域中具有平坦的上表面。14.如权利要求4所述的电子器件,其中,所述层间绝缘层包括:单元绝缘层,其填充在所述单元区域中的所述第一存储单元之间;以及外围电路绝缘层,其填充在所述第二外围电路区域中,其中,所述单元绝缘层的热导率低于所述外围电路绝缘层的热导率。15.如权利要求14所述的电子器件,其中,所述第一存储单元包括相变材料。16.如权利要求1所述的电子器件,还包括微处理器,所述微处理器包括:控制部,其被配置成从所述微处理器外部接收包括命令的信号,以及执行所述命令的提取、解码或者控制所述微处理器的信号的输入或输出;运算部,其被配置成基于所述控制部对所述命令解码的结果来执行运算;以及存储部,其被配置成存储:用于执行所述运算的数据、与执行所述运算的结果对应的数据、或者被执行所述运算的数据的地址,其中,所述半导体存储器是所述微处理器中的存储部的部分。17.如权利要求1所述的电子器件,还包括处理器,所述处理器包括:核心部,其被配置成:基于从所述处理器的外部输入的命令,通过使用数据来执行与所述命令对应的操作;缓存存储部,其被配置成存储:用于执行所述操作的数据、与执行所述操作的结果对应的数据、或者被执行所述操作的数据的地址;以及总线接口,其连接在所述核心部和所述缓存存储部之间,并且被配置成在所述核心部和所述缓存存储部之间传送数据,其中,所述半导体存储器是所述处理器中的缓存存储部的部分。18.如权利要求1所述的电子器件,还包括处理系统,所述处理系统包括:处理器,其被配置成对所述处理器接收到的命令解码以及基于对所述命令解码的结果来控制对信息的操作;辅助存储器件,其被配置成存储用于对所述命令解码的程序和所述信息;主存储器件,其被配置成从所述辅助存储器件调用和存储所述程序和所述信息,使得所述处理器在执行所述程序时使用所述程序和所述信息执行所述操作;以及接口器件,其被配置成执行所述处理器、所述辅助存储器件和所述主存储器件中的至少一种与外部之间的通信,其中,所述半导体存储器是所述处理系统中的所述辅助存储器件或所述主存储器件的部分。19.如权利要求1所述的电子器件,还包括存储系统,所述存储系统包括:

存储器,其被配置成存储数据并且不管供电与否都保持所存储的数据;存储器控制器,其被配置成根据从外部输入的命令而控制向所述存储器的数据输入和从所述存储器的数据输出;缓冲存储器,其被配置成缓冲在所述存储器和外部之间交换的数据;以及接口,其被配置成执行所述存储器、所述存储器控制器和所述缓冲存储器中的至少一种与外部之间的通信,其中,所述半导体存储器是所述存储系统中的所述存储器或所述缓冲存储器的部分。20.一种电子器件,包括半导体存储器,所述半导体存储器包括:衬底,其包括单元区域、在第一方向上设置在所述单元区域的第一侧的第一外围电路区域和在与所述第一方向交叉的第二方向上设置在所述单元区域的第二侧的第二外围电路区域;多个第一线路,其设置在所述衬底之上并且在所述第一方向上延伸穿越所述单元区域和所述第一外围电路区域;多个第二线路,其设置在所述第一线路之上并且在所述第二方向上延伸穿越所述单元区域和所述第二外围电路区域;多个第三线路,其设置在所述第二线路之上并且分别与所述第二线路交叠,所述第三线路局部地接触所述第二外围电路区域中的所述第二线路;多个第四线路,其设置在所述第三线路之上并且分别与所述第一线路交叠;多个第一存储单元,其设置在所述单元区域中并且位于所述第一线路和所述第二线路的相交处在所述第一线路和所述第二线路之间;以及多个第二存储单元,其设置在所述单元区域中并且位于所述第三线路和所述第四线路的相交处在所述第三线路和所述第四线路之间,其中,所述第二线路的上表面和下表面在所述第二外围电路区域中均包括凸出部分和凹入部分,并且所述第三线路接触所述第二线路的上表面的凸出部分。21.一种用于制造包括半导体存储器的电子器件的方法,所述方法包括:提供衬底,所述衬底包括单元区域、在第一方向上设置在所述单元区域的第一侧的第一外围电路区域和在与所述第一方向交叉的第二方向上设置在所述单元区域的第二侧的第二外围电路区域;在所述衬底之上形成多个堆叠结构,所述堆叠结构在所述第一方向上延伸穿越所述第一区域和所述第一外围电路区域,每个堆叠结构包括第一线路和初始第一存储单元;形成填充在所述堆叠结构之间的层间绝缘层和穿过所述第二外围电路区域中的所述层间绝缘层的接触插塞,所述第二外围电路区域中的所述层间绝缘层具有凹入部分,所述凹入部分的上表面凹入而低于所述初始第一存储单元的上表面,并且所述接触插塞的上表面的高度等于或高于所述初始第一存储单元的上表面的高度;形成多个第二线路,所述第二线路在所述第二方向上延伸穿越所述单元区域和所述第二外围电路区域,并且在所述初始第一存储单元、所述层间绝缘层和所述接触插塞之上延伸,其中所述第二线路中的一个接触所述接触插塞的上表面;通过刻蚀经由所述第二线路露出的所述初始第一存储单元来形成第一存储单元;以及形成分别与所述第二线路交叠的多个第三线路,

其中,所述多个第三线路中的一个第三线路的位于所述单元区域中的第一部分和所述一个第三线路的位于所述接触插塞之上的第二部分接触所述第二线路,以及所述一个第三线路的剩余部分的至少部分与所述第二线路隔开。22.如权利要求21所述的方法,其中,形成所述层间绝缘层和所述接触插塞包括:在所述衬底之上形成覆盖所述堆叠结构的绝缘层;通过选择性地刻蚀所述绝缘层而形成接触孔,所述接触孔提供在其中形成所述接触插塞的空间;在所述绝缘层之上形成导电层,所述导电层填充所述接触孔并且具有预定厚度;通过对所述导电层执行第一平坦化工艺使得所述绝缘层露出来形成初始接触插塞;以及通过对所述绝缘层执行第二平坦化工艺使得所述初始第一存储单元露出来形成所述接触插塞。23.如权利要求22所述的方法,其中,所述初始接触插塞的上表面的高度高于所述初始第一存储单元的上表面的高度。24.如权利要求21所述的方法,其中,所述第二线路沿所述初始第一存储单元的上表面、所述层间绝缘层的上表面和所述接触插塞的上表面形成。25.如权利要求24所述的方法,其中,所述第二线路在所述凹入部分之上具有凹入的下表面和凹入的上表面。26.如权利要求24所述的方法,其中,在形成所述第三线路之前,所述方法还包括:形成覆盖所述第一存储单元和所述第二线路的绝缘层;以及执行平坦化工艺以使所述单元区域中的所述第二线路的上表面露出。27.如权利要求26所述的方法,其中,所述第三线路的形成被执行成使得所述第三线路的剩余部分的所述至少部分接触所述绝缘层的上表面。28.如权利要求27所述的方法,其中,除了所述第三线路的剩余部分的所述至少部分之外,所述第三线路具有平坦的下表面。29.如权利要求27所述的方法,其中,所述第三线路在所述单元区域和所述第二外围电路区域中具有平坦的下表面。30.如权利要求27所述的方法,其中,所述第三线路在所述单元区域和所述第二外围电路区域中具有平坦的上表面。31.如权利要求21所述的方法,其中,所述层间绝缘层包括在所述单元区域中的单元绝缘层以及在所述第二外围电路区域中的外围电路绝缘层,以及所述单元绝缘层的热导率低于所述外围电路绝缘层的热导率。32.如权利要求31所述的方法,其中,所述第一存储单元包括相变材料。33.如权利要求21所述的方法,还包括:形成与每个所述第三线路交叠的初始第二存储单元;形成与每个所述第一线路和所述初始第二存储单元交叠的第四线路;以及通过刻蚀所述初始第二存储单元的经由所述第四线路露出的部分来形成第二存储单元。

技术总结

本申请公开了电子器件及其制造方法。电子器件包括半导体存储器,半导体存储器包括:衬底,其包括单元区域、设置在单元区域两侧的第一外围电路区域和第二外围电路区域;第一线路,其延伸穿越单元区域和第一外围电路区域;第二线路,其设置在第一线路之上并且延伸穿越单元区域和第二外围电路区域;接触插塞,其在第二外围电路区域中并且连接到第二线路;第三线路,其设置在第二线路之上并且分别与第二线路交叠;以及第一存储单元,其设置在单元区域中并且位于第一线路和第二线路的相交处在第一线路和第二线路之间,其中第三线路的位于单元区域中并且在接触插塞之上的部分接触第二线路,并且第三线路的部分剩余部分与第二线路隔开。隔开。隔开。

技术研发人员:金晃衍

受保护的技术使用者:爱思开海力士有限公司

技术研发日:2020.10.21

技术公布日:2021/12/16

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。