1.本发明涉及声表面波器件领域,尤其涉及一种具有复合膜层的声表面波装置。

背景技术:

2.声表面波装置已广泛应用于通信、医疗、卫星、交通等领域,但是传统的声表面波装置受制于材料本身的限制,即将不能满足高端声表面波产品的性能要求。复合键合结构声表面波装置集大带宽、低插损、低温漂、大功率以及高带外抑制等优点而备受关注,但是复合键合结构也会引起诸多寄生问题,例如高阶杂波响应,这将恶化滤波器的带外抑制,也会引起双工器或射频模块之间的模式串扰,极大地影响通信装置的性能。

技术实现要素:

3.本发明人针对上述问题及技术需求,提出了一种具有复合膜层的声表面波装置,本发明的技术方案如下:

4.一种具有复合膜层的声表面波装置,包括复合膜层和叉指电极;叉指电极形成于复合膜层上方,叉指电极的周期长度为λ;复合膜层中的任意一个界面处形成有图案化结构;图案化结构为凹槽阵列图形。

5.进一步的,复合膜层包括支撑衬底和压电层,压电层形成于支撑衬底上方,凹槽阵列图形形成在支撑衬底上表面或压电层下表面。

6.进一步的,复合膜层包括自下而上依次设置的支撑衬底、介质层和压电层。

7.进一步的,凹槽阵列图形形成在支撑衬底上表面或介质层下表面。

8.进一步的,凹槽阵列图形形成在介质层上表面或压电层下表面。

9.进一步的,凹槽阵列图形表面沉积有一层平坦化介质层,压电层下方的膜层通过平坦化介质层与压电层键合。

10.进一步的,介质层包括高声速介质层和低声速介质层,低声速介质层形成于高声速介质层上表面,低声速介质层的体声波速度低于压电层表面的弹性波声速,高声速介质层的体声波速度高于压电基板表面的弹性波声速;凹槽阵列图形形成在高声速介质层的上表面或形成在低声速介质层的下表面。

11.进一步的,凹槽阵列图形呈定周期或变周期分布。

12.进一步的,凹槽阵列图形的周期范围为0.2λ

‑

λ,凹槽阵列图形的占空比为 0.2

‑

0.8。

13.进一步的,声表面波装置包括谐振器、滤波器、双工器或包含谐振器、滤波器和双工器中至少一种的射频模组。

14.本发明的有益技术效果是:

15.本技术公开了一种具有复合膜层的声表面波装置,该声表面波装置在复合膜层的界面处通过刻蚀工艺进行图案化处理,形成凹槽阵列图形,可以有效散射高阶杂波响应;通过调节图形的深度与径向大小,可以减小甚至消除不同频段的高阶杂波,有效提高阻带抑

制能力。

附图说明

16.图1a

‑

1g是本技术公开的声表面波装置的凹槽阵列图形示意图。

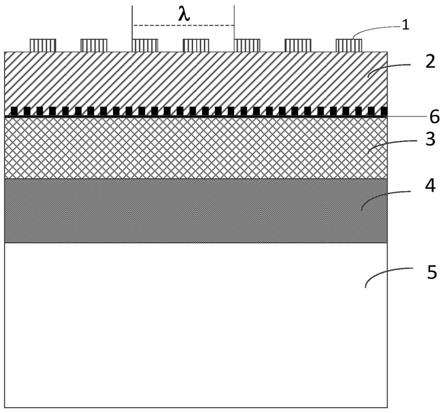

17.图2是本技术实施例1的声表面波装置的结构示意图。

18.图3是本技术实施例2的声表面波装置的结构示意图。

19.图4是本技术实施例3的声表面波装置的结构示意图。

20.图5是本技术实施例4的声表面波装置的结构示意图。

21.图6是本技术实施例5的声表面波装置的结构示意图。

22.图7a

‑

7b是本技术实施例5的声表面波装置的性能测试图。

具体实施方式

23.下面结合附图对本发明的具体实施方式做进一步说明。

24.本发明提供了一种低损耗声表面波装置,如图1

‑

6所示,一种具有复合膜层的声表面波装置,包括复合膜层和叉指电极;叉指电极形成于复合膜层上方,叉指电极的周期长度为λ,较优的,叉指电极的金属化比为0.3

‑

0.8,叉指电极的厚度为周期长度λ的3

‑

12%;复合膜层中的任意一个界面处形成有图案化结构;图案化结构为凹槽阵列图形,较优的,凹槽阵列图形包括沿着第一方向的若干条平行的凹槽和/或沿着第二方向的若干条平行的凹槽,沿着每个方向的每条凹槽连续或间隔离散,第二方向与第一方向之间的夹角为0~180

°

。

25.较优的,凹槽阵列图形呈定周期或变周期分布,凹槽阵列图形的周期范围为0.2λ

‑

λ,凹槽阵列图形的占空比为0.2

‑

0.8。

26.可选的,复合膜层包括支撑衬底和压电层,压电层形成于支撑衬底上方,凹槽阵列图形形成在支撑衬底上表面或压电层下表面;优选的,凹槽阵列图形表面沉积有一层平坦化介质层,支撑衬底和压电层通过平坦化介质层键合。

27.可选的,复合膜层包括自下而上依次设置的支撑衬底、介质层和压电层;凹槽阵列图形可以形成在支撑衬底上表面或介质层下表面,也可形成在介质层上表面或压电层下表面。

28.优选的,当凹槽阵列图形形成在介质层上表面或压电层下表面时,凹槽阵列图形表面沉积有一层平坦化介质层,介质层和压电层通过平坦化介质层键合。

29.可选的,介质层可包括高声速介质层和低声速介质层,低声速介质层形成于高声速介质层上表面,低声速介质层的体声波速度低于压电层表面的弹性波声速,高声速介质层的体声波速度高于压电基板表面的弹性波声速;凹槽阵列图形形成在高声速介质层的上表面或形成在低声速介质层的下表面。

30.较优的,高声速介质层的厚度为0.4λ

‑

λ,低声速介质层的厚度为0.15λ

‑

0.4λ;高声速介质层的材料包括si3n4、sic、多晶硅、非晶硅、aln、al2o3、gan中的至少一种,低声速介质层的材料包括sio2、sion、teo2、氟离子或硼离子或碳离子掺杂的sio2中的至少一种。

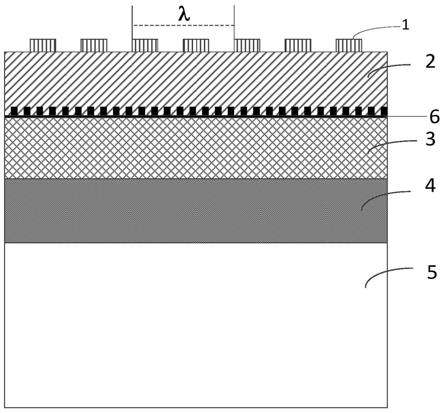

31.可选的,压电层的材料包括石英、铌酸锂、钽酸锂、氮化铝、氧化锌、pzt 中的至少一种。

32.可选的,声表面波装置包括谐振器、滤波器、双工器或包含谐振器、滤波器和双工

器中至少一种的射频模组。

33.实施例1

34.图2示出了本发明实施例1提供的一种具有复合膜层的声表面波装置。该声表面波装置的复合膜层包括支撑衬底4和压电层2,压电层2设置在支撑衬底上方,叉指电极1设置在压电层2上方;凹槽阵列图形形成在支撑衬底4的上表面;凹槽阵列图形上表面沉积有平坦化介质层3。该声表面波装置的制备方法如下:

35.步骤1、获取支撑衬底4并清洗表面,该支撑衬底4的材料包括金刚石、蓝宝石、硅、碳化硅、石英玻璃中的至少一种;

36.步骤2、在支撑衬底4上表面涂胶、光刻、显影、刻蚀、去胶,得到凹槽阵列图形,凹槽阵列图形从支撑衬底4上表面向下延伸一定深度,图形的深度范围为0.25λ

‑

λ;

37.步骤3、在凹槽阵列图形表面沉积薄介质层,后续cmp磨平形成平坦化介质层3,平坦化介质层3的材料可为sio2、si3n4或粘连材料中的任意一种;

38.步骤4、在压电基板的第一表面进行离子注入,注入离子为氢离子,注入深度控制在压电基板第一表面以下5λ

‑

15λ处;第一表面到离子注入位置之间的压电基板为有效压电基板;

39.步骤5、将步骤3中的平坦化介质层3的表面与压电基板的第一表面键合,键合方法包括热压键合、超声键合或直接键合,键合后采用热分离的方式将有效压电基板以外的压电基板去除,形成压电层2,压电层2的厚度为5λ

‑

15λ;

40.步骤6、在压电层2的表面上沉积叉指电极1,叉指电极1的材料包括ti、 al、cu、ag、ni、cr、pt、au、mo、w中的至少一种,叉指电极1的厚度为 0.03λ

‑

0.09λ,沉积方式为电子束蒸发。

41.实施例2

42.图3示出了本发明实施例2提供的一种具有复合膜层的声表面波装置。该声表面波装置的复合膜层包括支撑衬底4和压电层2,压电层2设置在支撑衬底上方,叉指电极1设置在压电层2上方;凹槽阵列图形形成在压电层2与支撑衬底4的上表面相对的表面;凹槽阵列图形上表面沉积有平坦化介质层3。

43.该声表面波装置的制备方法如下:

44.步骤1、获取压电基板并清洗表面,在压电基板的第一表面涂胶、光刻、显影、刻蚀、去胶,得到凹槽阵列图形,凹槽阵列图形从压电基板第一表面向内延伸一定深度,图形的深度为0.1λ

‑

0.5λ;

45.步骤2、在凹槽阵列图形表面沉积薄介质层,后续cmp磨平形成平坦化介质层3,平坦化介质层3的材料可为sio2、si3n4或粘连材料中的任意一种;

46.步骤3、在平坦化介质层3的表面进行离子注入,注入离子为氢离子,注入深度控制在压电基板第一表面以下5λ

‑

15λ处,第一表面到离子注入位置之间的压电基板为有效压电基板。

47.步骤4、将平坦化介质层3的表面与支撑衬底4的上表面键合,键合方法包括热压键合、超声键合或直接键合,键合后采用热分离的方式将有效压电基板以外的压电基板去除,形成压电层2,压电层2的厚度为5λ

‑

15λ;该支撑衬底4的材料包括金刚石、蓝宝石、硅、碳化硅、石英玻璃中的至少一种;

48.步骤5、在压电层2上沉积叉指电极1,叉指电极1的材料包括ti、al、 cu、ag、ni、cr、pt、au、mo、w中的至少一种,叉指电极1的厚度为0.08λ

‑

0.12λ,沉积方式为电子束蒸发。

49.实施例3

50.图4示出了本发明实施例3提供的一种具有复合膜层的声表面波装置。该声表面波装置的复合膜层包括由下而上依次设置的支撑衬底5、高声速介质层 4、低声速介质层3和压电层2,叉指电极1设置在压电层2上方;图中示出的凹槽阵列图形形成在支撑衬底5的上表面,但该凹槽阵列图形也可形成在高声速介质层4的下表面。该声表面波装置的制备方法如下,该制备方法以凹槽阵列图形形成在支撑衬底5的上表面为例:

51.步骤1、获取支撑衬底5并清洗表面,该支撑衬底5的材料包括金刚石、蓝宝石、硅、碳化硅、石英玻璃中的至少一种;

52.步骤2、在支撑衬底5表面涂胶、光刻、显影、刻蚀、去胶,得到凹槽阵列图形,凹槽阵列图形从支撑衬底5表面向内延伸一定深度,图形的深度为 0.25λ

‑

λ;

53.步骤3、在凹槽阵列图形表面沉积高声速介质层4,高声速介质层4的材料为包括si3n4、sic、多晶硅、非晶硅、aln、al2o3、gan中的至少一种,沉积方法可为lpcvd、pecvd或pvd,高声速介质层4的厚度为0.4λ

‑

λ;优选的,采用lpcvd方式沉积多晶硅,后续用cmp将多晶硅磨平减薄形成高声速介质层4;

54.步骤4、在高声速介质层4表面沉积低声速介质层3,低声速介质层3的材料包括sio2、sion、teo2、氟离子或硼离子或碳离子掺杂的sio2中的至少一种,沉积方法可为lpcvd、pecvd或pvd,低声速介质层3的厚度为 0.15λ

‑

0.4λ;优选的,采用pvd沉积sio2,后续用cmp将sio2磨平减薄形成低声速介质层3;

55.步骤5、获取压电基板,在压电基板第一表面进行离子注入,注入离子为氢离子,注入深度为压电基板第一表面以下0.1λ

‑

0.3λ处,从压电基板第一表面到离子注入位置之间的压电基板为有效压电基板。

56.步骤6、将上述压电基板的第一表面与步骤4中的低声速介质层3表面进行键合,键合方式为直接键合,键合后进行热分离处理,将有效压电基板以外的压电基板去除,形成压电层2,压电层2的厚度为0.1λ

‑

0.3λ。

57.步骤7、在压电层2上沉积叉指电极1,叉指电极1的材料包括ti、al、 cu、ag、ni、cr、pt、au、mo、w中的至少一种,叉指电极1的厚度为0.03λ

‑

0.09λ,沉积方式为电子束蒸发。

58.实施例4

59.图5示出了本发明实施例4提供的一种具有复合膜层的声表面波装置。该声表面波装置的复合膜层包括由下而上依次设置的支撑衬底5、高声速介质层 4、低声速介质层3和压电层2,叉指电极1设置在压电层2上方;图中示出的凹槽阵列图形形成在压电层2的下表面,但该凹槽阵列图形也可形成在低声速介质层3的上表面;凹槽阵列图形上表面沉积有平坦化介质层6。该声表面波装置的制备方法如下,该制备方法以凹槽阵列图形形成在压电层2的下表面为例:

60.步骤1、获取支撑衬底5并清洗表面,该支撑衬底5的材料包括金刚石、蓝宝石、硅、碳化硅、石英玻璃中的至少一种;

61.步骤2、在支撑衬底5上沉积高声速介质层4,高声速介质层4的材料包括 si3n4、sic、多晶硅、非晶硅、aln、al2o3、gan中的至少一种,沉积方法可为lpcvd、pecvd或pvd,高声

速介质层4的厚度为0.4λ

‑

λ;优选的,采用 lpcvd方式沉积多晶硅,后续用cmp将多晶硅磨平减薄形成高声速介质层4;

62.步骤3、在高声速介质层4上沉积低声速介质层3,低声速介质层3的材料包括sio2、sion、teo2、氟离子或硼离子或碳离子掺杂的sio2中的至少一种,沉积方法可为lpcvd、pecvd或pvd,低声速介质层3的厚度为0.15λ

‑

0.4λ;优选的,采用pvd沉积sio2,后续用cmp将sio2磨平减薄形成低声速介质层 3;

63.步骤4、获取压电基板并清洗表面,在压电基板的第一表面涂胶、光刻、显影、刻蚀、去胶,得到凹槽阵列图形,凹槽阵列图形从压电基板第一表面向内延伸一定深度,图形的深度为0.01λ

‑

0.03λ;

64.步骤5、在凹槽阵列图形表面沉积薄介质层,后续cmp磨平形成平坦化介质层6,平坦化介质层6的材料可为sio2、si3n4或粘连材料中的任意一种;

65.步骤6、在平坦化介质层6的表面进行离子注入,注入离子为氢离子,注入深度控制在压电基板第一表面以下0.1λ

‑

0.3λ处,压电基板第一表面到离子注入位置之间的压电基板为有效压电基板;

66.步骤7、将平坦化介质层6层的表面与低声速介质层3的表面键合,键合方法采用直接键合,键合后采用热分离的方式将有效压电基板以外的压电基板去除,形成压电层2,压电层2的厚度为0.1λ

‑

0.3λ。

67.步骤8、在压电层2上沉积叉指电极1,叉指电极1的材料包括ti、al、 cu、ag、ni、cr、pt、au、mo、w中的至少一种,叉指电极1的厚度为0.08λ

‑

0.12λ,沉积方式为电子束蒸发。

68.实施例5

69.图6示出了本发明实施例5提供的一种具有复合膜层的声表面波装置。该声表面波装置的复合膜层包括由下而上依次设置的支撑衬底5、高声速介质层 4、低声速介质层3和压电层2,叉指电极1设置在压电层2上方;图中示出的凹槽阵列图形形成在高声速介质层4的上表面,但该凹槽阵列图形也可形成在低声速介质层3的下表面。该声表面波装置的制备方法如下,该制备方法以凹槽阵列图形形成在高声速介质层4的上表面为例:

70.步骤1、获取支撑衬底5并清洗表面,该支撑衬底5的材料包括金刚石、蓝宝石、硅、碳化硅、石英玻璃中的至少一种;

71.步骤2、在支撑衬底5上沉积高声速介质层4,高声速介质层的材料包括 si3n4、sic、多晶硅、非晶硅、aln、al2o3、gan中的至少一种,沉积方法可为lpcvd、pecvd或pvd,高声速介质层4的厚度为0.4λ

‑

λ;优选的,采用 lpcvd方式沉积多晶硅,后续用cmp将多晶硅磨平减薄形成高声速介质层4;

72.步骤3、在高声速介质层4表面涂胶、光刻、显影、刻蚀,得到凹槽阵列图形,凹槽阵列图形从高声速介质层4表面向内延伸一定深度,图形的深度为为0.1λ

‑

0.2λ;

73.步骤4、在凹槽阵列图形表面上沉积低声速介质层3,低声速介质层3的材料包括sio2、sion、teo2、氟离子或硼离子或碳离子掺杂的sio2中的至少一种,沉积方法可为lpcvd、pecvd或pvd,低声速介质层3的厚度为 0.15λ

‑

0.4λ;优选的,采用pvd沉积sio2,后续用cmp将sio2磨平减薄形成低声速介质层3;

74.步骤5、获取压电基板,对压电基板第一表面进行离子注入,注入离子为氢离子,注入深度为压电基板第一表面以下0.1λ

‑

0.3λ处,从压电基板第一表面到离子注入位置之间

的压电基板为有效压电基板;

75.步骤6、将压电基板的第一表面与低声速介质层3的表面进行键合,键合方式为直接键合,键合后进行热分离处理将有效压电基板以外的压电基板去除,形成压电层2,压电层2的厚度为0.1λ

‑

0.3λ。

76.步骤7、在压电层2上沉积叉指电极1,叉指电极1的材料包括ti、al、 cu、ag、ni、cr、pt、au、mo、w中的至少一种,叉指电极1的厚度为0.03λ

‑

0.12λ,沉积方式为电子束蒸发。

77.对于以上实施例中所形成的凹槽阵列图形的结构,具体可参考图1a

‑

1g所示:

78.可选的,凹槽阵列图形如图1

‑

a,图形呈定周期排列,周期p的范围为 0.1λ

‑

0.4λ,图形的占空比为0.2

‑

0.8,图形的最长边轴向与晶圆定位边方向的夹角为θ,θ的取值为0

°

≤θ<180

°

;

79.可选的,凹槽阵列图形如图1

‑

b,图形呈定周期排列,周期p的范围为 0.1λ

‑

0.4λ,图形的占空比为0.2

‑

0.8,图形的最长边轴向之间的夹角为θ,θ的取值为0

°

<θ<180

°

;

80.可选的,凹槽阵列图形如图1

‑

c,图形呈定周期排列,周期p的范围为 0.1λ

‑

0.4λ,图形的占空比为0.2

‑

0.8,每个图形的长度为0.1λ

‑

2λ,图形最长边轴向与晶圆定位边方向的夹角为θ,θ的取值为0

°

≤θ<180

°

。

81.应需求不同,压电层和介质层的厚度会做相应调整,高阶模式数目也会产生不同,因此为尽可能减少各类高阶杂波,图形化处理需要考虑不同周期的凹槽阵列图形,周期数目等于高阶模式数目。

82.可选的,凹槽阵列图形如图1

‑

d,图形呈变周期排列,周期从p1变化到 pn,周期范围为0.1λ

‑

0.4λ,图形的占空比为0.2

‑

0.8,图形最长边轴向与晶圆定位边方向的夹角为θ,θ的取值为0

°

≤θ<180

°

;

83.可选的,凹槽阵列图形如图1

‑

e,图形呈变周期排列,周期从p1变化到pn,周期范围为0.1λ

‑

0.4λ,图形的占空比为0.2

‑

0.8,图形最长边轴向之间的夹角为θ,θ的取值为0

°

<θ<180

°

;

84.可选的,凹槽阵列图形如图1

‑

f,图形呈变周期排列,周期从p1变化到pn,周期范围0.1λ

‑

0.4λ,图形的占空比为0.2

‑

0.8,每个图形的长度为0.1λ

‑

2λ,图形最长边轴向与晶圆定位边方向的夹角为θ,θ的取值为0

°

≤θ<180

°

;

85.可选的,凹槽阵列图形如图1

‑

g,图形为微纳尺度阵列,图形定周期或变周期排列,周期范围为0.1λ

‑

0.4λ,图形的占空比为0.2

‑

0.8,图形表面形状可为圆形、三角形、四边形或其他多边形的任意一种。

86.本发明实施例5中的声表面波装置的性能测试结果如图7所示,其中图7

‑

a 示出了谐振器导纳测试曲线图,图7

‑

b示出了梯形滤波器测试曲线图。谐振器的高阶模式被大幅抑制,由此制备的梯形滤波器的高端抑制水平得到明显的改善,由此可见,合理设计复合膜层界面处的凹槽阵列图形能有效地抑制各类高阶杂波响应。

87.以上所述的仅是本发明的优选实施方式,本发明不限于以上实施例。可以理解,本领域技术人员在不脱离本发明的精神和构思的前提下直接导出或联想到的其他改进和变化,均应认为包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。