半导体装置

1.分案申请的相关信息

2.本案是分案申请。该分案的母案是申请日为2017年8月2日、申请号为201710650835.5、发明名称为“半导体装置及其制造方法”的发明专利申请案。

3.[相关申请案]

[0004]

本技术案享有以日本专利申请案2017

‑

53588号(申请日:2017年3月17日)为基础申请案的优先权。本技术案通过参照该基础申请案而包含基础申请案的全部内容。

技术领域

[0005]

本发明的实施方式涉及一种半导体装置及其制造方法。

背景技术:

[0006]

半导体存储器等半导体芯片有自高功能化或高集成化等观点考虑进行积层的情况。为了将所积层的多个半导体芯片间的元件电连接,而使用被称为tsv(through

‑

silicon via,硅穿孔)的贯通电极。tsv贯通衬底而将该衬底的元件与其他衬底的元件电连接。为了不对元件的特性造成影响,期望tsv的寄生电阻及寄生容量较小。

[0007]

然而,tsv本身由金属形成,虽然为低电阻,但形成在衬底上的tsv用的接触孔的纵横比较高。因此,存在接触孔底部上的tsv与配线的接触面积变小,tsv与配线的接触电阻变高的问题。

技术实现要素:

[0008]

本发明的实施方式提供一种能够减小贯通电极与半导体元件之间的接触电阻的半导体装置及其制造方法。

[0009]

本实施方式的半导体装置具备半导体衬底,所述半导体衬底具有第1面及第2面,所述第1面具有半导体元件,所述第2面位于该第1面的相反侧。第1绝缘膜设置在半导体衬底的第1面上。导电体设置在第1绝缘膜上。金属电极设置在第1面与第2面之间,贯通半导体衬底并与导电体接触。第2绝缘膜设置在金属电极与半导体衬底之间。第1绝缘膜与第2绝缘膜的边界面位于较半导体衬底的第1面更靠导电体侧,且随着向金属电极的中心部靠近以向导电体接近的方式倾斜。

附图说明

[0010]

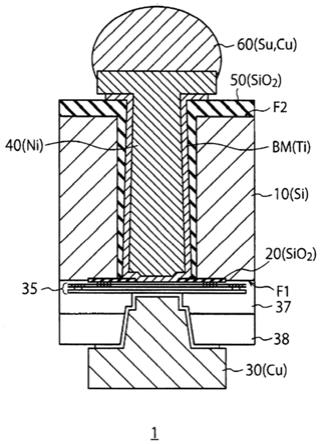

图1是表示第1实施方式的半导体芯片的构成例的截面图。

[0011]

图2是更详细地表示较配线构造更靠第2面侧的构造的截面图。

[0012]

图3是表示边界面未倾斜的构造的截面图。

[0013]

图4是表示第1实施方式的半导体芯片的制造方法的一例的截面图。

[0014]

图5是继图4之后表示半导体芯片的制造方法的截面图。

[0015]

图6是继图5之后表示半导体芯片的制造方法的截面图。

[0016]

图7是继图6之后表示半导体芯片的制造方法的截面图。

[0017]

图8是表示第2实施方式的半导体芯片的构成例的截面图。

[0018]

图9是表示第2实施方式的半导体芯片的制造方法的一例的截面图。

[0019]

图10是继图9之后表示半导体芯片的制造方法的一例的截面图。

[0020]

图11是继图10之后表示半导体芯片的制造方法的一例的截面图。

具体实施方式

[0021]

以下,参照图式对本发明之实施方式进行说明。本实施方式并不限定本发明。在以下实施方式中,半导体衬底的上下方向表示以设置有半导体元件的面或其相反侧的面为上表面时的相对方向,有与依据重力加速度的上下方向不同的情况。

[0022]

(第1实施方式)

[0023]

图1是表示第1实施方式的半导体芯片的构成例的截面图。半导体芯片1可为具有例如nand(与非)型eeprom(electrically erasable and programmable read

‑

only memory,电可擦除可编程只读存储器)等的半导体芯片。在图1中表示半导体芯片1的tsv及其周边部。

[0024]

半导体芯片1具备半导体衬底10、sti(shallow trench isolation,浅沟槽隔离)20、焊垫(凸块)30、tsv40、间隔膜50及凸块60。

[0025]

半导体衬底10例如为硅衬底,薄膜化为例如约30μm以下。半导体衬底10具有第1面f1及位于第1面f1的相反侧的第2面f2。半导体衬底10的第1面f1具有形成半导体元件的主动区域、及将主动区域间电分离的sti(shallow trench isolation)20。在主动区域形成有存储单元阵列、晶体管、电阻元件、电容元件等半导体元件(未图示)。在sti20使用例如氧化硅膜等绝缘膜。在sti20上未设置半导体元件,但设置有将半导体元件与tsv40电连接的焊垫30及配线构造35。以下,也将焊垫30与配线构造35统称为导电体30、35。在半导体衬底10的第2面f2上未设置半导体元件及配线,但设置有与tsv40电连接的凸块60等。

[0026]

作为第1绝缘膜的sti20设置在半导体衬底10的第1面f1上。如上所述,在sti20使用例如氧化硅膜等绝缘膜。

[0027]

导电体30、35设置在sti20上,与设置在半导体衬底10的第1面f1上的半导体元件(例如晶体管)电连接。焊垫30使用例如钨或钛等低电阻金属。在配线构造35使用例如多晶硅、所述低电阻金属等。

[0028]

作为金属电极的tsv40及障壁金属bm设置在半导体衬底10的第1面f1与第2面f2之间,贯通半导体衬底10。进而,tsv40及障壁金属bm贯通sti20而与导电体30、35电连接。由此,tsv40及障壁金属bm将与位于第1面f1侧的导电体30、35的电性连接延长至第2面f2侧为止。tsv40使用例如镍等低电阻金属。障壁金属bm设置在间隔膜50的侧面。障壁金属bm使用例如ti、ta、ru或其积层膜。以下,也将tsv40及障壁金属bm统称为金属电极40、bm。再者,只要能够将tsv40良好地埋入于接触孔ch内,则并不一定必需设置障壁金属bm。

[0029]

作为第2绝缘膜的间隔膜50设置在金属电极40、bm与半导体衬底10之间,将金属电极40、bm与半导体衬底10电分离。此外,间隔膜50也设置在半导体衬底10的第2面f2上。间隔膜50使用例如氧化硅膜等绝缘膜。

[0030]

凸块60在半导体衬底10的第2面f2侧设置在tsv40上。凸块60使用例如锡、铜等金

属。

[0031]

图2是更详细地表示较配线构造35更靠第2面f2侧的构造的截面图。在图2中,为了容易理解,示意性地强调表示tsv40或障壁金属bm与导电体30、35的连接部分。

[0032]

此处,sti20及间隔膜50的边界面fb1较半导体衬底10的第1面f1更靠导电体30、35侧,且随着靠近tsv40的中心部以接近导电体30、35的方式倾斜。也就是说,边界面fb1较半导体衬底10的第1面f1更靠近导电体30、35,且朝向tsv40的中心部,向远离半导体衬底10的方向倾斜。进而换言之,边界面fb1位于半导体衬底10与tsv40之间,朝向设置有tsv40的接触孔ch的中心部(tsv40的中心部)而逐渐向导电体30、35靠近。因此,在具有接触孔ch的区域,sti20的厚度随着向tsv40的中心部靠近而变薄。

[0033]

此外,伴随边界面fb1的倾斜,tsv40或障壁金属bm与间隔膜50或sti20之间的边界面fb2也沿边界面fb1倾斜。例如,边界面fb2在半导体衬底10的第1面f1的附近(tsv40的上部)具有略倒锥形,或者成为与第1面f1大致垂直的面。边界面fb2在半导体衬底10的第2面f2的附近的边界面fb1的正上方,向tsv40的中心部靠近,随着向tsv40的中心部靠近,以向导电体30、35接近的方式倾斜。进而,边界面fb2向与第1面f1垂直的方向靠近并到达至导电体30、35为止。

[0034]

如此,根据本实施方式,半导体衬底10与金属电极40、bm之间的间隔膜50的内侧面几乎无与第1面f1大致平行的面,而在与第1面f1大致垂直的方向上延伸或者平滑地倾斜。

[0035]

图3是表示边界面fb1未倾斜的构造的截面图。假设在像图3那样边界面fbl未倾斜,而与半导体衬底10的第1面f1或第2面f2大致平行(例如,与第2面f2为大致同一平面)的情况下,边界面fb2也与半导体衬底10的第1面f1或第2面f2大致平行。在此情况下,间隔膜50正下方的sti20的厚度与半导体衬底10之下的sti20的厚度大致相同。因此,接触孔ch的底面积变小,tsv40及障壁金属bm与导电体30、35之间的接触电阻变高。此外,在边界面fbl未倾斜而与第2面f2为大致同一平面时,像图3那样,间隔膜50的内侧面具有级差st。当在间隔膜50的内侧面有级差st时,设置在间隔膜50的内侧面的障壁金属的覆盖变差,难以填充tsv40的金属材料。

[0036]

相对于此,根据本实施方式,像图2那样,半导体衬底10与金属电极40、bm之间的间隔膜50的内侧面几乎无与第1面f1大致平行的面,而在与第1面f1大致垂直的方向上延伸或者平滑地倾斜。由此,在接触孔ch下方的区域,sti20的厚度随着向金属电极40、bm的中心部靠近而变薄。在此情况下,间隔膜50与sti20的膜厚的和随着向接触孔ch的中心部靠近而变薄。由此,当对接触孔ch的底部进行蚀刻时,接触孔ch变得容易贯通间隔膜50及sti20。因此,即便是短时间的过蚀刻,形成在间隔膜50及sti20上的接触孔ch的直径也会变大。由此,接触孔ch的底面积相对变大,金属电极40、bm与导电体30、35之间的接触电阻变低。此外,在对接触孔ch的底部进行蚀刻时,可缩短过蚀刻的时间,因此,能够抑制接触孔ch穿透配线构造35。

[0037]

进而,半导体衬底10与金属电极40、bm之间的间隔膜50的内侧面在与第1面f1大致垂直的方向上延伸或者平滑地倾斜。由此,在间隔膜50的内侧面无级差st,障壁金属bm的覆盖变得良好。因此,也容易填充tsv40的金属材料。

[0038]

其次,对本实施方式的半导体芯片1的制造方法进行说明。

[0039]

图4~图7是表示第1实施方式的半导体芯片的制造方法的一例的截面图。为了容

易理解tsv40或障壁金属bm与导电体30、35的连接部分的形成方法,图5~图7与图2相同地表示示意性的截面图。

[0040]

以下,主要说明在半导体芯片1上形成tsv40的方法。

[0041]

首先,在半导体衬底10的第1面f1上形成sti20而决定主动区域。半导体衬底10例如为硅衬底。sti20例如为氧化硅膜。其次,在主动区域形成半导体元件(未图示)。半导体元件可为例如存储单元阵列、晶体管、电阻元件、电容元件等。在形成半导体元件时,在sti20上形成例如配线构造35。半导体元件及配线构造35由绝缘膜37、38被覆。其次,焊垫30以与配线构造35连接的方式形成。因此,在sti20上形成导电体30、35。

[0042]

其次,使用光刻技术及rie(reactive ion etching,反应性离子蚀刻)法,从位于与第1面f1为相反侧的半导体衬底10的第2面f2对半导体衬底10进行蚀刻。也就是说,将光阻层80用作掩膜,从与形成有半导体元件的第1面f1为相反侧的第2面f2(背面)形成接触孔ch。由此,形成从第2面f2到达至第1面f1的接触孔ch。为了使tsv40与导电体30、35连接,接触孔ch形成在sti20的区域中存在导电体30、35的区域上。通过形成接触孔ch而使sti20露出。

[0043]

其次,像图5那样,使用rie法对位于接触孔ch的底面的st120的一部分进行蚀刻。此时,sti20的材料(例如,氧化硅膜)的蚀刻气体与半导体衬底10的材料(例如,硅)的蚀刻气体不同。例如,硅的蚀刻气体为sf6、sif4、cf4、c4f8、ar、hbr、o2气体或其等的混合气体等。氧化硅膜的蚀刻气体为cf4、chf3、ar、o2气体或其等的混合气体等。因此,sti20的蚀刻步骤与半导体衬底10的蚀刻步骤不同。例如,可在半导体衬底10的蚀刻后,使用与进行半导体衬底10的蚀刻的装置不同的装置执行sti20的蚀刻。或者也可在与半导体衬底10的蚀刻为同一装置内执行sti20的蚀刻,但需要更换蚀刻气体。

[0044]

相较于接触孔ch的底部的中心部,蚀刻气体的离子更难以到达其端部,因此,像图5那样,在接触孔ch的底部,sti20的中心部的膜厚t20c相较于其端部的膜厚t20e变薄。由此,接触孔ch的底面呈碗型凹陷。也就是说,接触孔ch的底面较半导体衬底10的第1面f1更向导电体30、35侧凹陷,且随着向接触孔ch的中心部靠近而以向导电体30、35接近的方式倾斜。因此,sti20的厚度随着向接触孔ch的中心部靠近而变薄。

[0045]

去除光阻层80后,像图6那样,使用cvd(chemical vapor deposition,化学气相沉积)法或ald(atomic layer deposition,原子层沉积)法,在接触孔ch的内侧面、底面及半导体衬底10的第2面f2上形成间隔膜50。间隔膜50沿接触孔ch的内表面形成,因此,形成在接触孔ch的底面上的间隔膜50沿接触孔ch的碗型以良好的覆盖形成在半导体衬底10及sti20上。

[0046]

此外,间隔膜50与接触孔ch的底面大致相同地呈碗型凹陷。也就是说,接触孔ch的底面的间隔膜50随着向接触孔ch的中心部靠近而以接近导电体30、35的方式倾斜。伴随于此,sti20及间隔膜50的边界面fb1也较半导体衬底10的第1面f1更靠导电体30、35侧,且随着向接触孔ch的中心部靠近而以向导电体30、35接近的方式倾斜。也就是说,边界面fbl较半导体衬底10的第1面f1更靠近导电体30、35,且朝向填充tsv40的接触孔ch的中心部而向远离半导体衬底10的方向倾斜。

[0047]

此外,实际上,接触孔ch的纵横比相对较高,因此,形成在接触孔ch的开口部的间隔膜50相较于形成在接触孔ch的内部的间隔膜50变厚。因此,像图6那样,间隔膜50在接触

孔ch的开口端在与第1面f1大致平行的方向上突出。以下,也将间隔膜50在接触孔ch的开口端突出的部分称为悬突部分oh。这种间隔膜50的悬突部分oh使接触孔ch的开口直径比接触孔ch的中间部分的直径稍窄。像图6那样,如果将间隔膜50的悬突部分oh的接触孔ch的开口直径设为φ1,将接触孔ch的中间部分的直径设为φ2,那么φ1<φ2。

[0048]

其次,像图7那样,将位于接触孔ch的内侧面及半导体衬底10的第2面f2上的间隔膜50用作掩膜,利用rie法对接触孔ch的底部的间隔膜50及sti20进行蚀刻。由此,接触孔ch贯通间隔膜50及sti20并到达至位于sti20之下的导电体30、35。也就是说,接触孔ch延长至sti20之下的导电体30、35。此时,如上所述,通过间隔膜50的悬突部分oh,接触孔ch的开口直径φ1相较于接触孔ch的中间部分的直径φ2变窄。将间隔膜50的悬突部分oh作为掩膜而对接触孔ch的底部的间隔膜50及sti20进行蚀刻。因此,形成在间隔膜50及sti20上的下部的接触孔ch的直径大致成为φ1。

[0049]

另一方面,接触孔ch的底面呈碗型凹陷,sti20及间隔膜50的中心部的膜厚的和ttlc相较于其等的端部的膜厚的和ttie变薄。因此,间隔膜50及sti20变得容易贯通,即便为短时间的过蚀刻,也能够相对增大形成在间隔膜50及sti20上的接触孔ch的直径φc。由此,接下来形成的tsv40与导电体30、35之间的接触电阻变低。此外,能够使过蚀刻进行的时间短,因此,能够抑制接触孔ch穿透配线构造35。进而,由于接触孔ch的底面呈碗型凹陷,故而接触孔ch的内侧面几乎无与第1面f1大致平行的面,而在与第1面f1大致垂直的方向上延伸或者平滑地倾斜。也就是说,接触孔ch的内侧面成为几乎无级差的平滑的倾斜面。因此,以下说明的障壁金属bm及tsv40的覆盖变得良好。

[0050]

其次,像图2那样,在接触孔ch内形成障壁金属bm,沉积tsv40的金属材料。由此,在接触孔ch内形成金属电极40、bm。障壁金属bm使用例如ti、ta、ru或其积层膜。tsv40使用例如镍等金属材料。由此,能够使金属电极40、bm与导电体30、35连接,且能够向第2面f2侧引出。此时,如上所述,接触孔ch的内侧面成为几乎无级差的平滑的倾斜面。由此,障壁金属bm及tsv40的金属材料的覆盖变得良好。

[0051]

其次,使用光刻技术及rie法,对tsv40及障壁金属bm进行加工。由此,去除位于第2面f2(场)上的tsv40及障壁金属bm的材料。

[0052]

其次,像图2那样,使用镀覆法等,在tsv40上形成凸块60。凸块60使用例如锡等。由此,完成本实施方式的半导体芯片1。再者,其后,可将半导体芯片1与其他半导体芯片积层,并经由tsv40及凸块60等与其他半导体芯片电连接。

[0053]

如此,根据本实施方式,在对半导体衬底10进行蚀刻之后且形成间隔膜50之前,对接触孔ch底部的sti20的上部进行蚀刻。由此,接触孔ch的底部呈碗型凹陷,间隔膜50的覆盖变得良好。进而,间隔膜50也与接触孔ch的底面大致相同地呈碗型凹陷。由此,sti20及间隔膜50的厚度随着向接触孔ch或tsv40的中心部靠近而变薄,因此,在对接触孔ch的底部进行蚀刻时,接触孔ch变得容易贯通间隔膜50及sti20。因此,形成在间隔膜50及sti20上的接触孔ch的直径相对变大,金属电极40、bm与导电体30、35之间的接触电阻变低。而且,可缩短过蚀刻,因此,能够抑制接触孔ch穿透配线构造35。进而,在间隔膜50的内侧面无级差st,因此,障壁金属bm或tsv40的金属材料的覆盖变得良好。

[0054]

(第2实施方式)

[0055]

图8是表示第2实施方式的半导体芯片的构成例的截面图。第2实施方式的半导体

芯片1在tsv40或间隔膜50等的形状方面与第1实施方式不同。第2实施方式的其他构成可与第1实施方式的对应的构成相同。再者,图8也与图2相同地,为了容易理解,而示意性地强调表示tsv40或障壁金属bm与导电体30、35的连接部分。

[0056]

在第2实施方式的半导体芯片1中,在与半导体衬底10的第1面f1及第2面f2大致垂直的方向的剖面上,将位于金属电极40、bm的两侧的金属电极40、bm与sti20之间的边界面设为第1边界面fb11及第2边界面fb12,将位于金属电极40、bm的两侧的间隔膜50与半导体衬底10的边界面设为第3边界面fb13及第4边界面fb14。此时,第1边界面fb11与第2边界面fb12之间的中心c11_12,从第3边界面fb13与第4边界面fb14之间的中心c13_14向第1方向d1偏移。

[0057]

此外,位于半导体衬底10的第2面f2侧的金属电极40、bm与间隔膜50之间的边界面中位于第1方向d1上的边界面,在第2面f2侧的端部e21弯曲(带弧度)。也就是说,间隔膜50的上表面f50t1与侧面f50s1之间的端部e21以倒角的方式切削,相对于该上表面f50t1及侧面f50s1两者倾斜。另一方面,金属电极40、bm与间隔膜50之间的边界面中位于与第1方向d1为反方向的方向上的边界面,不在第2面f2侧的端部e22弯曲。也就是说,间隔膜50的上表面f50t2与侧面f50s2之间的端部e22未被倒角,与该上表面f50t2或侧面f50s2的任一者成为大致同一平面。

[0058]

如此,从tsv40的中心观察,第1边界面fb11与第2边界面fb12之间的中心c11_12的偏离方向d1,与设置有弯曲的边界面fb21的方向成为大致同一方向。这种构造可通过如下的半导体芯片1的制造方法形成。

[0059]

图9~图11是表示第2实施方式的半导体芯片的制造方法的一例的截面图。以下,主要说明在半导体芯片1上形成tsv40的方法。

[0060]

至形成接触孔ch为止的步骤可与第1实施方式相同。再者,在第2实施方式中,在该阶段不执行位于接触孔ch的底面的sti20的蚀刻。因此,接触孔ch的底面为与第1或第2面f1、f2大致平行的状态。

[0061]

其次,像图9那样,使用cvd法或ald法,在接触孔ch的内侧面、该接触孔ch的底面及半导体衬底10的第2面f2形成间隔膜50。此时,接触孔ch的纵横比相对较高,因此,间隔膜50在接触孔ch的开口端具有悬突部分oh。再者,如下所述,在第2面f2上的间隔膜50上形成抗蚀膜70。由此,第2面f2上的间隔膜50的膜厚增厚抗蚀膜70的厚度的量,包含间隔膜50及抗蚀膜70的掩膜材的膜厚充分变厚。由此,间隔膜50不需要考虑作为掩膜材的功能而形成得过厚,相对较薄即可。通过使间隔膜50的膜厚较薄,间隔膜50的悬突部分oh变小。由此,能够使接触孔ch的开口直径φ1相对变大。由此,结果是金属电极40、bm与导电体30、35的接触面积变大,接触电阻变小。

[0062]

其次,像图10那样,使用光刻技术,在位于半导体衬底10的第2面f2上的间隔膜50上形成抗蚀膜70作为掩膜材的一部分。当将抗蚀膜70涂布在半导体衬底10的第2面f2上时,抗蚀膜70可进入至接触孔ch内,也可不进入至接触孔ch内。通过抗蚀膜70的曝光与显影而去除位于接触孔ch上的抗蚀膜70,残留其他抗蚀膜70。由此,像图10那样,抗蚀膜70的开口部op70以与接触孔ch的开口部opch大致对应的方式形成。

[0063]

然而,抗蚀膜70的开口部op70的中心c70不与接触孔ch的开口部的中心cch1一致。因此,像图10那样,从第2面f2的上方观察时,间隔膜50的一端部e22被抗蚀膜70遮掩,另一

端部e21从抗蚀膜70露出。例如,抗蚀膜70的d1方向的端部e70_1相较于间隔膜50的d1方向的端部e21更向d1方向引退。另一方面,抗蚀膜70的与d1方向为相反方向的端部e70_2相较于间隔膜50的与d1方向为相反方向的端部e22向d1方向突出。端部e21或抗蚀膜70的端部e70_2的突出量例如为约1μm。

[0064]

从第2面f2的上方观察时,抗蚀膜70的端部e70_1优选位于间隔膜50的端部e21与半导体衬底10的端部e11之间。由此,能够抑制间隔膜50的端部e21被过度蚀刻,从而能够抑制半导体衬底10与金属电极40、bm电性短路。进而优选端部e70_1比间隔膜50的端部e21与半导体衬底10的端部e11之间的中间位置更靠近端部e21。由此,能够更确实地抑制半导体衬底10与金属电极40、bm的电性短路。

[0065]

此外,如上所述,当在第2面f2上的间隔膜50之上形成抗蚀膜70时,能够使间隔膜50的膜厚较薄。由此,能够缩小间隔膜50的悬突部分oh。这有助于金属电极40、bm与导电体30、35的接触面积的扩大。

[0066]

其次,像图11那样,将抗蚀膜70及间隔膜50用作掩膜,利用rie法对位于接触孔ch的底部的间隔膜50及sti20进行蚀刻。此时,间隔膜50的端部e22被抗蚀膜70遮掩,因此,未被蚀刻。因此,端部e22保持90度或者较此为锐角的状态。另一方面,间隔膜50的端部e21从抗蚀膜70露出,因此,被蚀刻。由此,间隔膜50的端部e21以倒角地方式切削而带弧度。间隔膜50的端部e21相对于该上表面f50t1及侧面f50s1两者倾斜。

[0067]

此外,在接触孔ch的底部,间隔膜50及sti20将向d1方向偏移的抗蚀膜70或间隔膜50作为掩膜进行蚀刻。因此,形成在间隔膜50及sti20上的下部的接触孔ch的中心cch2,从形成在半导体衬底10上的上部的接触孔ch的中心cch1向d1方向偏移。该偏移量与抗蚀膜70的开口部的中心c70相对于接触孔ch的开口部的中心cch1的偏移量大致相同。如此,第1边界面fb11与第2边界面fb12之间的中心,从第3边界面fb13与第4边界面fb14之间的中心向第1方向d1偏移。

[0068]

其次,以第1实施方式所说明的方式形成障壁金属bm、tsv40及凸块60。由此,完成图8所示的第2实施方式的半导体芯片1。

[0069]

根据第2实施方式的制造方法,在形成间隔膜50之后,在第2面f2上形成抗蚀膜70。由此,包含间隔膜50与抗蚀膜70的掩膜材的膜厚在第2面f2上充分变厚,能够使间隔膜50的膜厚较薄。通过使间隔膜50的膜厚较薄而缩小悬突部分oh,接触孔ch的开口直径φ1变大。由此,金属电极40、bm与导电体30、35的接触面积变大,可减小其等的接触电阻。此外,通过缩小悬突部分oh而缓和间隔膜50的倒锥形状,因此,障壁金属bm或tsv40的金属材料的覆盖变得良好。

[0070]

第2实施方式也可与第1实施方式组合。由此,金属电极40、bm与导电体30、35的接触面积进一步增大,且障壁金属bm或tsv40的金属材料的覆盖变得更好。

[0071]

对本发明的几个实施方式进行了说明,但这些实施方式是作为例而提示的,并不意欲限定发明的范围。这些实施方式可通过其他各种形态实施,可在不脱离发明的主旨的范围内,进行各种省略、替换、变更。这些实施方式或其变化与包含在发明的范围或主旨内同样地包含在权利要求书中所记载的发明及其均等的范围内。

[0072]

[符号的说明]

[0073]1ꢀꢀꢀꢀꢀ

半导体芯片

[0074]

10

ꢀꢀꢀꢀ

半导体衬底

[0075]

20

ꢀꢀꢀꢀ

sti

[0076]

30

ꢀꢀꢀꢀ

焊垫

[0077]

35

ꢀꢀꢀꢀ

配线构造

[0078]

bm

ꢀꢀꢀꢀ

障壁金属

[0079]

40

ꢀꢀꢀꢀ

tsv

[0080]

50

ꢀꢀꢀꢀ

间隔膜

[0081]

60

ꢀꢀꢀꢀ

凸块

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。