一种衬底电荷耦合的1200v体硅ldmos及其制备方法

技术领域

1.本发明涉及功率半导体器件技术领域,涉及一种衬底电荷耦合的1200v体硅ldmos(横向双扩散mos晶体管)及其制备方法。

背景技术:

2.随着功率半导体技术的发展,高压集成电路被广泛应用于电源开关、电机驱动、汽车电子和新能源发电等领域。而高压集成路中很关键的一项技术设计就是高压ldmos器件的设计。高压体硅ldmos由于其工艺相对简单且与其他工艺相兼容的优点,在高压集成电路中得到了广泛的应用。对于1200v的高压集成电路,就需要耐压等级为1200v的ldmos来实现电平移位的功能。由于1200v耐压等级的ldmos耐压要求高,因此在设计1200v时的时需要从横向耐压和纵向耐压两个方面来考虑。对于横向耐压的设计要求,可以通过采用场板、resurf技术和场限环等终端技术来提高耐压。对于纵向耐压的设计,目前最常见的技术还是增加衬底电阻率来满足纵向耐压的需求。但是高衬底电阻率的衬底材料又有价格昂贵和均匀性差的缺点。因此具有高耐压能力的1200v体硅ldmos急需被研究。

技术实现要素:

3.技术问题:本发明针对上述问题,提出一种衬底电荷耦合的1200v体硅ldmos及其制备方法,用于制备具有高耐压能力的1200v体硅ldmos。

4.技术方案:本发明的一种衬底电荷耦合的1200v体硅ldmos包括p型衬底,在p型衬底中设有n型sn埋层,在n型sn埋层上方且靠近漏极侧设有n型dn埋层,在n型sn埋层上方且靠近源极侧设有5个p型bp埋层,p型bp埋层和n型dn埋层上方设有p型p

‑

well体区、n型漂移区和n型n

‑

well缓冲层,其中p型p

‑

well体区内设有源极n型重掺杂区和源极p型重掺杂区,n型n

‑

well缓冲层内设有漏极n型重掺杂区;n型漂移区上方设有场氧化层、多晶硅栅、二氧化硅氧化层和金属场板,其中金属场板横跨于场氧化层上方,多晶硅栅自源极n型重掺杂区上方经过p型p

‑

well体区延伸至场氧化层上方;源极n型重掺杂区和源极p型重掺杂区通过源极金属和源极相连,漏极n型重掺杂区通过漏极金属和漏极相连。

5.所述的n型sn埋层通过两次外延离子注入形成,两次外延的厚度分别为6.0~8.0um。

6.所述的n型sn埋层的离子注入的窗口宽度为2.0~2.5um,相邻离子注入窗口的间距为16.0~18.0um。

7.本发明的一种衬底电荷耦合的1200v体硅ldmos的制备方法的具体步骤如下:

8.步骤1:在p型衬底进行n型离子注入后,第一次生长厚度为8um的p型外延层;

9.步骤2:在第一次生长的p型外延层进行n型离子注入后,第二次生长厚度为8um的p型外延层;

10.步骤3:在第二次生长的p型外延层进行n型离子注入后,退火形成n型sn埋层,接着第三次生长厚度为6um的p型外延层;

11.步骤4:在第三次生长的p型外延层进行n型离子注入后,退火形成n型dn埋层,在第三次生长的p型外延层进行p型离子注入后,退火形成p型bp埋层,接着第四次生长厚度为6um的p型外延层;

12.步骤5:在第四次生长的p型外延层进行n型离子注入后,退火形成n型漂移区,接着继续进行n型离子注入,退火形成n型n

‑

well缓冲层;

13.步骤6:在第四次生长的p型外延层进行p型离子注入后,退火形成p型p

‑

well体区;

14.步骤7:在硅区表面氧化刻蚀形成场氧化层,氧化刻蚀形成栅氧化层,淀积刻蚀形成多晶硅栅;

15.步骤8:在硅区表面自对准n型离子注入形成源极n型重掺杂区和漏极n型重掺杂区;在硅区表面自对准p型离子注入形成源极p型重掺杂区;

16.步骤9:在硅区表面氧化生长二氧化硅氧化层,刻蚀二氧化硅氧化层形成接触孔,然后淀积金属铝,刻蚀金属铝形成器件的漏极接触、源极接触和金属场板;

17.步骤10:在硅区表面继续氧化生长二氧化硅氧化层,刻蚀二氧化硅氧化层形成接触孔,然后淀积金属铝,刻蚀金属铝形成器件的漏极接触与源极接触;

18.步骤11:在二氧化硅氧化层上淀积金属铝,刻蚀金属铝形成器件的漏极与源极。

19.有益效果:与现有技术相比,本发明结构具有如下优点:

20.1.本发明通过衬底电荷耦合结构,在低衬底电阻率衬底材料下,即可实现1200v的耐压需求。在低衬底电阻率衬底材料下,器件的纵向耐压(bvv)小于1200v,虽然通过拉长器件的漂移区长度和采用终端技术可以提高器件的横向耐压(bvl),使bvl的值大于1200v,但是bvv<1200v<bvl,因此器件在不到1200v时就在体内击穿,使器件最终的bv<1200v,因此要使体硅ldmos的bv>1200v,就需要采用高衬底电阻率的衬底材料。通过采用具有电荷耦合作用的sn埋层,可以在低衬底电阻率的基础上,使漏端纵向电场分布从三角形分布往矩形分布变化,进而提高器件的纵向耐压。因此,本发明结构在低衬底电阻率的衬底材料下即可实现1200v的耐压需求。

21.2.本发明方案通过使用低衬底电阻率的衬底材料,降低了衬底材料的成本,提高了衬底材料的均匀性。同时本发明方案和目前的工艺完全兼容,没有增加制造工艺的难度。

附图说明

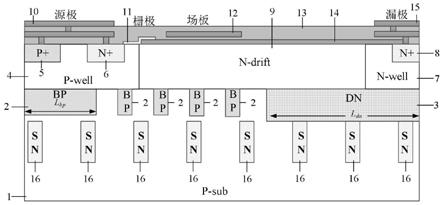

22.图1所示为本发明的1200v体硅ldmos结构图。

23.图2所示为本发明结构和传统结构漏端纵向电场分布示意图。

24.图3所示为本发明结构和传统机构击穿特性图。

25.图中有:p型衬底1、p型bp埋层2、n型dn埋层3、p型p

‑

well体区4、源极p型重掺杂区5、源极n型重掺杂区6、n型n

‑

well缓冲层7、漏极n型重掺杂区8、n型漂移区9、源极金属10、多晶硅栅11、金属场板12、二氧化硅氧化层13、场氧化层14、漏极金属15、n型sn埋层16。

具体实施方式

26.下面结合附图,对本发明做详细说明。

27.本发明的一种衬底电荷耦合的1200v体硅ldmos,包括p型衬底1,在p型衬底1上设有n型sn埋层16,在n型sn埋层16上方且靠近漏极侧设有n型dn埋层3,在n型sn埋层16上方且

靠近源极侧设有5个p型bp埋层2。p型bp埋层2和n型dn埋层3上方设有p型p

‑

well体区4、n型漂移区9和n型n

‑

well缓冲层7,其中p型p

‑

well体区4内设有源极n型重掺杂区6和源极p型重掺杂区5,n型n

‑

well缓冲层7内设有漏极n型重掺杂区8。n型漂移区9上方设有场氧化层14、多晶硅栅11、二氧化硅氧化层14和金属场板12,其中金属场板12横跨于场氧化层14上方,多晶硅栅11自源极n型重掺杂区6上方经过p型p

‑

well体区4,延伸至场氧化层14上方。源极n型重掺杂区6和源极p型重掺杂区5通过源极金属10和源极相连,漏极n型重掺杂区8通过漏极金属15和漏极相连。

28.所述的n型sn埋层16通过两次外延离子注入形成,两次外延的厚度都为8um。

29.所述的n型sn埋层16的离子注入的窗口宽度为2.0~2.5um,相邻离子注入窗口的间距为16.0~18.0um。

30.本发明的一种衬底电荷耦合的1200v体硅ldmos的制备方法具体步骤如下:

31.步骤1:在p型衬底1进行n型离子注入后,第一次生长厚度为8um的p型外延层;

32.步骤2:在第一次生长的p型外延层进行n型离子注入后,第二次生长厚度为8um的p型外延层;

33.步骤3:在第二次生长的p型外延层进行n型离子注入后,退火形成n型sn埋层16,接着第三次生长厚度为6um的p型外延层;

34.步骤4:在第三次生长的p型外延层进行n型离子注入后,退火形成n型dn埋层3,在第三次生长的p型外延层进行p型离子注入后,退火形成p型bp埋层2,接着第四次生长厚度为6um的p型外延层;

35.步骤5:在第四次生长的p型外延层进行n型离子注入后,退火形成n型漂移区9,接着继续进行n型离子注入,退火形成n型n

‑

well缓冲层7;

36.步骤6:在第四次生长的p型外延层进行p型离子注入后,退火形成p型p

‑

well体区4;

37.步骤7:在硅区表面氧化刻蚀形成场氧化层14,氧化刻蚀形成栅氧化层,淀积刻蚀形成多晶硅栅11;

38.步骤8:在硅区表面自对准n型离子注入形成源极n型重掺杂区6和漏极n型重掺杂区8;在硅区表面自对准p型离子注入形成源极p型重掺杂区5;

39.步骤9:在硅区表面氧化生长二氧化硅氧化层13,刻蚀二氧化硅形成接触孔,然后淀积金属铝,刻蚀金属铝形成器件的漏极接触、源极接触和金属场板;

40.步骤10:在硅区表面继续氧化生长二氧化硅氧化层13,刻蚀二氧化硅形成接触孔,然后淀积金属铝,刻蚀金属铝形成器件的漏极接触与源极接触;

41.步骤11:在二氧化硅氧化层13上淀积金属铝,刻蚀金属铝形成器件的漏极与源极。

42.下面结合附图对本发明做进一步说明。

43.对于1200v体硅ldmos,其耐压由纵向耐压(bvv)和横向耐压(bvl)两部分组成。当bvv<1200v<bvl时,此时器件的击穿电压bv<1200v,且此时的击穿点位于器件体内。当bvl<1200v<bvv时,此时器件的击穿电压bv<1200v,且此时的击穿点位于器件表面。因此要使器件的击穿电压bv>1200v,需要满足bvv>1200v且bvl>1200v。对于器件的纵向耐压,主要由衬底的电阻率决定,且衬底的电阻率越高,器件的纵向耐压越高。本发明提出的衬底电荷耦合的1200v体硅ldmos在传统1200v体硅ldmos的基础上,增加了由三次离子注入形成的n型sn

埋层16。sn埋层16的引入,可以辅助p型衬底1和sn埋层16之间的耗尽,促使纵向电场的分布由三角形电场分布往矩形电场分布过渡。图2所示为本发明结构和传统结构漏端的电场分布示意图,如图所示,本发明结构的纵向电场分布和传统结构相比,更加趋近于矩形分布,电场分布围成的线下面积更大,因此本发明结构具有更高的纵向耐压。在保持漂移区长度以及终端设计不变的情况下,本发明结构由于纵向耐压的提高,器件的击穿电压得到明显的提升。如图3所示,在相同的衬底电阻率情况下,本发明结构的击穿电压为1529v,传统结构的击穿电压为1094v,同比提高39.7%。

44.同时sn埋层采用的外延离子注入技术和目前的生产工艺完全兼容,可以直接利用目前的生产工艺,并没有增加生产工艺的难度,具有一定的可行性。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。