1.本发明总体涉及源同步型接口电路,并且特别涉及具有用于选择源端延迟(dos)和目的地端延迟(dod)定时的增强的可配置性的源同步型接口。

背景技术:

2.请参阅图1,其中示出了源同步型接口的框图。第一设备10与第二设备12互连。在该图示中,第一设备10起发送器的作用,并且第二设备12起接收器的作用。作为示例,第一设备10可以包括媒体访问控制(mac)电路,并且第二设备12可以包括物理层(phy)电路。发送器(第一)设备10通过包括一条或多条数据线16d和时钟线16c的有线互连16发送数据(txdata)和时钟(txclk)两者。例如,线16d、16c可以各自包括单根物理配线(参考公共地),或者可选地,各自支持使用两根物理配线的互补(或差分)信令。

3.为了在第二设备12处实现数据txdata的正确捕获,在第二设备12处用于数据捕获的时钟(这里称为目的地时钟dstclk)优选地与在第一设备10处用于产生数据的时钟(称为源时钟srcclk)在相位上偏移90度。这种相位偏移可以通过多种方式实现。

4.图2a示出了一种选择,本文中称为源端延迟(dos),其中第一设备10中的延迟电路20通过对源时钟srcclk施加90度相移来产生传送时钟txclk。源时钟srcclk用于给触发器22提供时钟,触发器22的输入串行地接收要发送的数据(data),并且触发器22的输出产生传送数据txdata以应用到接口16。在该实现中,由于传送时钟txclk已经相对于源时钟srcclk相移90度,因此由第二设备12接收的传送时钟txclk是目的地时钟dstclk。目的地时钟dstclk用于给第二设备12中的触发器24提供时钟,该触发器24的输入串行地接收来自互连16的传送数据txdata,并且触发器24的输出产生数据(data)。

5.图2b示出了另一种选择,本文中称为目的地延迟(dod),其中第二设备12中的延迟电路26通过对经由接口16接收的传送时钟txclk施加90度相移来产生目的地时钟dstclk。第一设备10中的源时钟srcclk用于给触发器22提供时钟,触发器22的输入串行地接收要发送的数据(data),并且触发器22的输出产生传送数据txdata以应用到接口16。在此实现中,传送时钟txclk为源时钟srcclk。目的地时钟dstclk用于给第二设备12中的触发器24提供时钟,该触发器24的输入串行地接收来自互连16的传送数据txdata,并且触发器24的输出产生数据(data)。

技术实现要素:

6.在一种实施方式中,一种系统利用源同步型接口,并且该系统包括:发送器电路;以及接收器电路;其中,发送器电路使用包括数据线和时钟线的源同步型接口耦合到接收器电路。发送器电路包括:第一触发器,具有被配置为接收串行数据的数据输入、被配置为接收源时钟的时钟输入和耦合到数据线的数据输出;第一多路复用器,具有被配置为接收源时钟的第一输入、被配置为接收相移时钟的第二输入、以及耦合到时钟线的第一时钟输出,其中,相移时钟从源时钟偏移90度;以及控制电路,被配置为:如果系统被配置为在接收

器电路中的目的地处对时钟延迟,则控制由第一多路复用器选择源时钟作为通过时钟线发送的传送时钟;如果系统被配置为在发送器电路中的源处对时钟的延迟,则控制由第一多路复用器选择相移时钟作为通过时钟线发送的传送时钟。

7.在一种实施方式中,用于源同步型接口的发送器电路包括:第一触发器,具有被配置为接收串行数据的数据输入、被配置为接收源时钟的时钟输入和耦合到数据线的数据输出;第一多路复用器,具有被配置为接收源时钟的第一输入、被配置为接收相移时钟的第二输入、以及耦合到时钟线的时钟输出,其中,相移时钟从源时钟偏移90度;以及控制电路,被配置为控制由第一多路复用器选择源时钟作为在时钟线上发送的传送时钟用于在目的地配置处对时钟延迟,并且控制由第一多路复用器选择相移时钟作为在时钟线上发送的传送时钟用于在源配置处对时钟延迟。

附图说明

8.为了更好地理解实施例,现在将仅以示例的方式参考附图,其中:

9.图1示出了源同步型接口的框图;

10.图2a示出了源同步型接口的源端延迟(dos)实现;

11.图2b示出了源同步型接口的目的地端延迟(dod)实现;

12.图3示出了源同步型接口的框图;

13.图4示出了图3的发送器设备的更详细的电路实现;以及

14.图5示出了两位约翰逊(johnson)计数器电路的电路图。

具体实施方式

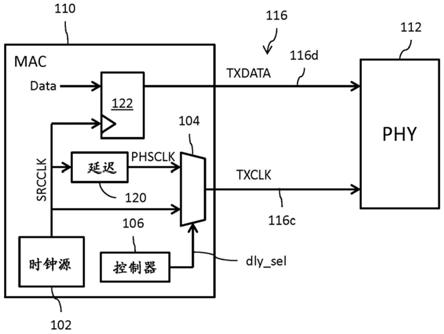

15.请参阅图3,其中示出了源同步型接口的框图。第一设备110与第二设备112互连。在该图示中,第一设备110起发送器的作用,并且第二设备112起接收器的作用。作为示例,第一设备110可以包括媒体访问控制(mac)电路,并且第二设备112可以包括物理层(phy)电路。发送器(第一)设备110通过包括一条或多条数据线116d和时钟线116c的有线互连116发送数据(txdata)和时钟(txclk)两者。例如,线116d、116c可以各自包括单根物理配线(参考公共地),或者可选地,各自支持使用两根物理配线的互补(或差分)信令。

16.发送器(第一)设备110包括时钟发生器(源)电路102,时钟发生器(源)电路102被配置为产生源时钟srcclk。源时钟srcclk用于给触发器122提供时钟,触发器122的输入串行地接收要发送的数据(data),并且触发器122的输出产生传送数据txdata以应用到接口116的数据线116d。如果使用多条数据线116d,则每条线将有一个时钟触发器(clocked flip

‑

flop)122连同多个数据输入。源时钟srcclk还被应用到多路复用器电路104的第一输入和延迟电路120的输入,延迟电路120通过对源时钟srcclk施加90度相移而产生相移时钟phsclk。相移时钟phsclk被施加到多路复用器电路104的第二输入。由多路复用器电路104执行的选择操作由控制信号dly_sel控制。如果控制信号dly_sel处于第一状态,则多路复用器电路104从第一输入中选择源时钟srcclk以通过有线互连116的时钟线116c输出作为传送时钟txclk(这与目的地端时钟延迟(dod)操作一致)。相反地,如果控制信号dly_sel处于第二状态,则多路复用器电路104从第二输入选择相移时钟phsclk以通过有线互连116的时钟线116c输出作为传送时钟txclk(这与时钟的源端延迟(dos)操作一致)。

17.控制信号dly_sel由控制电路106产生。在实施方式中,控制电路106可以包括数据寄存器的一个位,该位取决于时钟上的延迟是由发送器(第一)设备110(即,dos)还是接收器(第二)设备112(即,dod)提供,而被设置为第一状态或第二状态。例如,在时钟的源端延迟(dos)配置中(其中接收器(第二)设备112不包括时钟相移功能),则控制信号dly_sel处于第二状态,使得多路复用器电路104选择相移时钟phsclk作为传送时钟txclk。在时钟的目的地端延迟(dod)配置中(其中接收器(第二)设备112确实包括时钟相移功能),则控制信号dly_sel处于第一状态,使得多路复用器电路104选择源时钟srcclk作为传送时钟txclk。控制信号dly_sel的状态的设置可以由控制电路106自身进行,或者可以由发送器(第一)设备110的另一电路执行并传送到控制电路106。

18.现在参考图4,其示出了发送器(第一)设备110的时钟发生器(源)电路102和延迟电路120的更详细的电路实现。锁相环(pll)电路130以频率fphi产生时钟信号phiclk,频率fphi是接口116的传送时钟txclk的最高所需频率ftx(即fphi=n*ftx)的整数倍n倍。在该实施方式中,由于延迟电路120(如将描述的)执行的进一步的四分频操作,n=4。时钟信号phiclk被应用到多路复用器132的第一输入,并进一步应用到多个分频器电路134的输入。分频器电路134的输出被提供给多路复用器140的相应输入,多路复用器140的分频时钟divclk输出应用到多路复用器132的第二输入。多路复用器132的输出提供选择的时钟selclk。选择的时钟selclk用于对n分频约翰逊计数器电路142进行计时,该计数器电路142输出源时钟srcclk和相移时钟phsclk(在这种情况下,如上所述,具有相对于源时钟srcclk的90度相移),每个时钟具有的频率是选择的时钟selclk的频率的1/n。

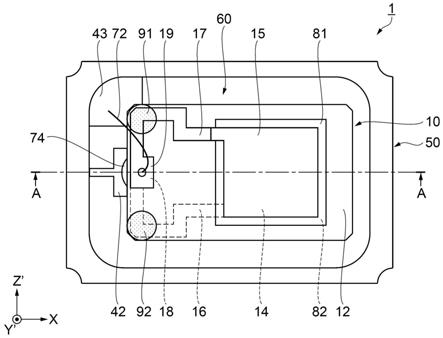

19.由多路复用器电路140执行的选择操作由控制信号speed_sel控制。如果控制信号speed_sel具有第一状态,则多路复用器电路140选择从div/a分频器电路134输出的(被a)分频的时钟信号作为分频时钟divclk应用到多路复用器132的第二输入。如果控制信号speed_sel具有第二状态,则多路复用器电路140选择从div/b分频器电路134输出的(被b)分频的时钟信号作为分频时钟divclk应用到多路复用器132的第二输入。如果控制信号speed_sel具有第三状态,则多路复用器电路140选择从div/c分频器电路134输出的(被c)分频的时钟信号作为分频时钟divclk应用到多路复用器132的第二输入。

20.控制信号speed_sel由控制电路106产生。在实施方式中,控制电路106可包括数据寄存器的另一组位,其根据接口116上的数据通信的期望速度(即速率)被设置为第一状态、第二状态或第三状态(例如,两个位分别设置为<0,0>、<0,1>或<1,0>)。

21.由多路复用器电路132执行的选择操作由控制信号clk_sel控制。如果控制信号clk_sel具有第一状态,则多路复用器电路132选择用于输出的时钟信号phiclk作为选择的时钟selclk。如果控制信号clk_sel具有第二状态,则多路复用器电路132选择来自多路复用器140的分频时钟divclk作为选择的时钟selclk输出。

22.控制信号clk_sel也由控制电路106产生。在实施方式中,控制电路106可包括数据寄存器的另一位,该另一位根据时钟信号phiclk(要被n分频)还是分频时钟divclk(要被n分频)要被用于产生传送时钟txclk,而被设置为第一状态或第二状态。

23.每个分频器电路134被配置为将时钟信号phiclk的频率除以整数值(在提供了三个分频器电路134的实施方式中这里指示为a、b和c的那些整数值)。在实施方式中a=50,b=5且c=1;但是应当理解,这只是示例,对于给定的应用,可以根据需要选择a、b和c的值。

在示例实施方式中,a=50,b=5和c=1的值是结合支持发送器(第一)设备110和接收器(第二)设备112之间的以太网rgmii接口的实现来选择的,该接口可以以三种不同的速度运行:10mbps,100mbps和1000mbps。在该实现中,时钟信号phiclk由pll 130以500mhz的频率fphi产生。为了说明,在有四条数据线116d和一条时钟线116c的实现中,除以四给出125mhz,并且在时钟的上升沿和下降沿对四条数据线进行采样时,总数据速度为1000mbps。此外,还可以再除以5得到25mhz的时钟频率,并且仅在时钟的上升沿对4条数据线进行采样,则总数据速度为100mbps。

24.因此,对于用整数分频器值a=50实现的分频器电路134,提供了对以10mbps的以太网rgmii接口操作的支持(通过以10mhz的频率生成分频时钟divclk)。约翰逊计数器的输出处的时钟频率将为2.5mhz,在四条传送线的情况下,总的数据速度为10mbps。在用整数分频器值b=5实现的分频器电路134的情况下,提供了对100mbps的以太网rgmii接口操作的支持(通过以100mhz的频率生成分频时钟divclk)。约翰逊计数器输出处的时钟频率将为25mhz,在四条传送线的情况下,总的数据速度将为100mbps。同样地,对于利用整数分频器值c=1实现的分频器电路134,提供了对100mbps的以太网rgmii接口操作的支持(通过以500mhz的频率生成分频时钟divclk)。约翰逊计数器输出处的时钟频率将为125mhz,使用四条传送线(并且在上升沿和下降沿都进行采样),总数据速度为1000mbps。

25.现在参考图5,图5示出了约翰逊计数器电路142的电路图。约翰逊计数器电路142是包括触发器150和152以及逻辑反相器154(非门)的两位扭环计数器。触发器150和152的时钟输入均接收选择的时钟selclk。触发器150的数据输出q被应用到触发器152的数据输入d。触发器152的数据输出q由逻辑反相器154反相并应用到触发器150的数据输入d。触发器150的数据输出q提供源时钟srcclk,触发器152的数据输出q提供相移时钟phsclk(在这种情况下,如上所述,具有相对于源时钟srcclk的90度相移)。可选地,将触发器152的反相数据输出/q应用到触发器150的数据输入d(参考158)。约翰逊计数器电路142的两位实现实际上是四分频电路,因此源时钟srcclk和相移时钟phsclk的频率将是选择的时钟selclk的频率的四分之一。对于时钟信号phiclk使用n=4设置的频率fphi支持仅使用相同边沿时钟触发器的90度相移操作。将触发器150和152在选择的时钟selclk的同一边沿上定时有利地为时钟再收敛悲观度消除(clock re

‑

convergence pessimism removal,crpr)提供一些余量。

26.支持发送器(第一)设备110在多种模式下的操作。首先,考虑以太网rgmii接口操作的情况。在该操作场景中,控制电路106设置控制信号clk_sel的状态以使多路复用器132选择分频时钟divclk以应用于约翰逊计数器142(因为分频器电路134提供的整数分频是具体地选择的以支持以太网rgmii接口速度)。发送器(第一)设备110将与接收器(第二)设备112协商,以确定以三种不同速度之一的数据传输速率:10mbps、100mbps和500mbps。该协商例如可以由控制电路106执行,或者可以由发送器(第一)设备110的另一电路执行,并传送到控制电路106,用于设置控制信号speed_sel的状态。如果协商速率为10mbps,则控制信号speed_sel被设置为第一状态,并且由分频器电路134输出的具有整数分频器值a=50的时钟信号被多路复用器140选择为分频时钟divclk,并通过多路复用器132以提供选择的时钟selclk。如果协商速率为100mbps,则控制信号speed_sel被设置为第二状态,并且由分频器电路134输出的具有整数分频器值b=5的时钟信号被多路复用器140选择为分频时钟

divclk,并通过多路复用器132以提供所选择的时钟selclk。如果协商速率为1000mbps,则控制信号speed_sel被设置为第一状态,并且由分频器电路134输出的具有整数分频器值c=1的时钟信号被多路复用器140选择为分频时钟divclk,并通过多路复用器132以提供选择的时钟selclk。

27.其次,考虑另一接口操作(例如,非以太网rgmii或以非标准以太网速度进行接口)的情况,该接口操作具有传送时钟txclk的所需频率ftx。控制pll电路130以将时钟phiclk的频率fphi设置为频率ftx的四倍。该控制操作例如可以由控制电路106实现,或者可以由发送器(第一)设备110的另一电路执行。在该操作场景中,控制信号clk_sel的状态被设置为使得多路复用器132选择时钟phiclk以应用于约翰逊计数器142。

28.虽然在附图和前面的描述中已经详细地说明和描述了本发明,但是这种说明和描述被认为是说明性的或示例性的,而不是限制性的;本发明不限于所公开的实施例。通过对附图、公开内容和所附权利要求书的研究,本领域技术人员在实践所要求的发明时可以理解和实现对所公开实施例的其它变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。