技术特征:

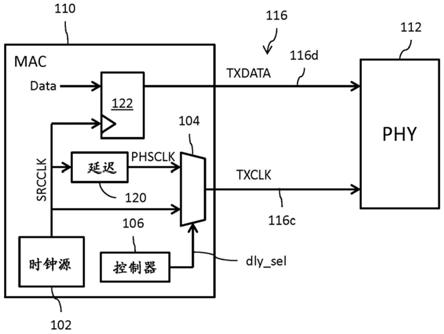

1.一种利用源同步型接口的系统,包括:发送器电路;以及接收器电路;其中所述发送器电路使用包括数据线和时钟线的源同步型接口被耦合到所述接收器电路;其中所述发送器电路包括:第一触发器,具有:数据输入,被配置为接收串行数据;时钟输入,被配置为接收源时钟;以及数据输出,被耦合到所述数据线;第一多路复用器,具有:第一输入,被配置为接收所述源时钟;第二输入,被配置为接收相移时钟;以及第一时钟输出,被耦合到所述时钟线,其中所述相移时钟被从所述源时钟偏移90度;以及控制电路,被配置为:如果所述系统被配置为用于在所述接收器电路中的目的地处对时钟进行延迟,则控制由所述第一多路复用器选择所述源时钟作为通过所述时钟线发送的传送时钟,并且如果所述系统被配置为用于在所述发送器电路中的源处对时钟进行延迟,则控制由所述第一多路复用器选择所述相移时钟作为通过所述时钟线发送的所述传送时钟。2.根据权利要求1所述的系统,其中所述接收器电路包括第二触发器,所述第二触发器具有:数据输入,被耦合以接收通过所述数据线发送的传送数据;以及时钟输入,被耦合以接收通过所述时钟线发送的所述传送时钟。3.根据权利要求1所述的系统,还包括约翰逊计数器,所述约翰逊计数器具有:输入,被配置为接收选择的时钟;第一输出,从所述选择的时钟产生所述源时钟;以及第二输出,从所述选择的时钟产生所述相移时钟。4.根据权利要求3所述的系统,其中所述约翰逊计数器是两位计数器。5.根据权利要求3所述的系统,其中所述约翰逊计数器实现由整数n对所述选择的时钟分频,以产生所述源时钟和所述相移时钟。6.根据权利要求5所述的系统,其中所述源时钟具有所述传送时钟的所需频率的n倍的频率,以通过所述源同步型接口在所述发送器电路和所述接收器电路之间实现期望的数据传输速率。7.根据权利要求3所述的系统,还包括:第二多路复用器,具有:第一输入,被配置为接收第一时钟;第二输入,被配置为接收第二时钟;以及第二时钟输出,产生所述选择的时钟,并且被耦合到所述约翰逊计数器的所述输入,其中所述第一时钟和所述第二时钟处于不同的频率。8.根据权利要求7所述的系统,其中所述控制电路还被配置为控制由所述第二多路复用器结合所述源同步型接口的第一操作模式为所述选择的时钟选择所述第一时钟,以及控制由所述第二多路复用器结合所述源同步型接口的第二操作模式为所述选择的时钟选择所述第二时钟。9.根据权利要求8所述的系统,其中所述源同步型接口的所述第一操作模式是与以太网rgmii接口操作相关联的标准速度,并且所述源同步型接口的所述第二操作模式是与以太网操作相关联的非标准速度。

10.根据权利要求9所述的系统,还包括第三多路复用器,所述第三多路复用器具有:第一输入,被配置为接收第三时钟;第二输入,被配置为接收第四时钟;以及第三时钟输出,产生所述第一时钟,并且被耦合到所述第二多路复用器的所述第一输入,其中所述第三时钟和所述第四时钟处于不同的频率,并且其中所述第三时钟和所述第四时钟的频率与用于所述以太网rgmii接口操作的不同标准速度相关联。11.根据权利要求10所述的系统,其中所述控制电路还被配置为控制由所述第三多路复用器结合用于所述以太网rgmii接口操作的第一标准速度选择所述第三时钟,以及控制由所述第三多路复用器结合用于所述以太网rgmii接口操作的第二、不同的标准速度选择所述第四时钟。12.根据权利要求10所述的系统,还包括:第一分频器,具有:输入,被配置为接收所述第二时钟;以及输出,产生所述第三时钟,并且被耦合到所述第三多路复用器的第一输入;以及第二分频器,具有:输入,被配置为接收所述第二时钟;以及输出,产生所述第四时钟,并且被耦合到所述第三多路复用器的第二输入。13.根据权利要求12所述的系统,还包括:锁相环,被配置为产生所述第二时钟。14.根据权利要求1所述的系统,还包括时钟分频和相移电路,所述时钟分频和相移电路具有:输入,被配置为接收选择的时钟;第一输出,产生从所述选择的时钟分频的所述源时钟;以及第二输出,产生从所述选择的时钟分频的所述相移时钟。15.根据权利要求14所述的系统,其中所述时钟分频和相移电路实现由整数n对所述选择的时钟分频,以产生所述源时钟和所述相移时钟。16.根据权利要求15所述的系统,其中所述源时钟具有所述传送时钟的所需频率的n倍的频率,以通过所述源同步型接口在所述发送器电路和所述接收器电路之间实现所需数据传输速率。17.根据权利要求14所述的系统,还包括:第二多路复用器,具有:第一输入,被配置为接收第一时钟;第二输入,被配置为接收第二时钟;以及第二时钟输出,产生所述选择的时钟,并且被耦合到所述时钟分频和相移电路的所述输入,其中所述第一时钟和所述第二时钟处于不同的频率。18.根据权利要求17所述的系统,其中所述控制电路还被配置为控制由所述第二多路复用器结合所述源同步型接口的第一操作模式为所述选择的时钟选择所述第一时钟,以及控制由所述第二多路复用器结合所述源同步型接口的第二操作模式为所述选择的时钟选择所述第二时钟。19.根据权利要求18所述的系统,其中所述源同步型接口的所述第一操作模式是与以太网rgmii接口操作相关联的标准速度,并且所述源同步型接口的所述第二操作模式是与以太网操作相关联的非标准速度。20.根据权利要求19所述的系统,还包括第三多路复用器,所述第三多路复用器具有:第一输入,被配置为接收第三时钟;第二输入,被配置为接收第四时钟;以及第三时钟输出,产生所述第一时钟并且被耦合到所述第二多路复用器的所述第一输入,其中所述第三时钟和所述第四时钟处于不同的频率,并且其中所述第三时钟和所述第四时钟的频率与用于所述以太网rgmii接口操作的不同标准速度相关联。

21.根据权利要求20所述的系统,其中所述控制电路还被配置为控制由所述第三多路复用器结合用于所述以太网rgmii接口操作的第一标准速度选择所述第三时钟,以及控制由所述第三多路复用器结合用于所述以太网rgmii接口操作的第二、不同的标准速度选择所述第四时钟。22.根据权利要求20所述的系统,还包括:第一分频器,具有:输入,被配置为接收所述第二时钟;以及输出,产生所述第三时钟,并且被耦合到所述第三多路复用器的第一输入;以及第二分频器,具有:输入,被配置为接收所述第二时钟;以及输出,产生所述第四时钟,并且被耦合到所述第三多路复用器的第二输入。23.根据权利要求22所述的系统,还包括:锁相环,被配置为产生所述第二时钟。24.一种用于源同步型接口的发送器电路,包括:第一触发器,具有:数据输入,被配置为接收串行数据;时钟输入,被配置为接收源时钟;以及数据输出,被耦合到数据线;第一多路复用器,具有:第一输入,被配置为接收所述源时钟;第二输入,被配置为接收相移时钟;以及时钟输出,被耦合到时钟线,其中所述相移时钟从所述源时钟偏移90度;以及控制电路,被配置为控制由所述第一多路复用器选择所述源时钟作为在所述时钟线上发送的传送时钟,用于在目的地配置处对时钟进行延迟,并且控制由所述第一多路复用器选择所述相移时钟作为在所述时钟线上发送的所述传送时钟,用于在所述源配置处对时钟进行延迟。25.根据权利要求24所述的发送器电路,还包括时钟分频和相移电路,所述时钟分频和相移电路具有:输入,被配置为接收选择的时钟;第一输出,产生从所述选择的时钟分频的所述源时钟;以及第二输出,产生从所述选择的时钟分频的所述相移时钟。26.根据权利要求25所述的发送器电路,其中所述时钟分频和相移电路实现由整数n对所述选择的时钟分频,以产生所述源时钟和所述相移时钟。27.根据权利要求26所述的发送器电路,其中所述源时钟具有所述传送时钟的所需频率的n倍的频率,以通过所述源同步型接口从所述发送器电路实现期望的数据传输速率。28.根据权利要求25所述的发送器电路,还包括:第二多路复用器,具有:第一输入,被配置为接收第一时钟;第二输入,被配置为接收第二时钟;以及第二时钟输出,产生所述选择的时钟,并且被耦合到所述时钟分频和相移电路的所述输入,其中所述第一时钟和所述第二时钟处于不同的频率。29.根据权利要求28所述的发送器电路,其中所述控制电路还被配置为控制由所述第二多路复用器结合所述源同步型接口的第一操作模式为所述选择的时钟选择所述第一时钟,以及控制由所述第二多路复用器结合所述源同步型接口的第二操作模式为所述选择的时钟选择所述第二时钟。30.根据权利要求29所述的发送器电路,其中所述源同步型接口的所述第一操作模式是与以太网rgmii接口操作相关联的标准速度,并且所述源同步型接口的所述第二操作模式是与以太网操作相关联的非标准速度。31.根据权利要求30所述的发送器电路,还包括第三多路复用器,所述第三多路复用器

具有:第一输入,被配置为接收第三时钟;第二输入,被配置为接收第四时钟;以及第三时钟输出,产生所述第一时钟并且被耦合到所述第二多路复用器的所述第一输入,其中所述第三时钟和所述第四时钟处于不同的频率,并且其中所述第三时钟和所述第四时钟的频率与用于所述以太网rgmii接口操作的不同标准速度相关联。32.根据权利要求31所述的发送器电路,其中所述控制电路还被配置为控制由所述第三多路复用器结合用于所述以太网rgmii接口操作的第一标准速度选择所述第三时钟,以及控制由所述第三多路复用器结合用于所述以太网rgmii接口操作的第二、不同的标准速度选择所述第四时钟。33.根据权利要求31所述的发送器电路,还包括:第一分频器,具有:输入,被配置为接收所述第二时钟;以及输出,产生所述第三时钟并且被耦合到所述第三多路复用器的第一输入;以及第二分频器,具有:输入,被配置为接收所述第二时钟;以及输出,产生所述第四时钟并且被耦合到所述第三多路复用器的第二输入。34.根据权利要求33所述的发送器电路,还包括:锁相环,被配置为产生所述第二时钟。

技术总结

本公开实施例公开了具有可选择的源端延迟和目的地端延迟控制的源同步接口。一种用于源同步型接口的发送器电路包括触发器,该触发器具有被配置为接收串行数据的数据输入、被配置为接收源时钟的时钟输入和耦合到数据线的数据输出。第一多路复用器具有被配置为接收源时钟的第一输入、被配置为接收相移时钟(从源时钟偏移90度)的第二输入以及耦合到时钟线的时钟输出。控制电路操作以控制由第一多路复用器选择源时钟作为在时钟线上发送的传送时钟,以用于在目的地实现时的时钟上的延迟。可选地,如果系统在源实现时被配置为时钟上的延迟,则控制电路使第一多路复用器选择相移时钟作为通过时钟线发送的传送时钟。作为通过时钟线发送的传送时钟。作为通过时钟线发送的传送时钟。

技术研发人员:B

受保护的技术使用者:意法半导体国际有限公司

技术研发日:2021.06.02

技术公布日:2021/12/7

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。