1.本发明涉及半导体装置。

背景技术:

2.在半导体装置包含有各种电路区域,作为电路区域的一个例子有标准单元区域。在标准单元区域包含有各种逻辑电路以及电源开关电路。

3.电源开关电路例如设置在供给的vdd的电位的电源线与向逻辑电路的晶体管供给vvdd的电源的电源线之间,切换对该晶体管的vvdd的电源电位的供给的开/关。通过使用电源开关电路,能够在不需要使逻辑电路动作时断开电源供给,抑制在构成逻辑电路的晶体管产生的漏电电流,实现消耗电力的降低。

4.近年来,已知被称为互补型场效应晶体管(complementary field effect transistor:cfet)的元件。在cfet中,在基板上层叠n沟道fet和p沟道fet。cfet适合于半导体装置的微细化。

5.专利文献1:日本特开2016-1652号公报

6.专利文献2:美国专利申请公开第2017/0331472号说明书

7.专利文献3:国际公开第2017/208888号

8.专利文献4:美国专利第9570395号说明书

9.专利文献5:美国专利第9837414号说明书

10.专利文献6:美国专利申请公开第2017/0040321号说明书

11.专利文献7:美国专利第9129829号说明书

12.专利文献8:日本特开2018-26565号公报

13.非专利文献1:2018symposium on vlsi technology digest of technical papers,p141

‑

p142

14.非专利文献2:2018symposium on vlsi technology digest of technical papers,p147

‑

148

15.至今,未对包含电源开关电路的半导体装置使用cfet的情况下的具体的构成进行详细的研究。

技术实现要素:

16.本发明的目的在于提供能够实现包含cfet的电源开关电路的半导体装置。

17.公开的技术的半导体装置具有:第一电源线;第二电源线;第一接地线;开关电路,设置于上述第一电源线与上述第二电源线之间;以及开关控制电路,设置于上述第一接地线与上述第一电源线之间。上述开关电路具有:第一导电型的第一晶体管;以及上述第一导电型的第二晶体管,形成在上述第一晶体管上。上述第一晶体管的第一栅电极与上述第二晶体管的第二栅电极连接。上述开关控制电路具有:第二导电型的第三晶体管;以及与上述第二导电型不同的第三导电型的第四晶体管,形成在上述第三晶体管上。上述第三晶体管

的第三栅电极与上述第四晶体管的第四栅电极连接。半导体装置具有将上述第三晶体管的输出以及上述第四晶体管的输出与上述第一栅电极以及上述第二栅电极电连接的信号线。

18.根据公开的技术,能够实现包含cfet的电源开关电路。

附图说明

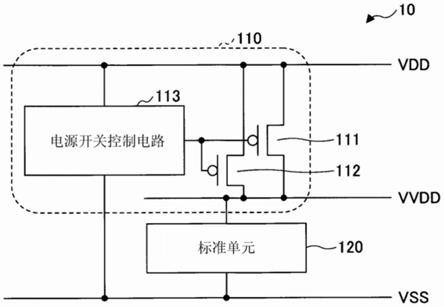

19.图1是表示第一实施方式的半导体装置的布局的图。

20.图2是表示第一实施方式的半导体装置所包含的电源开关电路的构成的电路图。

21.图3是表示第一实施方式的半导体装置所包含的缓冲器的构成的电路图。

22.图4是表示第一实施方式中的标准单元区域的平面构成的示意图(其一)。

23.图5是表示第一实施方式中的标准单元区域的平面构成的示意图(其二)。

24.图6是表示第一实施方式中的标准单元区域的剖视图(其一)。

25.图7是表示第一实施方式中的标准单元区域的剖视图(其二)。

26.图8是表示第一实施方式中的标准单元区域的剖视图(其三)。

27.图9是表示第一实施方式中的标准单元区域的剖视图(其四)。

28.图10是表示第一实施方式中的标准单元区域的剖视图(其五)。

29.图11是表示第一实施方式中的标准单元区域的剖视图(其六)。

30.图12是表示第一实施方式中的标准单元区域的剖视图(其七)。

31.图13是表示第一实施方式的第一变形例中的标准单元区域的剖视图(其一)。

32.图14是表示第一实施方式的第一变形例中的标准单元区域的剖视图(其二)。

33.图15是表示第一实施方式的第一变形例中的标准单元区域的剖视图(其三)。

34.图16是表示第一实施方式的第二变形例中的标准单元区域的平面构成的示意图。

35.图17是表示第一实施方式的第二变形例中的标准单元区域的剖视图。

36.图18是表示第一实施方式的第三变形例中的开关晶体管的平面构成的示意图(其一)。

37.图19是表示第一实施方式的第三变形例中的开关晶体管的平面构成的示意图(其二)。

38.图20是表示第一实施方式的第四变形例中的开关晶体管的平面构成的示意图(其一)。

39.图21是表示第一实施方式的第四变形例中的开关晶体管的平面构成的示意图(其二)。

40.图22是表示第一实施方式的第五变形例中的标准单元区域的平面构成的示意图(其一)。

41.图23是表示第一实施方式的第五变形例中的标准单元区域的平面构成的示意图(其二)。

42.图24是表示第二实施方式中的标准单元区域的平面构成的示意图(其一)。

43.图25是表示第二实施方式中的标准单元区域的平面构成的示意图(其二)。

44.图26是表示第二实施方式中的标准单元区域的剖视图(其一)。

45.图27是表示第二实施方式中的标准单元区域的剖视图(其二)。

46.图28是表示第三实施方式中的标准单元区域的平面构成的示意图(其一)。

47.图29是表示第三实施方式中的标准单元区域的平面构成的示意图(其二)。

48.图30是表示第三实施方式的第一变形例中的标准单元区域的平面构成的示意图(其一)。

49.图31是表示第三实施方式的第一变形例中的标准单元区域的平面构成的示意图(其二)。

50.图32是表示第三实施方式的第二变形例中的标准单元区域的平面构成的示意图(其一)。

51.图33是表示第三实施方式的第二变形例中的标准单元区域的平面构成的示意图(其二)。

52.图34是表示第四实施方式中的电源开关电路的构成的电路图。

53.图35是表示第四实施方式的半导体装置所包含的缓冲器的构成的电路图。

54.图36是表示第四实施方式中的标准单元区域的平面构成的示意图(其一)。

55.图37是表示第四实施方式中的标准单元区域的平面构成的示意图(其二)。

56.图38是表示第四实施方式中的标准单元区域的剖视图。

57.图39是表示第五实施方式中的标准单元区域的平面构成的示意图(其一)。

58.图40是表示第五实施方式中的标准单元区域的平面构成的示意图(其二)。

59.图41是表示第五实施方式中的标准单元区域的剖视图。

60.图42是表示第五实施方式的第一变形例中的标准单元区域的平面构成的示意图(其一)。

61.图43是表示第五实施方式的第一变形例中的标准单元区域的平面构成的示意图(其二)。

62.图44是表示第五实施方式的第二变形例中的标准单元区域的平面构成的示意图(其一)。

63.图45是表示第五实施方式的第二变形例中的标准单元区域的平面构成的示意图(其二)。

具体实施方式

64.以下,参照附图对实施方式进行具体的说明。此外,在本说明书以及附图中,对于实际具有相同的功能构成的构成要素,有时通过附加相同的附图标记来省去重复的说明。另外,在以下的说明中,将与基板的表面平行且相互正交的两个方向设为x方向、y方向,并将与基板的表面垂直的方向设为z方向。另外,本公开中的配置的一致严格来说并不排除由于制造上的偏差而不一致的情况,即使在由于制造上的偏差而配置产生偏移的情况下,也能够视为配置一致。

65.(第一实施方式)

66.首先,对第一实施方式进行说明。图1是表示第一实施方式的半导体装置的布局的图。图2是表示第一实施方式的半导体装置所包含的电源开关电路的构成的电路图。

67.如图1所示,第一实施方式的半导体装置1包含多个标准单元区域10以及配置在其周边的输入输出(i/o)单元区域20。此外,标准单元区域10的配置数目也可以是一个,也可以在三个以上。如图2所示,标准单元区域10包含标准单元120以及电源开关电路110。标准

单元120例如包含nand电路、反相器电路等各种逻辑电路。在标准单元区域10配置有对标准单元120供给接地电位的vss布线以及供给电源电位的vvdd布线。在标准单元区域10还配置有从外部对电源开关电路110供给电源电位的vdd布线。vss布线也被称为接地线,vvdd布线以及vdd布线也分别被称为电源线。

68.如图2所示,电源开关电路110包含开关晶体管111以及112、和电源开关控制电路113。开关晶体管111以及112例如是p沟道mos晶体管,连接在vdd布线与vvdd布线之间。开关晶体管111的栅极与开关晶体管112的栅极连接。电源开关控制电路113与开关晶体管111的栅极以及开关晶体管112的栅极连接,并控制开关晶体管111以及112的动作。通过电源开关控制电路113切换开关晶体管111以及112的开/关,控制vdd布线与vvdd布线之间的导通。电源开关控制电路113例如包含缓冲器。

69.接下来,对电源开关控制电路113所使用的缓冲器的构成进行说明。图3是表示缓冲器的构成的电路图。

70.如图3所示,电源开关控制电路113所使用的缓冲器1300具有反相器1310以及1320。在反相器1310输入有输入信号in,反相器1310的输出输入到开关晶体管111的栅极、开关晶体管112的栅极、以及反相器1320,从反相器1320输出输出信号out。反相器1310包含一对p沟道mos晶体管1311p以及n沟道mos晶体管1311n。反相器1320包含一对p沟道mos晶体管1321p以及n沟道mos晶体管1321n。此外,反相器1310以及1320的构成是一个例子,例如,也可以是包含于反相器1310以及1320的p沟道mos晶体管以及n沟道mos晶体管的对在两个以上。另外,也可以在开关晶体管111的栅极以及开关晶体管112的栅极输入有向反相器1310的输入信号in、来自反相器1320的输出信号out。

71.开关晶体管112形成在开关晶体管111上。在反相器1310中,p沟道mos晶体管1311p形成在n沟道mos晶体管1311n上。在反相器1320中,p沟道mos晶体管1321p形成在n沟道mos晶体管1321n上。

72.图4以及图5是表示第一实施方式中的标准单元区域10的平面构成的示意图。图4主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图5主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管112的布局。除了图4以及图5双方所示的结构物之外,图5所示的结构物位于图4所示的结构物的上方。图6~图12是表示第一实施方式中的标准单元区域10的剖视图。图6相当于沿着图4以及图5中的x11-x21线的剖视图。图7相当于沿着图4以及图5中的y11-y21线的剖视图。图8相当于沿着图4以及图5中的y12-y22线的剖视图。图9相当于沿着图4以及图5中的y13-y23线的剖视图。图10相当于沿着图4以及图5中的y14-y24线的剖视图。图11相当于沿着图4以及图5中的y15-y25线的剖视图。图12相当于沿着图4以及图5中的y16-y26线的剖视图。

73.如图6~图12所示,在基板101的表面形成元件分离膜102。例如通过sti(shallow trench isolation:浅沟槽隔离)法形成元件分离膜102。在基板101以及元件分离膜102形成向x方向延伸的多个槽,在这些槽内经由绝缘膜104形成电源线910以及920。例如,通过绝缘膜103覆盖电源线910以及920的表面。例如,元件分离膜102的表面以及绝缘膜103的表面既可以与基板101的表面成为同一平面,也可以不为同一平面。有时这样的结构的电源线910以及920被称为bpr(buried power rail:埋入式电源轨)。例如,电源线910相当于vvdd布线,电源线920相当于vss布线。

74.如图6等所示,在电源线910与电源线920之间在从元件分离膜102露出的基板101上形成向x方向延伸,并向z方向立起的鳍片181以及182。遍及n沟道mos晶体管1311n以及n沟道mos晶体管1321n形成鳍片181,鳍片182形成于开关晶体管111。

75.鳍片181包含n型区域181na、n型区域181nc、以及n型区域181na与n型区域181nc之间的n型区域181nb。n型区域181na成为n沟道mos晶体管1311n的漏极。n型区域181nc成为n沟道mos晶体管1321n的漏极。n型区域181nb成为n沟道mos晶体管1311n的源极以及n沟道mos晶体管1321n的源极。鳍片181的n型区域181na与n型区域181nb之间的部分成为n沟道mos晶体管1311n的沟道181c。鳍片181的n型区域181nb与n型区域181nc之间的部分成为n沟道mos晶体管1321n的沟道181c。

76.鳍片182包含交替地配置的p型区域182pa、和p型区域182pb。p型区域182pa成为开关晶体管111的漏极。p型区域182pb成为开关晶体管111的源极。鳍片182的p型区域182pa与p型区域182pb之间的部分成为开关晶体管111的沟道182c。此外,虽然分别仅配置一个鳍片181以及182,但例如也可以分别在y方向配置多个。这在其它的实施方式、变形例中也可以相同地变更个数。

77.如图4等所示,经由绝缘膜105在元件分离膜102上形成从n型区域181na向y方向延伸的局部布线191ba、从n型区域181nb向y方向延伸的局部布线191bb、以及从n型区域181nc向y方向延伸的局部布线191bc。局部布线191ba以及191bb延伸到电源线920的上方。局部布线191bc延伸到电源线910的上方。

78.如图8所示,在局部布线191bb与电源线920之间,在绝缘膜103形成有接触孔511b。局部布线191bb通过接触孔511b内的导电体与电源线920连接。局部布线191bb将电源线920与n型区域181nb电连接。

79.如图4等所示,经由绝缘膜105在元件分离膜102上形成从p型区域182pa向y方向延伸的局部布线192ba、和从p型区域182pb向y方向延伸的局部布线192bb。局部布线192ba延伸到电源线910的上方。局部布线192bb延伸到电源线920的上方。

80.如图10所示,在局部布线192ba与电源线910之间,在绝缘膜103形成有接触孔512a。局部布线192ba通过接触孔512a内的导电体与电源线910连接。局部布线192ba将电源线910与p型区域182pa电连接。

81.在局部布线191ba、191bb、191bc、192ba以及192bb上形成绝缘膜106。

82.如图5等所示,经由绝缘膜106,在局部布线191ba上形成局部布线291ta,在局部布线191bb上形成局部布线291tb,在局部布线191bc上形成局部布线291tc。

83.如图7所示,在电源线920的上方,在局部布线291ta与局部布线191ba之间在绝缘膜106形成有接触孔521a。局部布线291ta与局部布线191ba通过接触孔521a内的导电体相互电连接。

84.如图9所示,在电源线910的上方,在局部布线291tc与局部布线191bc之间在绝缘膜106形成有接触孔521c。局部布线291tc与局部布线191bc通过接触孔521c内的导电体相互电连接。

85.如图8所示,局部布线291tb与局部布线191bb通过绝缘膜106相互电绝缘分离。

86.如图5等所示,经由绝缘膜106,在局部布线192ba上形成局部布线292ta,在局部布线192bb上形成局部布线292tb。如图10所示,在电源线910的上方,在局部布线292ta与局部

布线192ba之间在绝缘膜106形成有接触孔522a。局部布线292ta与局部布线192ba通过接触孔522a内的导电体相互电连接。

87.如图11所示,在p型区域182pb的上方,在局部布线292tb与局部布线192bb之间在绝缘膜106形成有接触孔522b。局部布线292tb与局部布线192bb通过接触孔522b内的导电体相互电连接。

88.如图5以及图6所示,在鳍片181的上方,设置向x方向延伸,且配置为在俯视时与局部布线291ta、291tb以及291tc重叠的半导体区域281。在鳍片182的上方设置向x方向延伸,且配置为在俯视时与局部布线292ta以及局部布线292tb重叠的半导体区域282。此外,虽然分别仅配置一个半导体区域281以及282,但例如也可以分别在y方向配置多个。这在其它的实施方式、变形例中也可以相同地变更个数。

89.如图6等所示,半导体区域281包含p型区域281pa、p型区域281pc、以及p型区域281pa与p型区域281pc之间的p型区域281pb。p型区域281pa成为p沟道mos晶体管1311p的漏极。p型区域281pc成为p沟道mos晶体管1321p的漏极。p型区域281pb成为p沟道mos晶体管1311p的源极以及p沟道mos晶体管1321p的源极。半导体区域281的p型区域281pa与p型区域281pb之间的部分成为p沟道mos晶体管1311p的沟道281c。半导体区域281的p型区域281pb与p型区域281pc之间的部分成为p沟道mos晶体管1321p的沟道281c。

90.半导体区域282包含交替地配置的p型区域282pa、和p型区域282pb。p型区域282pa成为开关晶体管112的漏极。p型区域282pb成为开关晶体管112的源极。半导体区域282的p型区域282pa与p型区域282pb之间的部分成为开关晶体管112的沟道282c。

91.如图4~图6等所示,在局部布线191ba以及局部布线291ta的层叠体与局部布线191bb以及局部布线291tb的层叠体之间,形成有n沟道mos晶体管1311n以及p沟道mos晶体管1311p所共用的栅电极131。在局部布线191bc以及局部布线291tc的层叠体与局部布线191bb以及局部布线291tb的层叠体之间,形成有n沟道mos晶体管1321n以及p沟道mos晶体管1321p所共用的栅电极132。在局部布线192ba以及局部布线292ta的层叠体与局部布线192bb以及局部布线292tb的层叠体之间,形成有开关晶体管111以及开关晶体管112所共用的栅电极133。

92.在栅电极133与鳍片182之间、以及栅电极133与半导体区域282之间,形成有栅极绝缘膜135。在栅电极131与鳍片181之间、栅电极131与鳍片182之间、栅电极132与鳍片181之间、以及栅电极132与鳍片182之间也形成有栅极绝缘膜135。

93.如图6等所示,在基板101以及元件分离膜102的上方形成有绝缘膜151。局部布线191ba、191bb、191bc、192ba、192bb、291ta、291tb、291tc、292ta以及292tb、和栅电极131~133被埋入绝缘膜151。另外,如图8所示,在俯视时,局部布线291tb不到达局部布线191bb的电源线920侧的端部,在局部布线291tb的电源线920侧的端部与局部布线191bb的电源线920侧的端部之间,在绝缘膜106上形成有绝缘膜152。

94.在绝缘膜151以及152、局部布线291ta、291tb、291tc、292ta以及292tb、栅电极131~133之上形成有绝缘膜153,在绝缘膜153之上形成有绝缘膜154。

95.如图5以及图8所示,在绝缘膜153的n型区域181nb以及p型区域281pb的上方形成有到达局部布线291tb的接触孔531b。如图5以及图9所示,在绝缘膜153的电源线910的上方形成有到达局部布线291tc的接触孔531c。如图5所示,在绝缘膜153的电源线910的上方形

成有到达栅电极131的接触孔541a。如图5以及图11所示,在绝缘膜153的p型区域182pb以及p型区域282pb的上方形成有到达局部布线292tb的接触孔532b。如图5以及图12所示,在绝缘膜153的电源线920的上方形成有到达栅电极133的接触孔542。在绝缘膜153的电源线920的上方形成有到达局部布线291ta的接触孔531a。在绝缘膜153的电源线920的上方形成有到达栅电极132的接触孔541b。

96.如图5等所示,在电源线910的上方,在绝缘膜154内形成有通过接触孔541a内的导电体与栅电极131连接的信号线951、和通过接触孔531c内的导电体与局部布线291tc连接的信号线952。信号线951以及952向x方向延伸。在信号线951输入向反相器1310的输入信号in,从信号线952输出来自反相器1320的输出信号out。

97.在电源线920的上方,在绝缘膜154内形成有控制信号线940。控制信号线940通过接触孔531a内的导电体与局部布线291ta连接。控制信号线940通过接触孔541b内的导电体与栅电极132连接。控制信号线940通过接触孔542内的导电体与栅电极133连接。控制信号线940向x方向延伸。通过控制信号线940,从电源开关控制电路113向开关晶体管111以及112传递控制信号。

98.在y方向上,在信号线951以及952与控制信号线940之间配置电源线930。电源线930形成在绝缘膜154内。电源线930通过接触孔531b内的导电体与局部布线291tb连接,并通过接触孔532b内的导电体与局部布线292tb连接。电源线930例如相当于vdd布线。

99.例如,电源线910以及920的材料使用钌(ru)、钴(co)或者钨(w)等。例如,电源线930、控制信号线940以及信号线951~952的材料使用铜(cu)、钌(ru)或者钴(co)等。在使用铜或者钴的情况下,优选形成导电性的基底膜(势垒金属膜)例如钽(ta)膜或者氮化钽(tan)膜,然而在使用钌的情况下,也可以不形成基底膜。

100.例如,局部布线的材料使用铜(cu)、钌(ru)、钴(co)或者钨(w)等。在使用铜、钴或者钨的情况下,优选形成导电性的基底膜(势垒金属膜)例如钛(ti)膜或者氮化钛(tin)膜,但在使用钌的情况下,也可以不形成基底膜。例如,接触孔内的导电膜(通孔)例如能够使用与局部布线的材料相同的材料,或者与电源线930、控制信号线940以及信号线951~952的材料相同的材料。

101.例如,基板101能够使用硅(si)等半导体。例如,能够通过对基板101进行图案化来形成鳍片181以及182。也可以在鳍片181以及182的与局部布线相接的部分设置镍(ni)或者钴(co)等高熔点金属的硅化物。例如,半导体区域281以及282的沟道能够使用硅(si)等半导体的纳米线。另外,半导体区域281以及282的p型区域以及n型区域能够使用从沟道的纳米线的端面外延生长的si、碳化硅(sic)、锗硅(sige)等半导体。

102.例如,栅电极131~133能够使用钛(ti)、氮化钛(tin)、多晶硅(poly si)等导电材料。例如,栅极绝缘膜能够使用氧化铪、氧化铝、铪以及铝的氧化物等高电介质材料。

103.例如,电源线930、控制信号线940以及信号线951~952与配置在它们的下部的接触孔一起,通过双镶嵌法形成。另外,也可以和配置在它们的下部的接触孔独立地利用单镶嵌法形成电源线930、控制信号线940以及信号线951~952。另外,例如也可以与电源开关电路110以及电源开关控制电路113的各晶体管相比在上方配置电源线910以及920。也可以将这些变形应用于其它的实施方式、变形例。

104.在第一实施方式中,反相器1310以及1320包含cfet。另外,开关晶体管111以及112

虽然均为p沟道mos晶体管,然而具有cfet那样的层叠结构。根据第一实施方式,能够使用cfet实现电源开关电路110。因此,适合于半导体装置的进一步的微细化。

105.(第一实施方式的第一变形例)

106.接下来,对第一实施方式的第一变形例进行说明。第一变形例在n沟道mos晶体管1311n以及1321n、开关晶体管111代替鳍片而使用纳米线这一点与第一实施方式不同。图13~图15是表示第一实施方式的第一变形例中的标准单元区域10的剖视图。图13相当于沿着图4以及图5中的x11-x21线的剖视图。图14相当于沿着图4以及图5中的y11-y21线的剖视图。图15相当于沿着图4以及图5中的y16-y26线的剖视图。

107.在第一变形例中,如图13~图15所示,在局部布线191ba、191bb、191bc、192ba以及192bb的下表面与基板101的上表面之间形成有绝缘膜105。在半导体区域281的下方,设置沿着x方向,且配置为在俯视时与局部布线191ba、191bb以及191bc重叠的半导体区域481。在半导体区域282的下方设置向x方向,且配置为在俯视时与局部布线192ba以及192bb重叠的半导体区域482。

108.半导体区域481包含n型区域481na、n型区域481nc、以及n型区域481na与n型区域481nc之间的n型区域481nb。n型区域481na成为n沟道mos晶体管1311n的漏极。n型区域481nc成为n沟道mos晶体管1321n的漏极。n型区域481nb成为n沟道mos晶体管1311n的源极以及n沟道mos晶体管1321n的源极。半导体区域481的n型区域481na与n型区域481nb之间的部分成为n沟道mos晶体管1311n的沟道481c。半导体区域481的n型区域481nb与n型区域481nc之间的部分成为n沟道mos晶体管1321n的沟道481c。

109.半导体区域482包含交替地配置的p型区域482pa、和p型区域482pb。p型区域482pa成为开关晶体管111的漏极。p型区域482pb成为开关晶体管111的源极。半导体区域482的p型区域482pa与p型区域482pb之间的部分成为开关晶体管111的沟道482c。

110.例如,半导体区域481以及482的沟道能够使用硅(si)等半导体的纳米线。另外,半导体区域481以及482的p型区域以及n型区域能够使用从沟道的纳米线的端面外延生长的si、碳化硅(sic)、锗硅(sige)等半导体。

111.其它的构成与第一实施方式相同。

112.通过第一变形例也能够得到与第一实施方式相同的效果。在其它的实施方式、变更例中,也能够代替鳍片181以及182而使用半导体区域481以及482。另外,也能够代替半导体区域481以及482而使用鳍片181以及182。

113.(第一实施方式的第二变形例)

114.接下来,对第一实施方式的第二变形例进行说明。第二变形例在接触孔522b的配置这一点与第一实施方式不同。图16是表示第一实施方式的第二变形例中的标准单元区域10的平面构成的示意图。图16主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图17是表示第一实施方式的第二变形例中的标准单元区域10的剖视图。图17相当于沿着图16中的y15-y25线的剖视图。

115.在第二变形例中,如图16~图17所示,接触孔522b位于电源线920的上方。其它的构成与第一实施方式相同。

116.通过第二变形例也能够得到与第一实施方式相同的效果。

117.另外,在第二变形例中,在俯视时接触孔522b从半导体区域282偏离,所以即使不

通过保护膜等保护半导体区域282也能够形成接触孔522b。因此,能够使制造工序简单化。

118.(第一实施方式的第三变形例)

119.接下来,对第一实施方式的第三变形例进行说明。第三变形例在开关晶体管111以及112的构成这一点与第一实施方式不同。图18以及图19是表示第一实施方式的第三变形例中的开关晶体管111以及112的平面构成的示意图。图18主要示出开关晶体管111的布局。图19主要示出开关晶体管112的布局。除了图18以及图19双方所示的结构物之外,图19所示的结构物位于图18所示的结构物的上方。

120.在第三变形例中,如图18所示,局部布线192bb与局部布线192ba相同,从p型区域182pa延伸至电源线910的上方。也在电源线910的上方形成有接触孔522b。如图19所示,也在电源线910的上方形成有接触孔532b。在电源线910的上方也形成有通过接触孔532b内的导电体与局部布线292tb连接的电源线930。例如,电源线910的上方的电源线930经由上层的布线层与鳍片182的上方的电源线930连接。换句话说,在第三变形例中,作为vdd布线的一部分的电源线930被分割为多个,并与开关晶体管112的源极连接。分割为多个的电源线930相互电连接。其它的构成与第一实施方式相同。

121.通过第三变形例也能够得到与第一实施方式相同的效果。另外,通过将电源线930分割为多个来配置,能够分散地进行vdd的电位的供给,能够抑制电流集中。另外,通过电源线930的分割,在电源线930整体降低电阻,所以能够抑制通过电源线930供给的电位的降低。在其它的实施方式、变更例中,也可以将电源线930分割为多个,并与开关晶体管112的源极连接。

122.(第一实施方式的第四变形例)

123.接下来,对第一实施方式的第四变形例进行说明。第四变形例在开关晶体管111以及112的构成这一点与第一实施方式不同。图20以及图21是表示第一实施方式的第四变形例中的开关晶体管111以及112的平面构成的示意图。图20主要示出开关晶体管111的布局。图21主要示出开关晶体管112的布局。除了图20以及图21双方所示的结构物之外,图21所示的结构物位于图20所示的结构物的上方。

124.在第四变形例中,如图20所示,局部布线192bb从电源线910的上方延伸至电源线920的上方。接触孔522b位于电源线910的上方以及电源线920的上方。如图21所示,接触孔532b位于电源线910的上方以及电源线920的上方,接触孔542位于半导体区域282的上方。在电源线910以及920的上方形成电源线930,在半导体区域282的上方形成控制信号线940。控制信号线940在半导体区域282的上方通过接触孔542内的导电体与栅电极133连接。其它的构成与第三变形例相同。

125.通过第四变形例也能够得到与第一实施方式相同的效果。并且,在俯视时接触孔532b与接触孔522b重叠,所以能够降低电源线930与局部布线192bb之间的电阻。

126.(第一实施方式的第五变形例)

127.接下来,对第一实施方式的第五变形例进行说明。第五变形例在电源开关电路110的轨道数目这一点与第一实施方式不同。图22以及图23是表示第一实施方式的第五变形例中的标准单元区域10的平面构成的示意图。图22主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图23主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。除了图22以及图23双方所示的结构物之外,图23所示的结构

物位于图22所示的结构物的上方。

128.在第五变形例中,如图22以及图23所示,电源开关电路110由四个轨道构成。

129.如图22所示,在y方向上,接触孔521a位于电源线920与鳍片181之间,接触孔521c位于电源线910与鳍片181之间。局部布线192bb与局部布线192ba相同,从p型区域182pa延伸至电源线910的上方。接触孔522b位于电源线910的上方。

130.如图23所示,接触孔531b以及532b位于电源线910的上方。电源线930在电源线910的上方,通过接触孔531b内的导电体与局部布线291tb连接,并通过接触孔532b内的导电体与局部布线292tb连接。接触孔541a以及信号线951位于电源线920的上方。接触孔531c以及信号线952位于接触孔521c的上方。将局部布线291td形成为在x方向在与局部布线291tb之间夹着局部布线291tc。局部布线291td从电源线920的上方朝向电源线910的上方延伸。在y方向上在与接触孔531a相同的位置,在局部布线291td上在绝缘膜153形成接触孔531d。在绝缘膜154内形成通过接触孔531a内的导电体与局部布线291ta连接,并通过接触孔531d内的导电体与局部布线291td连接的控制信号线941。

131.其它的构成与第一实施方式相同。

132.通过第五变形例也能够得到与第一实施方式相同的效果。另外,根据第五变形例,能够在y方向上,增大电源线930与控制信号线940之间的距离。因此,能够降低电源线930与控制信号线940之间的寄生电容。并且,在俯视时接触孔532b与接触孔522b重叠,所以能够降低电源线930与局部布线192bb之间的电阻。

133.此外,也可以在y方向上在电源线910与电源线920之间,配置两组以上鳍片181(或者半导体区域481)、鳍片182(或者半导体区域482)、半导体区域281以及半导体区域282。在其它的实施方式、变更例中也相同。

134.(第二实施方式)

135.接下来,对第二实施方式进行说明。第二实施方式在局部布线的配置这一点与第一实施方式不同。图24以及图25是表示第二实施方式中的标准单元区域10的平面构成的示意图。图24主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图25主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。除了图24以及图25双方所示的结构物之外,图25所示的结构物位于图24所示的结构物的上方。图26以及图27是表示第二实施方式中的标准单元区域10的剖视图。图26相当于沿着图24以及图25中的y17-y27线的剖视图。图27相当于沿着图24以及图25中的y18-y28线的剖视图。

136.在第二实施方式中,如图24所示,局部布线191ba从n型区域481na延伸至电源线910的上方,接触孔521a位于电源线910的上方。局部布线192ba从p型区域482pa延伸至电源线910的上方,局部布线192bb从p型区域482pb延伸至电源线920的上方。

137.如图25所示,局部布线291ta从p型区域281pa延伸至电源线910的上方。接触孔531a位于电源线910的上方。接触孔541a位于电源线920的上方。接触孔541b位于电源线910的上方。接触孔531c位于半导体区域281的上方。局部布线292ta从p型区域282pa延伸至电源线920的上方,局部布线292tb从p型区域282pb延伸至电源线910的上方。

138.如图26所示,在电源线920的上方,在绝缘膜153形成接触孔2532a,电源线930通过接触孔2532a内的导电体与局部布线292ta连接。

139.如图27所示,在电源线910的上方,在绝缘膜151以及103形成接触孔2512b,局部布

线292tb通过接触孔2512b内的导电体与电源线910连接。在电源线920的上方,在绝缘膜153以及152形成接触孔2532b,电源线930通过接触孔2532b内的导电体与局部布线192bb连接。

140.这样,在第二实施方式中,俯视时,开关晶体管111的源极(p型区域482pb)与开关晶体管112的漏极(p型区域282pb)重叠,开关晶体管111的漏极(p型区域482pa)与开关晶体管112的源极(p型区域282pa)重叠。

141.其它的构成与第一实施方式的第一变形例相同。

142.在第二实施方式中,电源线930不经由局部布线292tb,而通过接触孔2352b内的导电体与局部布线192bb连接。因此,能够提高供给至局部布线192bb的vdd的电源电位与供给至局部布线292ta的vdd的电源电位之间的均匀性。另外,在俯视时,开关晶体管111中的电流路径i1与开关晶体管112中的电流路径i2分散。因此,能够进一步抑制电流集中,能够抑制电源中断。

143.也可以将第一实施方式的第二~第五变形例应用于第二实施方式。

144.(第三实施方式)

145.接下来,对第三实施方式进行说明。第三实施方式在单元的高度这一点与第一实施方式不同。图28以及图29是表示第三实施方式中的标准单元区域10的平面构成的示意图。图28主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图29主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。

146.在第三实施方式中,如图28以及图29所示,电源开关电路110成为双高单元(double high cell)。换句话说,电源开关电路110形成于在y方向夹着电源线920配置的两个电源线910。

147.如图28所示,局部布线191ba从n型区域181na延伸至一方的电源线910的上方,局部布线191bc从n型区域181nc延伸至电源线920的上方。接触孔521a位于一方的电源线910的上方,接触孔521c位于电源线920的上方。

148.如图28以及图29所示,栅电极133、局部布线192ba、192bb、292ta以及292tb从一方的电源线910的上方延伸至另一方的电源线910的上方。在y方向上在一方的电源线910与另一方的电源线910之间以等间隔配置四个鳍片182以及半导体区域282。在局部布线192bb与局部布线292tb之间将接触孔522b形成为在俯视时与鳍片182以及半导体区域282重叠。此外,图28以及图29中的鳍片182以及半导体区域282的数目为一个例子,并不限定于此。

149.如图29所示,控制信号线940位于一方的电源线910的上方,电源线930位于电源线920的上方。另外,在鳍片182以及半导体区域282的上方也在绝缘膜154内形成电源线930。多个电源线930中最接近控制信号线940的电源线通过接触孔531b内的导电体与局部布线291tb连接。

150.通过第三实施方式也能够得到与第一实施方式相同的效果。在其它的实施方式、变更例中,也能够使电源开关电路110为双高单元。

151.此外,也可以省略形成鳍片182(或者半导体区域482)与半导体区域282之间的接触孔522b。该情况下,也可以仅在俯视时与电源线910重叠的位置配置接触孔522b。

152.(第三实施方式的第一变形例)

153.接下来,对第三实施方式的第一变形例进行说明。第一变形例在单元的高度这一点与第二实施方式不同。图30以及图31是表示第三实施方式的第一变形例中的标准单元区

域10的平面构成的示意图。图30主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图31主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。

154.在第一变形例中,如图30以及图31所示,电源开关电路110为双高单元。换句话说,电源开关电路110形成于在y方向上夹着电源线920配置的两个电源线910。局部布线192ba从p型区域182pa延伸至两个电源线910的上方。局部布线192bb配置在与各p型区域182pb重叠的位置,在俯视时与两个电源线910分离。局部布线292ta配置在与各p型区域282pa重叠的位置,在俯视时与两个电源线910分离。局部布线292tb从p型区域282pb延伸至两个电源线910的上方。在局部布线192ba的一部分的上方配置局部布线292ta的一部分。在局部布线192bb的一部分的上方配置局部布线292tb的一部分。局部布线192bb通过接触孔2532b内的导电体与电源线930连接。局部布线292ta通过接触孔2532a内的导电体与电源线930连接。局部布线192ba通过接触孔512a内的导电体分别与两个电源线910连接。局部布线292tb通过接触孔2512b内的导电体分别与两个电源线910连接。

155.换句话说,第一变形例具备组合了第三实施方式和第二实施方式的构成。但是,在第三实施方式中,在俯视时鳍片182以及半导体区域282位于电源线920的x方向的延长线上,与此相对在第一变形例中,它们位于各个单元的电源线910附近。而且,在俯视时接触孔2532b位于电源线920的延长线上。该情况下,接触孔2532b在俯视时位于鳍片182以及半导体区域282之间。

156.根据第一变形例,能够得到与第二实施方式相同的效果以及与第三实施方式相同的效果。

157.(第三实施方式的第二变形例)

158.接下来,对第三实施方式的第二变形例进行说明。第二变形例在开关晶体管111以及112的构成这一点与第一变形例不同。图32以及图33是表示第三实施方式的第二变形例中的标准单元区域10的平面构成的示意图。图32主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图33主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。

159.在第二变形例中,如图32以及图33所示,在两个电源线910间以等间隔配置四个鳍片182。对于四个鳍片182中的三个,在其上方配置半导体区域282。而且,接触孔2532b位于在俯视时配置鳍片182且未配置半导体区域282的部分。此外,鳍片182的配置数目是一个例子,并不限定于四个。另外,在上方不配置半导体区域282的鳍片182的数目并不限定于一个,也可以在两个以上。

160.通过第二变形例也能够得到与第二实施方式相同的效果以及与第三实施方式相同的效果。

161.此外,在第二变形例中,虽然在有多个的鳍片182的一部分的上方未配置半导体区域282,但只要未形成该半导体区域282的p型区域282pa以及282pb,则也可以形成虚拟的沟道282c。另外,在形成工序中,也可以使p型区域282pa以及282pb外延生长,之后除去p型区域282pa以及282pb。

162.(第四实施方式)

163.接下来,对第四实施方式进行说明。第四实施方式在电源开关电路110所包含的缓

冲器以及开关晶体管的数目这一点与第一实施方式不同。图34是表示第四实施方式中的电源开关电路110的构成的电路图。

164.如图34所示,电源开关电路110包含开关晶体管4111、4112、111以及112、和电源开关控制电路4113。开关晶体管4111以及4112例如是p沟道mos晶体管,连接在vdd布线与vvdd布线之间。开关晶体管4111的栅极与开关晶体管4112的栅极连接。电源开关控制电路4113与开关晶体管4111、4112、111以及112的各栅极连接,并控制开关晶体管4111、4112、111以及112的动作。通过电源开关控制电路4113切换开关晶体管4111、4112、111以及112的开/关,控制vdd布线与vvdd布线之间的导通。电源开关控制电路113包含缓冲器1300以及4300。

165.缓冲器1300与第一实施方式相同,具有反相器1310以及1320。输入信号in2输入到反相器1310,反相器1310的输出输入到开关晶体管111的栅极、开关晶体管112的栅极、以及反相器1320,从反相器1320输出输出信号out2。

166.缓冲器4300具有反相器4310以及4320。输入信号in1输入到反相器4310,反相器4310的输出输入到开关晶体管4111的栅极、开关晶体管4112的栅极、以及反相器4320,从反相器4320输出输出信号out1。

167.图35是表示缓冲器4300的构成的电路图。反相器4310包含两对p沟道mos晶体管以及n沟道mos晶体管。即,反相器4310包含p沟道mos晶体管4311p以及4312p、和n沟道mos晶体管4311n以及4312n。反相器4320包含两对p沟道mos晶体管以及n沟道mos晶体管。即,反相器4320包含p沟道mos晶体管4321p以及4322p、和n沟道mos晶体管4321n以及4322n。

168.图36以及图37是表示第四实施方式中的标准单元区域10的平面构成的示意图。图36主要示出电源开关控制电路4113的n沟道mos晶体管、开关晶体管111以及4111的布局。图37主要示出电源开关控制电路4113的p沟道mos晶体管、开关晶体管112以及4112的布局。除了图36以及图37双方所示的结构物之外,图37所示的结构物位于图36所示的结构物的上方。图38是表示第四实施方式中的标准单元区域10的剖视图。图38相当于沿着图36以及图37中的y19-y29线的剖视图。

169.如图36~图38所示,电源开关电路110与第三实施方式相同为双高。换句话说,电源开关电路110形成于在y方向上夹着电源线920配置的两个电源线910。而且,缓冲器1300、和开关晶体管111以及112构成为与第三实施方式相同。

170.缓冲器4300、和开关晶体管4111以及4112相对于设置了缓冲器1300的一方的电源线910设置于另一方的电源线910侧。

171.缓冲器4300具有与半导体区域481相同地向x方向延伸的半导体区域4181、和与半导体区域281相同地向x方向延伸的半导体区域4282。

172.半导体区域4181具有n型区域4481nc等n型区域、和沟道。如图36所示,在缓冲器4300设置有在y方向上与局部布线191ba并排的局部布线4191bc、在y方向上与局部布线191bb并排的局部布线4191be、以及在y方向上与局部布线191bc并排的局部布线4191bb。并且,在缓冲器4300设置有在与局部布线4191be之间夹着局部布线4191bb的局部布线4191bd、和在与局部布线4191bb之间夹着局部布线4191bd的局部布线4191ba。局部布线4191bb通过形成于绝缘膜105以及103的接触孔4511b内的导电体与电源线920连接。

173.半导体区域4282具有p型区域4481pc等p型区域、和沟道。如图37所示,在缓冲器4300设置有在y方向上与局部布线291ta并排的局部布线4291tc、在y方向上与局部布线

291tb并排的局部布线4291te、以及在y方向上与局部布线291tc并排的局部布线4291tb。并且,在缓冲器4300设置有在与局部布线4291te之间夹着局部布线4291tb的局部布线4291td、和在与局部布线4291tb之间夹着局部布线4291td的局部布线4291ta。局部布线4291tc通过形成于绝缘膜106的接触孔4521c内的导电体与局部布线4191bc连接。局部布线4291ta通过形成于绝缘膜106的接触孔4521a内的导电体与局部布线4191ba连接。

174.在局部布线4191bc以及局部布线4291tc的层叠体与局部布线4191be以及局部布线4291te的层叠体之间,形成有n沟道mos晶体管4311n以及p沟道mos晶体管4311p所共用的栅电极4132b。在局部布线4191be以及局部布线4291te的层叠体与局部布线4191bb以及局部布线4291tb的层叠体之间,形成有n沟道mos晶体管4312n以及p沟道mos晶体管4312p所共用的栅电极4132a。在局部布线4191bb以及局部布线4291tb的层叠体与局部布线4191bd以及局部布线4291td的层叠体之间,形成有n沟道mos晶体管4322n以及p沟道mos晶体管4322p所共用的栅电极4131a。在局部布线4191bd以及局部布线4291td的层叠体与局部布线4191ba以及局部布线4291ta的层叠体之间,形成有n沟道mos晶体管4321n以及p沟道mos晶体管4321p所共用的栅电极4131b。

175.在电源线920的上方设置有输入输入信号in2的信号线4951、和输出输出信号out2的信号线4952。信号线4951通过接触孔4541bb内的导电体与栅电极4132b连接,并通过接触孔4541ba内的导电体与栅电极4132a连接。信号线4952通过接触孔4531a内的导电体与局部布线4291ta连接。

176.在电源线910的上方设置有控制信号线4940。控制信号线4940通过接触孔4531c内的导电体与局部布线4291tc连接,通过接触孔4541aa内的导电体与栅电极4131a连接,并通过接触孔4541ab内的导电体与栅电极4131b连接。

177.在y方向上,在信号线4951以及4952与控制信号线4940之间设置有电源线930。电源线930通过接触孔4531b内的导电体与局部布线4291tb连接。

178.如图36所示,开关晶体管4111具有与半导体区域482相同地向x方向延伸的半导体区域4182。半导体区域4182具有n型区域和沟道。在开关晶体管4111设置有向y方向延伸的局部布线4192bb以及4192ba。局部布线4192ba通过形成于绝缘膜105以及103的接触孔4512a内的导电体与电源线910连接。

179.如图37所示,开关晶体管4112具有与半导体区域282相同地向x方向延伸的半导体区域4282。半导体区域4282具有p型区域和沟道。在开关晶体管4112经由绝缘膜106设置有形成在局部布线4192bb上的局部布线4292tb、和形成在局部布线4192ba上的局部布线4292ta。局部布线4292ta通过形成于绝缘膜106的接触孔4522a内的导电体与局部布线4192ba连接。局部布线4292tb通过形成于绝缘膜106的接触孔4522b内的导电体与局部布线4192bb连接。

180.在局部布线4192ba以及局部布线4292ta的层叠体与局部布线4192bb以及局部布线4292tb的层叠体之间,形成有开关晶体管4111以及4112所共用的栅电极4133。

181.电源线930通过接触孔4532b内的导电体与局部布线4292tb连接,控制信号线4940通过接触孔4542内的导电体与栅电极4133连接。

182.在本实施方式中,开关晶体管4111以及4112与开关晶体管111以及112相比驱动能力较小,在接通时在开关晶体管4111以及4112流过的电流比在开关晶体管111以及112流过

的电流小。因此,通过在接通开关晶体管4111以及4112之后接通开关晶体管111以及112,能够使供给到vvdd布线的电位的上升变得缓慢。在从vvdd布线向标准单元120急剧地供给电源电位的情况下,在vdd布线可能产生电源噪声。但是,通过如上述那样使电位的上升变得缓慢,能够抑制这样的误动作等。

183.此外,也可以是对于缓冲器1300和缓冲器4300而言,构成这些缓冲器的晶体管的构成相同。例如,也可以是缓冲器1300所包含的晶体管的数目与缓冲器4300所包含的晶体管的数目一致。

184.在图38中,两个电源线920通过共用化而图示为较粗的一个电源线920,所以电源线920比电源线910粗。在y方向上与电源开关电路110相邻的单元所包含的电源线910与电源开关电路110的电源线910相邻的情况下,也可以使这两个电源线910通过共用化成为较粗的一个电源线910。在其它的实施方式、变形例中也相同。

185.(第五实施方式)

186.接下来,对第五实施方式进行说明。第五实施方式在缓冲器所包含的p沟道mos晶体管与n沟道mos晶体管之间的上下关系这一点与第一实施方式的第一变形例不同。图39以及图40是表示第五实施方式中的标准单元区域10的平面构成的示意图。图39主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。图40主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管112的布局。除了图39以及图40双方所示的结构物之外,图40所示的结构物位于图39所示的结构物的上方。图41是表示第五实施方式中的标准单元区域10的剖视图。图41相当于沿着图39以及图40中的y20-y30线的剖视图。

187.在第五实施方式中,如图39~图41所示,与第一实施方式的第一变形例相比较,调换缓冲器1300所包含的p型区域和n型区域。例如,如图41所示,代替第一实施方式的第一变形例的n型区域481nb而设置p型区域481pb,代替第一实施方式的第一变形例的p型区域281pb而设置n型区域281nb。

188.另外,局部布线291tb经由形成于绝缘膜151以及103的接触孔5521b内的导电体与电源线920连接。电源线930在电源线910的上方,经由形成于绝缘膜151以及152的接触孔5531b内的导电体与局部布线191bb连接。

189.这样,在第五实施方式中,电源开关控制电路113所包含的n沟道mos晶体管1311n以及1321n形成于p沟道mos晶体管1311p以及1321p的上方。

190.其它的构成与第一实施方式相同。

191.通过第五实施方式,也能够得到与第一实施方式相同的效果。在其它的实施方式、变形例中,电源开关控制电路113所包含的n沟道mos晶体管也能够形成在p沟道mos晶体管的上方。

192.(第五实施方式的第一变形例)

193.接下来,对第五实施方式的第一变形例进行说明。第一变形例在电源开关电路110的轨道数目这一点与第五实施方式不同。图42以及图43是表示第五实施方式的第一变形例中的标准单元区域10的平面构成的示意图。图42主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。图43主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。除了图42以及图43双方所示的结构物之外,图43所示的结构物位于图42所示的结构物的上方。

194.在第一变形例中,如图42以及图43所示,电源开关电路110由四个轨道构成。换句话说,第一变形例具备组合了第五实施方式和第一实施方式的第五变形例的构成。

195.根据第一变形例,能够得到与第一实施方式的第五变形例相同的效果以及与第五实施方式相同的效果。

196.(第五实施方式的第二变形例)

197.接下来,对第五实施方式的第二变形例进行说明。第二变形例在电源开关电路110所包含的缓冲器以及开关晶体管的数目这一点与第五实施方式不同。图44以及图45是表示第五实施方式的第二变形例中的标准单元区域10的平面构成的示意图。图44主要示出电源开关控制电路113的p沟道mos晶体管、和开关晶体管111的布局。图45主要示出电源开关控制电路113的n沟道mos晶体管、和开关晶体管111的布局。除了图44以及图45双方所示的结构物之外,图45所示的结构物位于图44所示的结构物的上方。

198.第五实施方式的第二变形例具有与第四实施方式相同的电路构成。

199.在缓冲器1300中,在电源线910的上方形成控制信号线5941以及5942,在电源线920及其延长线的上方形成控制信号线5943。控制信号线5941与控制信号线5942经由形成于它们的上方的布线5900相互连接。控制信号线5943经由形成于与局部布线291ta等相同的层的局部布线与控制信号线5942连接,控制信号线5943与p沟道mos晶体管1321p的栅电极132连接。

200.在缓冲器4300中,控制信号线4940位于电源线920及其延长线的上方,电源线4930位于电源线910的上方。

201.换句话说,第二变形例具备组合了第五实施方式和第四实施方式的构成。

202.根据第一变形例,能够得到与第四实施方式相同的效果以及与第五实施方式相同的效果。

203.以上,基于各实施方式进行了本发明的说明,但本发明并不限定于上述实施方式所示的要件。对于这些点,能够在不脱离本发明的主旨的范围内进行变更,能够根据其应用方式适当地决定。

204.附图标记说明

205.1:半导体装置,110:电源开关电路,111、112、4111、4112:开关晶体管,113、4113:电源开关控制电路,120:标准单元,181、182:鳍片,181c、182c、281c、282c、481c、482c:沟道,181na、181nb、181nc、281nb、481na、481nb、481nc、4481nc:n型区域,182pa、182pb、281pa、281pb、281pc、282pa、282pb、481pb、482pa、482pb、4481pc:p型区域,191ba、191bb、191bc、192ba、192bb、291ta、291tb、291tc、291td、292ta、292tb:局部布线,281、282、481、482、4182、4282、4481、4482:半导体区域,910、920、930、4930:电源线,940、941、4940、5941、5942、5943:控制信号线,951、952、4951、4952:信号线,1311n、1321n、4311n、4312n、4321n、4322n:n沟道mos晶体管,1311p、1321p、4311p、4312p、4321p、4322p:p沟道mos晶体管。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。