显示装置

1.本技术要求于2020年6月2日在韩国知识产权局提交的第10

‑

2020

‑

0066615号韩国专利申请的优先权和权益,该韩国专利申请的全部内容通过引用包含于此。

技术领域

2.本公开的一些示例实施例的方面涉及一种显示装置。

背景技术:

3.显示装置是在显示屏或显示面板上显示图像的装置,并且包括例如液晶显示器(lcd)、有机发光二极管(oled)显示器等。显示装置可以用于各种电子装置(诸如移动电话、导航装置、数码相机、电子书、便携式游戏机、平板个人计算机和各种终端)中。

4.显示装置通常可以包括在行方向和列方向上布置的(例如,以矩阵构造布置的)多个像素。在每个像素内,可以包括各种元件(诸如晶体管和电容器)以及能够将信号供应到这些元件的各种布线。

5.显示装置可以包括位于上端处的凹口部。凹口部是非发射区域,并且相机、传感器等可以位于凹口部中。因为像素通常不布置在凹口部中,所以与其他区域相比,连接到位于凹口部的两侧上的布线的像素的数量非常小。因此,位于凹口部的两侧上的布线与位于其他区域中的布线相比具有负载差异,因此会发生亮度偏差。

6.在该背景技术部分中公开的以上信息仅用于增强对背景技术的理解,因此在该背景技术部分中讨论的信息不一定构成现有技术。

技术实现要素:

7.一些示例实施例的方面包括一种可以防止或减少根据各种组件(例如,布线或其他有源或无源电气组件)的位置的亮度偏差的发生的显示装置。

8.根据本公开的一些示例实施例,一种包括非发射区域的凹口部的显示装置包括:多个像素;多条扫描线,连接到多个像素;以及负载调整部,连接到在凹口部的两侧上且与凹口部的上端部相邻的扫描线,其中,负载调整部包括:负载调整布线,连接到在凹口部的两侧上的扫描线;第一负载调整电极,与负载调整布线在不同的层中,并且与负载调整布线叠置;以及第二负载调整电极,与负载调整布线和第一负载调整电极在不同的层中,并且与负载调整布线叠置。

9.根据一些示例实施例,负载调整部还可以与凹口部的下端部相邻。

10.根据一些示例实施例,扫描线和负载调整布线可以在第一方向上延伸,第一负载调整电极可以在与第一方向交叉的第二方向上延伸,并且第二负载调整电极可以整体地在负载调整部的上部处。

11.根据一些示例实施例,显示装置还可以包括:第一绝缘层,在第一负载调整电极与负载调整布线之间;以及第二绝缘层,在第二负载调整电极与负载调整布线之间,其中,第一负载调整电极可以在负载调整布线下方,并且第二负载调整电极可以在负载调整布线

上。

12.根据一些示例实施例,连接到在凹口部的两侧上的扫描线的像素的数量可以比连接到在除了凹口部的两侧之外的剩余区域中的扫描线的像素的数量小。

13.根据一些示例实施例,显示装置还可以包括:多条信号线,连接到多个像素;连接布线部,沿着凹口部的边缘,以将在凹口部的左侧处的信号线和在凹口部的右侧处的信号线连接;以及负载连接布线,将扫描线和负载调整部连接,并且负载连接布线可以与连接布线部相邻。

14.根据一些示例实施例,连接布线部可以包括在不同层中的第一连接布线、第二连接布线、第三连接布线和第四连接布线,在相邻层中的第一连接布线和第二连接布线可以不在剖面上彼此叠置,并且在相邻层中的第三连接布线和第四连接布线可以不在剖面上彼此叠置。

15.根据一些示例实施例,显示装置还可以包括顺序地沉积的多晶半导体层、第一栅极导电层、第二栅极导电层、氧化物半导体层、第三栅极导电层、第一数据导电层和第二数据导电层,第一连接布线可以在第一栅极导电层中,第二连接布线可以在第二栅极导电层中,第三连接布线可以在第一数据导电层中,并且第四连接布线可以在第二数据导电层中。

16.根据一些示例实施例,负载调整布线可以在第三栅极导电层中,第一负载调整电极可以在第二栅极导电层中,并且第二负载调整电极可以在第一数据导电层中。

17.根据一些示例实施例,负载连接布线可以在第三栅极导电层中以与负载调整布线一体地形成,并且可以不与连接布线部叠置。

18.根据一些示例实施例,显示装置还可以包括顺序地沉积的多晶半导体层、第一栅极导电层、第二栅极导电层、氧化物半导体层、第三栅极导电层、第一数据导电层和第二数据导电层,并且负载连接布线可以在第二数据导电层中。

19.根据一些示例实施例,负载连接布线可以与连接布线部叠置。

20.根据一些示例实施例,连接布线部可以包括在不同层中的第一连接布线、第二连接布线、第三连接布线和第四连接布线,第一连接布线可以在第一栅极导电层中,第二连接布线可以在第二栅极导电层中,第三连接布线可以在第三栅极导电层中,并且第四连接布线可以在第一数据导电层中。

21.根据一些示例实施例,负载调整布线可以在第二栅极导电层中,第一负载调整电极可以在多晶半导体层中,并且第二负载调整电极可以在第一数据导电层中。

22.根据一些示例实施例,负载调整布线可以在第三栅极导电层中,第一负载调整电极可以在第二栅极导电层中,并且第二负载调整电极可以在第一数据导电层中。

23.根据一些示例实施例,显示装置还可以包括连接到多个像素的发光控制线、旁路控制线和初始化控制线,扫描线可以包括第一扫描线和第二扫描线,并且负载调整部可以连接到第一扫描线或第二扫描线。

24.根据一些示例实施例,连接布线部可以包括:第一连接布线,将在凹口部的左侧处的发光控制线和在凹口部的右侧处的发光控制线连接;第二连接布线,将在凹口部的左侧处的旁路控制线和在凹口部的右侧处的旁路控制线连接;第三连接布线,将在凹口部的左侧处的初始化控制线和在凹口部的右侧处的初始化控制线连接;以及第四连接布线,将在凹口部的左侧处的第二扫描线和在凹口部的右侧处的第二扫描线连接,并且负载调整部可

以连接到第一扫描线。

25.根据一些示例实施例,多个像素中的每个可以包括:发光二极管(led),连接在施加有驱动电压的驱动电压线与施加有共电压的共电压线之间;驱动晶体管,连接在驱动电压线与发光二极管(led)之间;第二晶体管,连接在驱动晶体管的连接到驱动电压线的第一电极与施加有数据电压的数据线之间;第三晶体管,连接在驱动晶体管的连接到发光二极管(led)的第二电极与驱动晶体管的栅电极之间;以及第四晶体管,连接在驱动晶体管的栅电极与施加有第一初始化电压的第一初始化电压线之间,驱动晶体管和第二晶体管可以包括多晶半导体,并且第三晶体管和第四晶体管可以包括氧化物半导体。

26.根据一些示例实施例,第二晶体管的栅电极可以连接到第一扫描线,第三晶体管的栅电极可以连接到第二扫描线,并且第四晶体管的栅电极可以连接到初始化控制线。

27.根据一些示例实施例,多个像素中的每个还可以包括:第五晶体管,连接在驱动电压线与驱动晶体管之间;以及第七晶体管,连接在发光二极管(led)与施加有第二初始化电压的第二初始化电压线之间,第五晶体管的栅电极可以连接到发射控制线,并且第七晶体管的栅电极可以连接到旁路控制线。

28.根据一些示例实施例的显示装置还可以包括位于凹口部处的相机、接近传感器、照度传感器、手势传感器、运动传感器、指纹传感器和生物传感器中的至少一种或它们的组合。

29.根据本公开的一些示例实施例的显示装置可以包括:多个像素;多条扫描线,连接到多个像素;以及负载调整部,连接到在凹口部的两侧上的扫描线,其中,负载调整部包括:负载调整布线,连接到在凹口部的两侧上的扫描线;第一负载调整电极,在负载调整布线下方,并且与负载调整布线叠置;第一绝缘层,在负载调整布线与第一负载调整电极之间;第二负载调整电极,在负载调整布线上,并且与负载调整布线叠置;以及第二绝缘层,在负载调整布线与第二负载调整电极之间。

30.根据一些示例实施例,可以防止或减少显示装置的外围处的凹口部与其他区域之间的亮度偏差。

附图说明

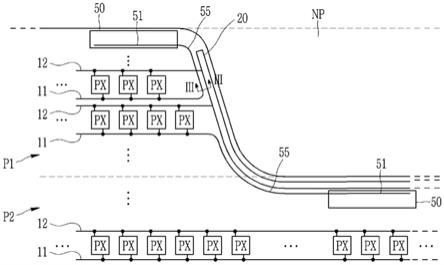

31.图1是示意性地示出根据一些示例实施例的显示装置的俯视平面图。

32.图2是示出根据一些示例实施例的显示装置的部分区域的俯视平面图。

33.图3是沿着图2的线iii

‑

iii截取的剖视图。

34.图4是示出根据一些示例实施例的显示装置的部分区域的俯视平面图。

35.图5是沿着图4的线v

‑

v截取的剖视图。

36.图6是根据一些示例实施例的显示装置的任一像素的电路图。

37.图7是示出根据一些示例实施例的显示装置的俯视平面图。

38.图8是沿着图7的线viii

‑

viii截取的剖视图。

39.图9至图14是顺序地示出根据一些示例实施例的显示装置的制造顺序的俯视平面图。

40.图15至图17是示出根据一些示例实施例的显示装置的部分区域的剖视图。

41.图18是示出根据一些示例实施例的显示装置的部分区域的俯视平面图。

42.图19是沿着图18的线xix

‑

xix截取的剖视图。

43.图20是示出根据一些示例实施例的显示装置的部分区域的俯视平面图。

44.图21是沿着图20的线xxi

‑

xxi截取的剖视图。

45.图22和图23是示出根据一些示例实施例的显示装置的部分区域的剖视图。

具体实施方式

46.在下文中将参照附图更充分地描述根据本发明的实施例的进一步的细节,在附图中示出了发明的示例实施例。如本领域技术人员将认识到的,在均不脱离本发明的精神或范围的情况下,可以以各种不同的方式修改所描述的实施例。

47.附图和描述本质上被认为是说明性的而非限制性的,贯穿说明书,同样的附图标记表示同样的元件。

48.另外,为了更好的理解和易于描述,任意地示出了附图中示出的每个构造的尺寸和厚度,但是根据本发明的实施例不限于此。在附图中,为了清楚起见,夸大了层、膜、面板、区域等的厚度。在附图中,为了更好的理解和易于描述,夸大了一些层和区域的厚度。

49.另外,将理解的是,当诸如层、膜、区域或基底的元件被称为“在”另一元件“上”时,该元件可以直接在所述另一元件上,或者也可以存在中间元件。相反,当元件被称为“直接在”另一元件“上”时,不存在中间元件。此外,在说明书中,词语“在

……

上”或“在

……

上方”是指位于目标部分上或下方,并且不一定是指基于重力方向位于目标部分的上侧上。

50.另外,除非明确地相反描述,否则词语“包括”及其变型将被理解为意指包括所陈述的元件,但是不排除任何其他元件。

51.此外,贯穿说明书,短语“在平面上”是指从顶部观看目标部分,并且短语“在剖面上”是指从侧面观看通过竖直切割目标部分而形成的剖面。

52.参照图1描述了根据一些示例实施例的显示装置。

53.图1是示意性地示出根据一些示例实施例的显示装置的俯视平面图。

54.如图1中所示,根据一些示例实施例的显示装置1000包括凹口部np。

55.凹口部np可以是非发射区域,并且可以位于显示装置1000的上端的中心处。然而,凹口部np的位置不限于此,并且可以以各种方式改变。例如,凹口部np可以位于显示装置1000的下端处。凹口部np的平面形状可以是近似四边形的。凹口部np的平面形状可以具有梯形形状,该梯形形状的上边比下边长。凹口部np的两侧(左侧和右侧)边缘可以由曲线形成。凹口部np是其中不显示屏幕的区域,并且具有各种功能的组件可以位于凹口部np中。例如,相机、接近传感器、照度传感器、手势传感器、运动传感器、指纹识别传感器和生物传感器中的至少一种或它们的组合可以位于凹口部np中。

56.可以在除了凹口部np之外的区域中显示屏幕。第一区域p1可以位于凹口部np的两侧(左侧和右侧)上。第二区域p2可以位于凹口部np和第一区域p1下方。第一区域p1和第二区域p2可以是发光区域。此时,可以在第一区域p1和第二区域p2的大部分上显示屏幕。然而,在第一区域p1和第二区域p2的边缘的一些区域中,可以设置其中不显示屏幕的区域,该区域被称为边框区域。

57.显示装置1000可以包括多个像素px。多个像素px可以沿着行方向和列方向以矩阵形式定位,并且可以接收图像信号,从而显示图像。然而,多个像素px的布置形式不限于此,

并且可以以各种方式改变。根据一些示例实施例,显示装置1000还可以包括多条布线。布线可以由多条扫描线、多条控制线、多条数据线、多条驱动电压线等构成。这些布线中的每条可以传输扫描信号、控制信号、数据信号和驱动电压。多条布线可以定位为在行方向或列方向上彼此交叉。另外,每个像素px可以包括连接到多条布线的多个晶体管、电容器和至少一个发光二极管(led)。即,显示装置1000可以由有机发光二极管显示器制成。然而,显示装置1000的类型不限于此,并且可以由各种类型的显示装置制成。例如,显示装置1000可以由液晶显示器、电泳显示器或电润湿显示装置制成。另外,根据一些示例实施例的显示装置1000也可以由下一代显示装置(诸如微发光二极管(led)(微led)显示装置、量子点发光二极管(led)(qled)显示装置或量子点有机发光二极管(qd

‑

oled)显示器)组成。

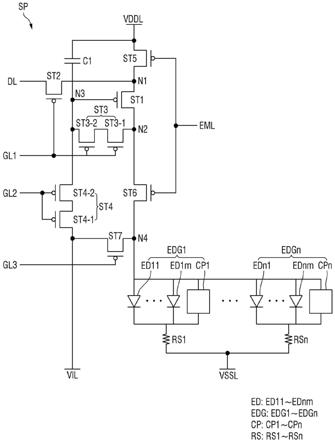

58.多个像素px可以位于第一区域p1和第二区域p2中。像素px不位于凹口部np中。位于同一行中的多个像素px可以连接到同一布线。此时,布线可以在行方向上延伸。例如,位于同一行中的多个像素px可以连接到同一扫描线。此外,位于同一列中的多个像素px可以连接到同一布线。此时,布线可以在列方向上延伸。例如,位于同一列中的多个像素px可以连接到同一数据线。

59.在第二区域p2中,可以针对每个像素行定位相似数量的像素px。因此,连接到每个像素行的布线的负载几乎相同。与位于第二区域p2中的一个像素行中的像素px的数量相比,位于第一区域p1中的一个像素行中的像素px的数量非常小。这是因为凹口部np位于第一区域p1之间,并且像素px不位于凹口部np中。因此,连接到第一区域p1中的每个像素行的布线的负载可以与连接到第二区域p2中的每个像素行的布线的负载不同。

60.参照图2至图5进一步描述根据一些示例实施例的用于减小第一区域pa1和第二区域pa2中的布线的负载差异的显示装置的结构。

61.图2是示出根据一些示例实施例的显示装置的部分区域的俯视平面图,并且图3是沿着图2的线iii

‑

iii截取的剖视图。图4是示出根据一些示例实施例的显示装置的部分区域的俯视平面图,并且图5是沿着图4的线v

‑

v截取的剖视图。图2至图5示出了根据一些示例实施例的显示装置的凹口部的外围。图2至图5示出了根据一些示例实施例的显示装置的凹口部的左边缘外围,但是根据一些示例实施例,凹口部的右边缘外围可以与左侧对称。

62.如图2中所示,根据一些示例实施例的显示装置包括多个像素px,并且多个像素px在行方向和列方向上布置。

63.根据一些示例实施例的显示装置还可以包括多条扫描线11。多条扫描线11可以在平面上在第一方向上延伸,并且第一方向可以是行方向。位于同一行中的像素px连接到同一扫描线11。例如,扫描线11可以由传输第一扫描信号的第一扫描信号线形成。连接到位于凹口部np的两侧上的扫描线11的像素px的数量比连接到位于除了凹口部np的两侧之外的其余区域的扫描线11的像素px的数量少。

64.即,连接到位于第一区域p1中的扫描线11的像素px的数量比连接到位于第二区域p2中的扫描线11的像素px的数量少。定位在相对于凹口部np位于左侧处的第一区域p1中的扫描线11可以不连接到定位在位于右侧处的第一区域p1中的扫描线11。将信号供应到扫描线11的驱动单元可以位于显示装置的两个边缘处,并且扫描线11可以从两侧上的驱动单元接收信号。这被称为双侧驱动。

65.根据一些示例实施例的显示装置还可以包括负载调整部50,负载调整部50能够控

制位于凹口部np的两侧处的扫描线11的负载。负载调整部50可以控制位于凹口部np的两侧处的扫描线11。即,负载调整部50可以连接到位于第一区域p1处的扫描线11,并且可以不连接到位于第二区域p2处的扫描线11。负载调整部50可以定位为与凹口部np的上端部相邻。负载调整部50被示出为位于凹口部np的上端部的左侧处,但是根据一些示例实施例,负载调整部50还可以位于凹口部np的上端部的右侧处。此外,负载调整部50还可以定位为与凹口部np的下端部相邻。位于第一区域p1中的多条扫描线11之中的部分可以连接到与凹口部np的上端部相邻的负载调整部50,并且另一部分可以连接到位于凹口部np的下端部处的负载调整部50。例如,基于第一区域p1的中心区域位于上侧处的扫描线11可以连接到与凹口部np的上端部相邻的负载调整部50。基于第一区域p1的中心区域位于下侧处的扫描线11可以连接到与凹口部np的下端部相邻的负载调整部50。

66.根据一些示例实施例的显示装置还可以包括将扫描线11和负载调整部50连接的负载连接布线55。负载调整部50可以包括负载调整布线51。负载调整布线51可以在平面上在第一方向上延伸,并且第一方向可以是行方向。即,负载调整布线51可以在与扫描线11平行的方向上延伸。负载连接布线55可以连接到负载调整布线51。在这种情况下,负载连接布线55可以与负载调整布线51位于同一层上并且与负载调整布线51一体地形成。然而,其不限于此,负载连接布线55可以与负载调整布线51位于不同的层上。负载连接布线55可以沿着凹口部np的边缘定位。负载连接布线55可以沿着凹口部np的左边缘和右边缘定位。

67.根据一些示例实施例的显示装置还可以包括多条信号线12。多条信号线12可以在平面上在第一方向上延伸,并且第一方向可以是行方向。位于同一行中的像素px连接到同一信号线12。为方便起见,示出了针对每个像素行定位一条信号线12,然而可以针对每个像素行定位多条信号线12。即,一个像素px可以连接到多条信号线12。例如,信号线12可以包括传输发光控制信号的发光控制线、传输旁路信号的旁路控制线、传输初始化控制信号的初始化控制线和传输第二扫描信号的第二扫描线。相对于凹口部np,定位在位于左侧处的第一区域p1中的信号线12可以连接到定位在位于右侧处的第一区域p1中的信号线12。将信号供应到信号线12的驱动单元可以位于显示装置的一侧边缘上,并且信号线12可以从一侧的驱动单元接收信号。这被称为单侧驱动。例如,产生将传输到发光控制线的发光控制信号的发光驱动器和产生将传输到初始化控制线的初始化控制信号的初始化驱动单元可以位于显示装置的左边缘上。产生将传输到旁路控制线的旁路信号的旁路驱动单元和产生将传输到第二扫描线的第二扫描信号的第二扫描驱动器可以位于显示装置的右边缘上。为了将信号从位于一侧的边缘上的驱动单元传输到另一侧的边缘,可以将位于凹口部np的左侧的第一区域p1中的信号线12和位于凹口部np的右侧的第一区域p1中的信号线12连接。

68.根据一些示例实施例的显示装置还可以包括将位于凹口部np的左侧处的信号线和位于凹口部np的右侧处的信号线连接的连接布线部20。连接布线部20可以沿着凹口部np的边缘定位。连接布线部20可以沿着凹口部np的左边缘、下边缘和右边缘定位。负载连接布线55可以定位为与连接布线部20相邻。在这种情况下,负载连接布线55可以不与连接布线部20叠置。

69.如图3中所示,连接布线部20可以包括彼此位于不同的层上的第一连接布线21、第二连接布线22、第三连接布线23和第四连接布线24。在这种情况下,负载连接布线55可以不与第一连接布线21、第二连接布线22、第三连接布线23和第四连接布线24叠置。

70.缓冲层111可以位于基底110上。缓冲层111可以具有单层或多层结构。缓冲层111可以包括有机绝缘材料或无机绝缘材料。第一栅极绝缘层141可以位于缓冲层111上。第一栅极绝缘层141可以包括氮化硅、氧化硅等。根据一些示例实施例,多晶半导体层可以位于缓冲层111与第一栅极绝缘层141之间。即,多晶半导体层共同表示位于缓冲层111与第一栅极绝缘层141之间的多晶半导体等。多晶半导体层可以包括多晶半导体材料。

71.第二栅极绝缘层142可以位于第一栅极绝缘层141上。第二栅极绝缘层142可以包括氮化硅、氧化硅等。包括第一连接布线21的第一栅极导电层可以位于第一栅极绝缘层141与第二栅极绝缘层142之间。即,第一连接布线21可以位于第一栅极导电层中。第一栅极导电层共同表示位于第一栅极绝缘层141与第二栅极绝缘层142之间的布线等。

72.第一层间绝缘层161可以位于第二栅极绝缘层142上。第一层间绝缘层161可以包括氮化硅、氧化硅等。包括第二连接布线22的第二栅极导电层可以位于第二栅极绝缘层142与第一层间绝缘层161之间。即,第二连接布线22可以位于第二栅极导电层中。第二栅极导电层共同表示位于第二栅极绝缘层142与第一层间绝缘层161之间的布线等。

73.第一连接布线21和第二连接布线22可以经由置于其间的第二栅极绝缘层142位于彼此相邻的层中。第一连接布线21和第二连接布线22可以不在剖面上彼此叠置。如果布置在相邻层中的布线彼此叠置,则布线可能短路。在根据一些示例实施例的显示装置中,通过将第一连接布线21和第二连接布线22布置为不叠置,可以防止或减少第一连接布线21与第二连接布线22之间的短路。

74.第三栅极绝缘层143可以布置在第一层间绝缘层161上。根据一些示例实施例,氧化物半导体层可以位于第一层间绝缘层161与第三栅极绝缘层143之间。氧化物半导体层可以包括位于第一层间绝缘层161与第三栅极绝缘层143之间的氧化物半导体等。氧化物半导体层可以包括一元金属氧化物(诸如氧化铟(in)、氧化锡(sn)或氧化锌(zn))、二元金属氧化物(诸如in

‑

zn基氧化物、sn

‑

zn基氧化物、al

‑

zn基氧化物、zn

‑

mg基氧化物、sn

‑

mg基氧化物、in

‑

mg基氧化物或in

‑

ga基氧化物)、三元氧化物(诸如in

‑

ga

‑

zn基氧化物、in

‑

al

‑

zn基氧化物、in

‑

sn

‑

zn基氧化物、sn

‑

ga

‑

zn基氧化物、al

‑

ga

‑

zn基氧化物、sn

‑

al

‑

zn基氧化物、in

‑

hf

‑

zn基氧化物、in

‑

la

‑

zn基氧化物、in

‑

ce

‑

zn基氧化物、in

‑

pr

‑

zn基氧化物、in

‑

nd

‑

zn基氧化物、in

‑

sm

‑

zn基氧化物、in

‑

eu

‑

zn基氧化物、in

‑

gd

‑

zn基氧化物、in

‑

tb

‑

zn基氧化物、in

‑

dy

‑

zn基氧化物、in

‑

ho

‑

zn基氧化物、in

‑

er

‑

zn基氧化物、in

‑

tm

‑

zn基氧化物、in

‑

yb

‑

zn基氧化物或in

‑

lu

‑

zn基氧化物)以及四元金属氧化物(诸如in

‑

sn

‑

ga

‑

zn基氧化物、in

‑

hf

‑

ga

‑

zn基氧化物、in

‑

al

‑

ga

‑

zn基氧化物、in

‑

sn

‑

al

‑

zn基氧化物、in

‑

sn

‑

hf

‑

zn基氧化物或in

‑

hf

‑

al

‑

zn基氧化物)之中的至少一种。例如,氧化物半导体层可以包括in

‑

ga

‑

zn基氧化物之中的氧化铟镓锌(igzo)。

75.第二层间绝缘层162位于第三栅极绝缘层143上。包括负载连接布线55的第三栅极导电层可以位于第三栅极绝缘层143与第二层间绝缘层162之间。即,负载连接布线55可以位于第三栅极导电层中。第三栅极导电层共同表示位于第三栅极绝缘层143与第二层间绝缘层162之间的布线等。

76.第三层间绝缘层180可以位于第二层间绝缘层162上。包括第三连接布线23的第一数据导电层可以位于第二层间绝缘层162与第三层间绝缘层180之间。即,第三连接布线23可以位于第一数据导电层中。第一数据导电层共同表示位于第二层间绝缘层162与第三层

间绝缘层180之间的布线等。

77.包括第四连接布线24的第二数据导电层可以位于第三层间绝缘层180上。即,第四连接布线24可以位于第二数据导电层中。第二数据导电层共同表示位于第三层间绝缘层180上的布线等。

78.第三连接布线23和第四连接布线24可以经由置于其间的第三层间绝缘层180位于彼此相邻的层中。第三连接布线23和第四连接布线24可以不在剖面上彼此叠置。在根据一些示例实施例的显示装置中,通过将第三连接布线23和第四连接布线24布置为不叠置,可以防止或减少第三连接布线23与第四连接布线24之间的短路。

79.如图4和图5中所示,负载调整部50连接到负载连接布线55。负载调整部50可以包括负载调整布线51、第一负载调整电极52和第二负载调整电极53。

80.多条负载调整布线51可以在平面上在第一方向上延伸,并且第一方向可以是行方向。负载调整布线51可以在与扫描线11平行的方向上延伸。负载调整布线51可以位于第三栅极导电层中。负载调整布线51可以位于第三栅极绝缘层143与第二层间绝缘层162之间。负载调整布线51可以连接到负载连接布线55。负载调整布线51可以与负载连接布线55位于同一层上。即,负载调整布线51和负载连接布线55可以位于第三栅极导电层中。负载调整布线51和负载连接布线55可以一体地形成。负载调整布线51可以通过负载连接布线55连接到扫描线11。因此,施加到扫描线11的信号可以传输到负载调整布线51。

81.多个第一负载调整电极52可以在平面上在第二方向上延伸,并且第二方向可以与第一方向交叉。例如,第二方向可以是列方向。因此,第一负载调整电极52可以与负载调整布线51交叉。第一负载调整电极52可以与负载调整布线51叠置。第一负载调整电极52可以与负载调整布线51位于不同的层上。第一负载调整电极52可以位于第二栅极导电层中。第一负载调整电极52可以位于第二栅极绝缘层142与第一层间绝缘层161之间。第一负载调整电极52可以位于负载调整布线51下方。绝缘层可以位于第一负载调整电极52与负载调整布线51之间。例如,第一层间绝缘层161和第三栅极绝缘层143可以位于第一负载调整电极52与负载调整布线51之间。

82.第二负载调整电极53可以整体地位于负载调整部50的上部处。第二负载调整电极53可以与负载调整布线51叠置。第二负载调整电极53可以与负载调整布线51位于不同的层上。第二负载调整电极53可以位于第一数据导电层中。第二负载调整电极53可以位于第二层间绝缘层162与第三层间绝缘层180之间。第二负载调整电极53可以位于负载调整布线51上。绝缘层可以位于第二负载调整电极53与负载调整布线51之间。例如,第二层间绝缘层162可以位于第二负载调整电极53与负载调整布线51之间。

83.绝缘层可以位于第一负载调整电极52与第二负载调整电极53之间。例如,第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第一负载调整电极52与第二负载调整电极53之间。位于第一负载调整电极52与第二负载调整电极53之间的绝缘层可以包括开口54。开口54可以形成在第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162中。开口54不与负载调整布线51叠置。第二负载调整电极53可以位于开口54中。第二负载调整电极53可以通过开口54连接到第一负载调整电极52。第一负载调整电极52和第二负载调整电极53彼此叠置,并且第一负载调整电极52和第二负载调整电极53可以在第一负载调整电极52和第二负载调整电极53不与负载调整布线51叠置的部分处连接。驱动电

压elvdd(见图6)可以施加到第一负载调整电极52和/或第二负载调整电极53。如果驱动电压elvdd施加到第一负载调整电极52,则驱动电压elvdd也可以传输到第二负载调整电极53。如果驱动电压elvdd施加到第二负载调整电极53,则驱动电压elvdd也可以传输到第一负载调整电极52。驱动电压elvdd可以施加到第一负载调整电极52和第二负载调整电极53。

84.第一负载调整电极52和负载调整布线51经由置于它们之间的绝缘层叠置,从而形成第一电容器c1。此外,第二负载调整电极53和负载调整布线51经由置于其间的绝缘层彼此叠置,从而形成第二电容器c2。在这种情况下,第一电容器c1的电容可以由第一负载调整电极52与负载调整布线51的叠置面积、位于第一负载调整电极52与负载调整布线51之间的绝缘层的厚度等确定。第二电容器c2的电容可以由第二负载调整电极53与负载调整布线51的叠置面积、位于第二负载调整电极53与负载调整布线51之间的绝缘层的厚度等确定。通过控制负载调整部50的第一电容器c1和第二电容器c2的电容,可以改变连接到负载调整部50的扫描线11的负载。因此,通过控制连接到位于第一区域p1中的扫描线11的负载调整部50的电容器的电容,可以将位于第一区域p1中的扫描线11的负载控制为与位于第二区域p2中的扫描线11的负载相似。因此,能够防止或减少在第一区域p1和第二区域p2中出现亮度差异的情况。

85.在上面,已经描述了多个第一负载调整电极52并排延伸并且第二负载调整电极53具有与多条负载调整布线51和多个第一负载调整电极52叠置的总体板形状,但是其不限于此。例如,多个第二负载调整电极53可以并排延伸,并且第一负载调整电极52可以具有与多条负载调整布线51和多个第二负载调整电极53叠置的总体板形状。

86.在下文中,参照图6描述根据一些示例实施例的显示装置的一个像素和每条布线的连接关系。

87.图6是根据一些示例实施例的显示装置的一个像素的电路图。

88.如图6中所示,根据一些示例实施例的显示装置的一个像素px包括连接到若干信号线的多个晶体管t1、t2、t3、t4、t5、t6、t7和t8、存储电容器cst和发光二极管led。

89.多条信号线127、128、151、152、153、154、155、156、171、172和741连接到一个像素px。多条信号线包括第一初始化电压线127、第二初始化电压线128、第一扫描线151、第二扫描线152、初始化控制线153、旁路控制线154、发光控制线155、参考电压线156、数据线171、驱动电压线172和共电压线741。

90.第一扫描线151连接到栅极驱动器,以将第一扫描信号gw传输到第二晶体管t2。在第二扫描线152中,与施加到第一扫描线151的电压极性相反的电压可以与第一扫描线151的信号同时施加。例如,当高电压施加到第一扫描线151时,低电压可以施加到第二扫描线152。第二扫描线152将第二扫描信号gc传输到第三晶体管t3。

91.初始化控制线153将初始化控制信号gi传输到第四晶体管t4。旁路控制线154将旁路信号gb传输到第七晶体管t7和第八晶体管t8。旁路控制线154可以由下一级处的第一扫描线151组成。发光控制线155将发光控制信号em传输到第五晶体管t5和第六晶体管t6。

92.数据线171是传输从数据驱动器产生的数据电压data的布线,并且由发光二极管(led)led发射的亮度根据施加到像素px的数据电压data而改变。

93.驱动电压线172施加驱动电压elvdd,并且参考电压线156施加参考电压veh。第一初始化电压线127传输第一初始化电压vint1,并且第二初始化电压线128传输第二初始化

电压vint2。共电压线741将共电压elvss施加到发光二极管led的阴极。根据一些示例实施例,施加到驱动电压线172、参考电压线156、第一初始化电压线127和第二初始化电压线128以及共电压线741的每个电压可以是恒定电压。

94.在下文中,更详细地描述多个晶体管的结构和连接关系。

95.驱动晶体管t1可以具有p型晶体管特性并且包括多晶半导体。驱动晶体管t1可以根据第二晶体管t2的开关操作来接收数据电压data,以将驱动电流供应到发光二极管led的阳极。因为根据输出到发光二极管led的阳极的驱动电流的大小来调整发光二极管led的亮度,所以可以根据施加到像素px的数据电压data来调整发光二极管led的亮度。为了这个目的,驱动晶体管t1的第一电极定位为接收驱动电压elvdd并且经由第五晶体管t5连接到驱动电压线172。此外,驱动晶体管t1的第一电极连接到第二晶体管t2的第二电极,以接收数据电压data。另一方面,驱动晶体管t1的第二电极定位为朝向发光二极管led输出电流,并且经由第六晶体管t6连接到发光二极管led的阳极。此外,驱动晶体管t1的第二电极将施加到第一电极的数据电压data传输到第三晶体管t3。另一方面,驱动晶体管t1的栅电极连接到存储电容器cst的一个电极(在下文中称为第二存储电极)。因此,驱动晶体管t1的栅电极的电压根据存储在存储电容器cst中的电压而改变,并且因此由驱动晶体管t1输出的驱动电流改变。另外,存储电容器cst也用于针对一帧保持驱动晶体管t1的栅电极的电压恒定。

96.第二晶体管t2可以具有p型晶体管特性,并且可以包括多晶半导体。第二晶体管t2是将数据电压data接收到像素px中的晶体管。第二晶体管t2的栅电极连接到第一扫描线151。第二晶体管t2的第一电极连接到数据线171。第二晶体管t2的第二电极连接到驱动晶体管t1的第一电极。当第二晶体管t2由通过第一扫描线151传输的第一扫描信号gw之中的低电压导通时,通过数据线171传输的数据电压data传输到驱动晶体管t1的第一电极。

97.第三晶体管t3可以具有n型晶体管特性,并且可以包括氧化物半导体。第三晶体管t3电连接到驱动晶体管t1的第二电极和驱动晶体管t1的栅电极。结果,第三晶体管t3是允许补偿电压传输到存储电容器cst的第二存储电极的晶体管,通过驱动晶体管t1使数据电压data改变为所述补偿电压。第三晶体管t3的栅电极连接到第二扫描线152,第三晶体管t3的第一电极连接到驱动晶体管t1的第二电极。第三晶体管t3的第二电极连接到存储电容器cst的第二存储电极和驱动晶体管t1的栅电极。第三晶体管t3由通过第二扫描线152传输的第二扫描信号gc之中的高电压导通,以将驱动晶体管t1的栅电极和驱动晶体管t1的第二电极连接,并将施加到驱动晶体管t1的栅电极的电压传输到存储电容器cst的第二存储电极,以存储到存储电容器cst。

98.第四晶体管t4可以具有n型晶体管特性,并且可以包括氧化物半导体。第四晶体管t4用于使驱动晶体管t1的栅电极和存储电容器cst的第二存储电极初始化。第四晶体管t4的栅电极连接到初始化控制线153,并且第四晶体管t4的第一电极连接到第一初始化电压线127。第四晶体管t4的第二电极经由第三晶体管t3的第二电极连接到存储电容器cst的第二存储电极和驱动晶体管t1的栅电极。第四晶体管t4由通过初始化控制线153传输的初始化控制信号gi之中的高电压导通,并且在这种情况下,第一初始化电压vint1传输到驱动晶体管t1的栅电极和存储电容器cst的第二存储电极。因此,驱动晶体管t1的栅电极和存储电容器cst的电压被初始化。

99.第五晶体管t5可以具有p型晶体管特性,并且可以包括多晶半导体。第五晶体管t5用于将驱动电压elvdd传输到驱动晶体管t1。第五晶体管t5的栅电极连接到发光控制线155,第五晶体管t5的第一电极连接到驱动电压线172,第五晶体管t5的第二电极连接到驱动晶体管t1的第一电极。

100.第六晶体管t6可以具有p型晶体管特性,并且可以包括多晶半导体。第六晶体管t6用于将从驱动晶体管t1输出的驱动电流传输到发光二极管led。第六晶体管t6的栅电极连接到发光控制线155,第六晶体管t6的第一电极连接到驱动晶体管t1的第二电极,并且第六晶体管t6的第二电极连接到发光二极管led的阳极。

101.第七晶体管t7可以具有p型晶体管特性,并且可以包括多晶半导体。第七晶体管t7用于使发光二极管led的阳极初始化。第七晶体管t7的栅电极连接到旁路控制线154,第七晶体管t7的第一电极连接到发光二极管led的阳极,第七晶体管t7的第二电极连接到第二初始化电压线128。如果第七晶体管t7由旁路信号gb之中的低电压导通,则第二初始化电压vint2施加到待初始化的发光二极管(led)led的阳极。

102.第八晶体管t8可以具有p型晶体管特性,并且可以包括多晶半导体。第八晶体管t8的栅电极连接到旁路控制线154,第八晶体管t8的第一电极连接到参考电压线156,第八晶体管t8的第二电极连接到驱动晶体管t1的第一电极。当第八晶体管t8由旁路信号gb之中的低电压导通时,参考电压veh施加到驱动晶体管t1的第一电极。

103.在上面,一个像素px被描述为包括八个晶体管t1至t8以及一个存储电容器cst,但是不限于此,晶体管的数量、电容器的数量以及它们之间的连接关系可以以各种方式改变。

104.根据一些示例实施例,驱动晶体管t1可以包括多晶半导体。此外,第三晶体管t3和第四晶体管t4可以包括氧化物半导体。第二晶体管t2、第五晶体管t5、第六晶体管t6、第七晶体管t7和第八晶体管t8可以包括多晶半导体。然而,根据本发明的实施例不限于此,第二晶体管t2、第五晶体管t5、第六晶体管t6、第七晶体管t7和第八晶体管t8之中的至少任一者可以包括氧化物半导体。根据一些示例实施例,通过使第三晶体管t3和第四晶体管t4与驱动晶体管t1包括不同的半导体材料,可以更稳定地执行驱动并且可以改善可靠性。

105.连接到根据一些示例实施例的显示装置中的负载调整部50的扫描线11可以是第一扫描线151。然而,连接到负载调整部50的扫描线11不限于此,并且可以是另一信号线。例如,连接到负载调整部50的扫描线11可以是第二扫描线152。作为另一示例,连接到负载调整部50的扫描线11中的一部分可以是第一扫描线151,并且另一部分可以是第二扫描线152。

106.连接布线部20可以连接到多条信号线12。例如,连接布线部20可以连接到发光控制线155、旁路控制线154、初始化控制线153和第二扫描线152。连接布线部20可以包括第一连接布线21、第二连接布线22、第三连接布线23和第四连接布线24。在这种情况下,第一连接布线21可以连接到发光控制线155。第一连接布线21可以将位于凹口部np的左侧处的发光控制线155和位于凹口部np的右侧处的发光控制线155连接。第二连接布线22可以连接到旁路控制线154。第二连接布线22可以连接到位于凹口部np的左侧处的旁路控制线154和位于凹口部np的右侧处的旁路控制线154。第三连接布线23可以连接到初始化控制线153。第三连接布线23可以将位于凹口部np的左侧处的初始化控制线153和位于凹口部np的右侧处的初始化控制线153连接。第四连接布线24可以连接到第二扫描线152。第四连接布线24可

以将位于凹口部np的左侧处的第二扫描线152和位于凹口部np的右侧处的第二扫描线152连接。

107.连接布线部20与信号线12之间的连接关系仅是示例,并且它们之间的连接关系可以以各种方式改变。例如,第一连接布线21可以连接到旁路控制线154,并且第二连接布线22可以连接到发光控制线155。第三连接布线23可以连接到第二扫描线152,并且第四连接布线24可以连接到初始化控制线153。

108.在下文中,参照图7至图14进一步描述驱动晶体管t1、第三晶体管t3、第四晶体管t4等的在平面和剖面上的结构。

109.图7是示出根据一些示例实施例的显示装置的俯视平面图,图8是沿着图7的线viii

‑

viii截取的剖视图,并且图9至图14是顺序地示出根据一些示例实施例的显示装置的制造顺序的俯视平面图。图7至图14示出了两个相邻像素,并且两个像素可以彼此对称。在下文中,主要描述位于左侧处的像素。

110.如图7至图14中所示,包括驱动晶体管t1的沟道1132、第一电极1131和第二电极1133的多晶半导体层可以位于基底110上。图9示出了多晶半导体层。与驱动晶体管t1一样,多晶半导体层还可以包括第二晶体管t2、第五晶体管t5、第六晶体管t6、第七晶体管t7和第八晶体管t8的每个沟道、第一电极和第二电极。

111.驱动晶体管t1的沟道1132可以在平面上形成为弯曲形状。然而,驱动晶体管t1的沟道1132的形状不限于此,并且可以以各种方式改变。例如,驱动晶体管t1的沟道1132可以弯曲为不同的形状,或者可以形成为棒形状。驱动晶体管t1的第一电极1131和第二电极1133可以位于驱动晶体管t1的沟道1132的两侧上。驱动晶体管t1的第一电极1131在平面上上下延伸,使得向上延伸的部分可以连接到第二晶体管t2的第二电极,并且向下延伸的部分可以连接到第五晶体管t5的第二电极。驱动晶体管t1的第二电极1133在平面上向下延伸,并且可以连接到第六晶体管t6的第一电极。

112.缓冲层111可以位于基底110与包括驱动晶体管t1的沟道1132、第一电极1131和第二电极1133的多晶半导体层之间。

113.第一栅极绝缘层141可以位于包括驱动晶体管t1的沟道1132、第一电极1131和第二电极1133的多晶半导体层上。

114.包括驱动晶体管t1的栅电极1151的第一栅极导电层可以位于第一栅极绝缘层141上。图10一起示出了多晶半导体层和第一栅极导电层。

115.驱动晶体管t1的栅电极1151可以与驱动晶体管t1的沟道1132叠置。驱动晶体管t1的沟道1132被驱动晶体管t1的栅电极1151覆盖。

116.第一栅极导电层可以包括第一初始化电压线127、第一扫描线151、发光控制线155和旁路控制线154。第一初始化电压线127、第一扫描线151、发光控制线155和旁路控制线154可以在近似水平方向上延伸。第一初始化电压线127可以连接到第四晶体管t4的第一电极。第一扫描线151可以连接到第二晶体管t2的栅电极。第五晶体管t5的栅电极和第六晶体管t6的栅电极可以连接到发光控制线155。第七晶体管t7的栅电极和第八晶体管t8的栅电极可以连接到旁路控制线154。

117.如上所述,第一连接布线21可以位于第一栅极导电层中。因此,第一连接布线21可以与驱动晶体管t1的栅电极1151位于同一层上。第一连接布线21可以与第一初始化电压线

127、第一扫描线151、发光控制线155和旁路控制线154位于同一层上。

118.在形成包括驱动晶体管t1的栅电极1151的第一栅极导电层之后,可以执行掺杂工艺。被第一栅极导电层覆盖的多晶半导体层不被掺杂,并且多晶半导体层的未被第一栅极导电层覆盖的部分被掺杂,从而具有与导体相同的特性。此时,可以用p型掺杂剂执行掺杂工艺,并且包括多晶半导体的驱动晶体管t1、第二晶体管t2、第五晶体管t5、第六晶体管t6、第七晶体管t7和第八晶体管t8可以具有p型晶体管特性。

119.第二栅极绝缘层142可以位于包括驱动晶体管t1的栅电极1151的第一栅极导电层和第一栅极绝缘层141上。

120.在第二栅极绝缘层142上,可以定位包括存储电容器cst的第一存储电极1153的第二栅极导电层。图11一起示出了多晶半导体层、第一栅极导电层和第二栅极导电层。

121.第一存储电极1153与驱动晶体管t1的栅电极1151叠置,从而形成存储电容器cst。存储电容器cst的第一存储电极1153具有开口1152。存储电容器cst的第一存储电极1153的开口1152可以与驱动晶体管t1的栅电极1151叠置。

122.如上所述,第二连接布线22和第一负载调整电极52可以位于第二栅极导电层中。因此,第二连接布线22和第一负载调整电极52可以与存储电容器cst的第一存储电极1153位于同一层上。

123.第一层间绝缘层161可以位于包括存储电容器cst的第一存储电极1153的第二栅极导电层上。

124.在第一层间绝缘层161上,可以定位氧化物半导体层,氧化物半导体层包括第三晶体管t3的沟道3137、第一电极3136和第二电极3138以及第四晶体管t4的沟道4137、第一电极4136和第二电极4138。图12一起示出了多晶半导体层、第一栅极导电层、第二栅极导电层和氧化物半导体层。

125.第三晶体管t3的沟道3137、第一电极3136和第二电极3138以及第四晶体管t4的沟道4137、第一电极4136和第二电极4138可以彼此连接以一体地形成。第三晶体管t3的第一电极3136和第二电极3138可以位于第三晶体管t3的沟道3137的两侧上。第四晶体管t4的第一电极4136和第二电极4138可以位于第四晶体管t4的沟道4137的两侧上。第三晶体管t3的第二电极3138可以连接到第四晶体管t4的第二电极4138。

126.第三栅极绝缘层143可以位于包括第三晶体管t3的沟道3137、第一电极3136和第二电极3138以及第四晶体管t4的沟道4137、第一电极4136和第二电极4138的氧化物半导体层上。第三栅极绝缘层143可以位于氧化物半导体层和第一层间绝缘层161的整个表面上。因此,第三栅极绝缘层143可以覆盖第三晶体管t3的沟道3137、第一电极3136和第二电极3138以及第四晶体管t4的沟道4137、第一电极4136和第二电极4138的上表面和侧表面。然而,根据本公开的实施例不限于此,第三栅极绝缘层143可以不位于氧化物半导体层和第一层间绝缘层161的整个表面上。例如,第三栅极绝缘层143可以与第三晶体管t3的沟道3137叠置,并且可以不与第一电极3136和第二电极3138叠置。此外,第三栅极绝缘层143可以与第四晶体管t4的沟道4137叠置,并且可以不与第一电极4136和第二电极4138叠置。

127.包括第三晶体管t3的栅电极3151和第四晶体管t4的栅电极4151的第三栅极导电层可以位于第三栅极绝缘层143上。图13一起示出了多晶半导体层、第一栅极导电层、第二栅极导电层、氧化物半导体层和第三栅极导电层。

128.第三晶体管t3的栅电极3151可以与第三晶体管t3的沟道3137叠置。第四晶体管t4的栅电极4151可以与第四晶体管t4的沟道4137叠置。

129.第三栅极导电层还可以包括初始化控制线153、第二扫描线152和参考电压线156。初始化控制线153、第二扫描线152和参考电压线156可以在近似水平方向上延伸。初始化控制线153可以连接到第四晶体管t4的栅电极4151。第二扫描线152可以连接到第三晶体管t3的栅电极3151。参考电压线156可以连接到第八晶体管t8的第一电极。

130.如上所述,负载调整布线51和负载连接布线55可以位于第三栅极导电层中。因此,负载调整布线51和负载连接布线55可以与第三晶体管t3的栅电极3151和第四晶体管t4的栅电极4151位于同一层上。负载调整布线51和负载连接布线55可以与初始化控制线153、第二扫描线152和参考电压线156位于同一层上。

131.在形成包括第三晶体管t3的栅电极3151和第四晶体管t4的栅电极4151的第三栅极导电层之后,可以执行掺杂工艺。氧化物半导体层的被第三栅极导电层覆盖的部分不被掺杂,并且氧化物半导体层的未被第三栅极导电层覆盖的部分被掺杂,从而具有与导体相同的特性。第三晶体管t3的沟道3137可以位于栅电极3151下方,以与栅电极3151叠置。第三晶体管t3的第一电极3136和第二电极3138可以不与栅电极3151叠置。第四晶体管t4的沟道4137可以位于栅电极4151下方,以与栅电极4151叠置。第四晶体管t4的第一电极4136和第二电极4138可以不与栅电极4151叠置。可以用n型掺杂剂执行氧化物半导体层的掺杂工艺,并且包括氧化物半导体层的第三晶体管t3和第四晶体管t4可以具有n型晶体管特性。

132.第二层间绝缘层162可以位于包括第三晶体管t3的栅电极3151和第四晶体管t4的栅电极4151的第三栅极导电层上。第二层间绝缘层162可以具有第一开口1165、第二开口1166、第三开口3165、第四开口3166、第五开口4165和第六开口4166。

133.第一开口1165可以与驱动晶体管t1的栅电极1151的至少一部分叠置。第一开口1165还可以形成在第三栅极绝缘层143、第一层间绝缘层161和第二栅极绝缘层142中。第一开口1165可以与第一存储电极1153的开口1152叠置。第一开口1165可以位于第一存储电极1153的开口1152内。第二开口1166可以与第三晶体管t3的第二电极3138的至少一部分叠置。第二开口1166还可以形成在第三栅极绝缘层143中。

134.第三开口3165可以与驱动晶体管t1的第二电极1133的至少一部分叠置。第三开口3165还可以形成在第三栅极绝缘层143、第一层间绝缘层161、第二栅极绝缘层142和第一栅极绝缘层141中。第四开口3166可以与第三晶体管t3的第一电极3136的至少一部分叠置。第四开口3166还可以形成在第三栅极绝缘层143中。

135.第五开口4165可以与第四晶体管t4的第一电极4136的至少一部分叠置。第五开口4165还可以形成在第三栅极绝缘层143中。第六开口4166可以与第一初始化电压线127的至少一部分叠置。第六开口4166还可以形成在第三栅极绝缘层143、第一层间绝缘层161和第二栅极绝缘层142中。

136.在第二层间绝缘层162上,可以定位包括第一连接电极1175、第二连接电极3175和第三连接电极4175的第一数据导电层。图14一起示出了多晶半导体层、第一栅极导电层、第二栅极导电层、氧化物半导体层、第三栅极导电层和第一数据导电层。

137.第一连接电极1175可以与驱动晶体管t1的栅电极1151叠置。第一连接电极1175可以通过第一开口1165和第一存储电极1153的开口1152连接到驱动晶体管t1的栅电极1151。

第一连接电极1175可以与第三晶体管t3的第二电极3138叠置。第一连接电极1175可以连接到第三晶体管t3的第二电极3138。因此,驱动晶体管t1的栅电极1151和第三晶体管t3的第二电极3138可以通过第一连接电极1175连接。

138.第二连接电极3175可以与驱动晶体管t1的第二电极1133叠置。第二连接电极3175可以通过第三开口3165连接到驱动晶体管t1的第二电极1133。第二连接电极3175可以与第三晶体管t3的第一电极3136叠置。第二连接电极3175可以通过第四开口3166连接到第三晶体管t3的第一电极3136。因此,驱动晶体管t1的第二电极1133和第三晶体管t3的第一电极3136可以通过第二连接电极3175连接。

139.第三连接电极4175可以与第四晶体管t4的第一电极4136叠置。第三连接电极4175可以通过第五开口4165连接到第四晶体管t4的第一电极4136。第三连接电极4175可以与第一初始化电压线127叠置。第三连接电极4175可以通过第六开口4166连接到第一初始化电压线127。因此,第四晶体管t4的第一电极4136和第一初始化电压线127可以通过第三连接电极4175连接。

140.第一数据导电层还可以包括第二初始化电压线128。第二初始化电压线128可以在近似水平方向上延伸。第二初始化电压线128可以连接到第七晶体管t7的第二电极。

141.如上所述,第三连接布线23和第二负载调整电极53可以位于第一数据导电层中。因此,第三连接布线23和第二负载调整电极53可以与第一连接电极1175、第二连接电极3175和第三连接电极4175位于同一层上。第三连接布线23和第二负载调整电极53可以与第二初始化电压线128位于同一层上。

142.第三层间绝缘层180可以位于包括第一连接电极1175、第二连接电极3175和第三连接电极4175的第一数据导电层上。

143.包括数据线171和驱动电压线172的第二数据导电层可以位于第三层间绝缘层180上。数据线171和驱动电压线172可以近似在竖直方向上延伸。数据线171可以连接到第二晶体管t2。数据线171可以连接到第二晶体管t2的第一电极。驱动电压线172可以连接到第五晶体管t5。驱动电压线172可以连接到第五晶体管t5的第一电极。驱动电压线172可以连接到存储电容器cst。驱动电压线172可以连接到存储电容器cst的第一存储电极1153。相邻像素的存储电容器cst的第一存储电极1153彼此连接,并且可以在基本上水平的方向上延伸。

144.如上所述,第四连接布线24可以位于第二数据导电层中。因此,第四连接布线24可以与数据线171和驱动电压线172位于同一层上。

145.根据一些示例实施例,钝化层可以位于包括数据线171和驱动电压线172的第二数据导电层上,并且阳极可以位于钝化层上。阳极可以连接到第六晶体管t6并且可以接收驱动晶体管t1的输出电流。分隔物可以位于阳极上。分隔物包括开口,并且分隔物的开口可以与阳极叠置。发光元件层可以位于分隔物的开口中。阴极可以位于发光元件层和分隔物上。阳极、发光元件层和阴极可以形成发光二极管led。

146.如上所述,在根据一些示例实施例的显示装置中,驱动晶体管t1可以包括多晶半导体,并且第三晶体管t3和第四晶体管t4可以包括氧化物半导体。如上所述,由于第三晶体管t3和第四晶体管t4与驱动晶体管t1包括不同的半导体材料,因此可以更稳定地驱动它们并且可以改善可靠性。

147.在上面,描述了一个像素中包括的晶体管以及连接到其的布线在平面和剖面上的

位置,但是它们不限于此。每个构成元件在平面和剖面上的位置可以以各种方式改变。

148.在下文中,参照图15至图17描述根据上述图1至图6的一些示例实施例的显示装置的示例变型。

149.图15至图17是示出根据一些示例实施例的显示装置的一些区域的剖视图。图15至图17示出了根据图5中示出的一些示例实施例的显示装置的负载调整部的剖面形状的许多示例变型。

150.根据图5中示出的一些示例实施例的显示装置的负载调整部50包括位于第三栅极导电层中的负载调整布线51、位于第二栅极导电层中的第一负载调整电极52和位于第一数据导电层中的第二负载调整电极53。其中定位有根据一些示例实施例的显示装置的负载调整部50的负载调整布线51、第一负载调整电极52和第二负载调整电极53的层可以以各种方式改变,并且在下面描述了示例。

151.如图15中所示,根据一些示例实施例的显示装置的负载调整部50可以包括位于第三栅极导电层中的负载调整布线51、位于第二栅极导电层中的第一负载调整电极52和位于第二数据导电层中的第二负载调整电极53。

152.绝缘层可以位于第二负载调整电极53与负载调整布线51之间。例如,第二层间绝缘层162和第三层间绝缘层180可以位于第二负载调整电极53与负载调整布线51之间。

153.绝缘层可以位于第一负载调整电极52与第二负载调整电极53之间。例如,第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180可以位于第一负载调整电极52与第二负载调整电极53之间。位于第一负载调整电极52与第二负载调整电极53之间的绝缘层可以包括开口54。开口54可以形成在第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180中。开口54不与负载调整布线51叠置。第二负载调整电极53可以位于开口54内。第二负载调整电极53可以通过开口54连接到第一负载调整电极52。

154.根据一些示例实施例,如图16中所示,根据一些示例实施例的显示装置的负载调整部50可以包括位于第二栅极导电层中的负载调整布线51、位于第一栅极导电层中的第一负载调整电极52和位于第一数据导电层中的第二负载调整电极53。

155.绝缘层可以位于第一负载调整电极52与负载调整布线51之间。例如,第二栅极绝缘层142可以位于第一负载调整电极52与负载调整布线51之间。

156.绝缘层可以位于第二负载调整电极53与负载调整布线51之间。例如,第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第二负载调整电极53与负载调整布线51之间。

157.绝缘层可以位于第一负载调整电极52与第二负载调整电极53之间。例如,第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第一负载调整电极52与第二负载调整电极53之间。位于第一负载调整电极52与第二负载调整电极53之间的绝缘层可以包括开口54。开口54可以位于第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162中。开口54不与负载调整布线51叠置。第二负载调整电极53可以位于开口54内。第二负载调整电极53可以通过开口54连接到第一负载调整电极52。

158.根据一些示例实施例,如图17中所示,显示装置的负载调整部50可以包括位于第

二栅极导电层中的负载调整布线51、位于第一栅极导电层中的第一负载调整电极52和位于第二数据导电层中的第二负载调整电极53。

159.绝缘层可以位于第一负载调整电极52与负载调整布线51之间。例如,第二栅极绝缘层142可以位于第一负载调整电极52与负载调整布线51之间。

160.绝缘层可以位于第二负载调整电极53与负载调整布线51之间。例如,第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180可以位于第二负载调整电极53与负载调整布线51之间。

161.绝缘层可以位于第一负载调整电极52与第二负载调整电极53之间。例如,第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180可以位于第一负载调整电极52与第二负载调整电极53之间。位于第一负载调整电极52与第二负载调整电极53之间的绝缘层可以包括开口54。开口54可以形成在第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180中。开口54不与负载调整布线51叠置。第二负载调整电极53可以位于开口54内。第二负载调整电极53可以通过开口54连接到第一负载调整电极52。

162.接下来,参照图18至图21描述根据一些示例实施例的显示装置。

163.如图18至图21中所示,根据一些示例实施例的显示装置与根据图1至图6中示出的示例实施例的显示装置的大部分相同,从而省略对相同部分的描述。根据一些示例实施例,负载连接布线和负载调整部的连接关系、负载连接布线和连接布线部的位置关系、连接布线部中包括的每条连接布线的位置等与先前的示例实施例的负载连接布线和负载调整部的连接关系、负载连接布线和连接布线部的位置关系、连接布线部中包括的每条连接布线的位置等不同。

164.图18是示出根据一些示例实施例的显示装置的部分区域的俯视平面图,并且图19是沿着图18的线xix

‑

xix截取的剖视图。图20是示出根据一些示例实施例的显示装置的部分区域的俯视平面图,并且图21是沿着图20的线xxi

‑

xxi截取的剖视图。

165.如图18中所示,根据一些示例实施例的显示装置包括位于凹口部np的两侧上的多个像素px、连接到多个像素px的多条扫描线11以及连接到扫描线11的负载调整部50。

166.根据一些示例实施例的显示装置还可以包括连接到多个像素px的多条信号线12以及将位于凹口部np的左侧处的信号线12和位于凹口部np的右侧处的信号线12连接的连接布线部20。

167.根据一些示例实施例的显示装置还可以包括将扫描线11和负载调整部50连接的负载连接布线55。负载连接布线55可以定位为与连接布线部20相邻。在先前的示例实施例中,描述了负载连接布线55不与连接布线部20叠置,然而在本示例实施例中,负载连接布线55可以与连接布线部20叠置。

168.当负载连接布线55不与连接布线部20叠置时,可以防止或减少负载连接布线55与连接布线部20之间的短路的情况。此外,在连接布线部20中,可以防止第一连接布线21、第二连接布线22、第三连接布线23和第四连接布线24短路。然而,在这种情况下,因为用于定位负载连接布线55的区域相对小,所以可以控制负载的扫描线11的数量也减少。

169.当负载连接布线55与连接布线部20叠置时,可以宽地确保能够包括负载连接布线55的区域。因此,能够控制更多扫描线11的负载,并且可以使用于减小亮度偏差的区域加

宽。

170.如图19中所示,连接布线部20可以包括位于不同层中的第一连接布线21、第二连接布线22、第三连接布线23和第四连接布线24。在这种情况下,负载连接布线55可以与第一连接布线21、第二连接布线22、第三连接布线23和第四连接布线24之中的至少一者叠置。

171.第一连接布线21可以位于第一栅极导电层中。第一连接布线21可以位于第一栅极绝缘层141与第二栅极绝缘层142之间。第二连接布线22可以位于第二栅极导电层中。第二连接布线22可以位于第二栅极绝缘层142与第一层间绝缘层161之间。第一连接布线21和第二连接布线22可以经由第二栅极绝缘层142位于彼此相邻的层中。第一连接布线21和第二连接布线22可以不在剖面上叠置。

172.第三连接布线23可以位于第三栅极导电层中。第三连接布线23可以位于第三栅极绝缘层143与第二层间绝缘层162之间。第四连接布线24可以位于第一数据导电层中。第四连接布线24可以位于第二层间绝缘层162与第三层间绝缘层180之间。第三连接布线23和第四连接布线24可以经由第二层间绝缘层162位于彼此相邻的层中。第三连接布线23和第四连接布线24可以不在剖面上彼此叠置。

173.负载连接布线55可以位于第二数据导电层中。负载连接布线55可以位于第三层间绝缘层180上。第四连接布线24和负载连接布线55可以经由第三层间绝缘层180位于彼此相邻的层中。第四连接布线24和负载连接布线55可以不在剖面上彼此叠置。

174.如图20和图21中所示,负载调整部50连接到负载连接布线55。负载调整部50可以包括负载调整布线51、第一负载调整电极52和第二负载调整电极53。

175.多条负载调整布线51可以在平面上在第一方向上延伸,并且第一方向可以是行方向。负载调整布线51可以位于第二栅极导电层中。负载调整布线51可以位于第二栅极绝缘层142与第一层间绝缘层161之间。

176.负载调整布线51可以连接到负载连接布线55。负载调整布线51可以与负载连接布线55位于不同的层上。负载调整布线51和负载连接布线55可以部分地叠置。例如,负载调整布线51的端部和负载连接布线55的端部可以彼此叠置。绝缘层可以位于负载调整布线51与负载连接布线55之间。例如,第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180可以位于负载调整布线51与负载连接布线55之间。位于负载调整布线51与负载连接布线55之间的绝缘层可以包括开口56。开口56可以形成在第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180中。开口56可以与负载调整布线51和负载连接布线55叠置。负载连接布线55可以位于开口56内。负载连接布线55可以通过开口56连接到负载调整布线51。负载调整布线51可以通过负载连接布线55连接到扫描线11。因此,施加到扫描线11的信号可以传输到负载调整布线51。

177.多个第一负载调整电极52可以在平面上在第二方向上延伸,并且第二方向可以与第一方向交叉。例如,第二方向可以是列方向。第一负载调整电极52可以与负载调整布线51叠置。第一负载调整电极52可以与负载调整布线51位于不同的层中。第一负载调整电极52可以位于多晶半导体层中。第一负载调整电极52可以位于缓冲层111与第一栅极绝缘层141之间。第一负载调整电极52可以位于负载调整布线51下方。绝缘层可以位于第一负载调整电极52与负载调整布线51之间。例如,第一栅极绝缘层141和第二栅极绝缘层142可以位于第一负载调整电极52与负载调整布线51之间。

178.第二负载调整电极53可以整体地位于负载调整部50的上部处。第二负载调整电极53可以与负载调整布线51叠置。第二负载调整电极53可以与负载调整布线51位于不同的层上。第二负载调整电极53可以位于第一数据导电层中。第二负载调整电极53可以位于第二层间绝缘层162与第三层间绝缘层180之间。第二负载调整电极53可以位于负载调整布线51上。绝缘层可以位于第二负载调整电极53与负载调整布线51之间。例如,第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第二负载调整电极53与负载调整布线51之间。

179.绝缘层可以位于第一负载调整电极52与第二负载调整电极53之间。例如,第一栅极绝缘层141、第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第一负载调整电极52与第二负载调整电极53之间。位于第一负载调整电极52与第二负载调整电极53之间的绝缘层可以包括开口54。开口54可以形成在第一栅极绝缘层141、第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162中。开口54不与负载调整布线51叠置。第二负载调整电极53可以位于开口54内。第二负载调整电极53可以通过开口54连接到第一负载调整电极52。第一负载调整电极52和第二负载调整电极53可以在第一负载调整电极52和第二负载调整电极53彼此叠置且第一负载调整电极52和第二负载调整电极53不与负载调整布线51叠置的部分处连接。驱动电压elvdd可以施加到第一负载调整电极52和/或第二负载调整电极53。

180.第一负载调整电极52和负载调整布线51经由绝缘层叠置,从而形成第一电容器c1。此外,第二负载调整电极53和负载调整布线51经由绝缘层叠置,从而形成第二电容器c2。通过调整负载调整部50的第一电容器c1和第二电容器c2的电容,可以控制连接到负载调整部50的扫描线11的负载,从而防止或减少在第一区域p1和第二区域p2中出现亮度差异。

181.在上面,多个第一负载调整电极52并排延伸,第二负载调整电极53具有与多条负载调整布线51和多个第一负载调整电极52叠置的总体板形状,然而其不限于此,并且可以以各种方式改变。

182.在下文中,参照图22和图23描述根据如上述图18至图21中示出的一些示例实施例的显示装置的示例变型。

183.图22和图23是示出根据一些示例实施例的显示装置的部分区域的剖视图。图22和图23示出了根据如图21中示出的一些示例实施例的显示装置的负载调整部的剖面形状的许多示例变型。

184.根据如图21中示出的一些示例实施例的显示装置的负载调整部50包括位于第二栅极导电层中的负载调整布线51、位于多晶半导体层中的第一负载调整电极52和位于第一数据导电层中的第二负载调整电极53。其中定位有根据一些示例实施例的显示装置的负载调整部50的负载调整布线51、第一负载调整电极52和第二负载调整电极53的层可以以各种方式改变,并且描述了示例。

185.如图22中所示,根据一些示例实施例的显示装置的负载调整部50可以包括位于第三栅极导电层中的负载调整布线51、位于第二栅极导电层中的第一负载调整电极52和位于第一数据导电层中的第二负载调整电极53。

186.绝缘层可以位于负载调整布线51与负载连接布线55之间。例如,第二层间绝缘层

162和第三层间绝缘层180可以位于负载调整布线51与负载连接布线55之间。位于负载调整布线51与负载连接布线55之间的绝缘层可以包括开口56。开口56可以形成在第二层间绝缘层162和第三层间绝缘层180中。开口56可以与负载调整布线51和负载连接布线55叠置。负载连接布线55可以位于开口56内。负载连接布线55可以通过开口56连接到负载调整布线51。

187.绝缘层可以位于第一负载调整电极52与负载调整布线51之间。例如,第一层间绝缘层161和第三栅极绝缘层143可以位于第一负载调整电极52与负载调整布线51之间。

188.绝缘层可以位于第二负载调整电极53与负载调整布线51之间。例如,第二层间绝缘层162可以位于第二负载调整电极53与负载调整布线51之间。

189.绝缘层可以位于第一负载调整电极52与第二负载调整电极53之间。例如,第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第一负载调整电极52与第二负载调整电极53之间。位于第一负载调整电极52与第二负载调整电极53之间的绝缘层可以包括开口54。开口54可以形成在第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162中。开口54不与负载调整布线51叠置。第二负载调整电极53可以位于开口54内。第二负载调整电极53可以通过开口54连接到第一负载调整电极52。

190.根据一些示例实施例,如图23中所示,根据一些示例实施例的显示装置的负载调整部50可以包括位于第二栅极导电层中的负载调整布线51、位于第一栅极导电层中的第一负载调整电极52和位于第一数据导电层中的第二负载调整电极53。

191.绝缘层可以位于负载调整布线51与负载连接布线55之间。例如,第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180可以位于负载调整布线51与负载连接布线55之间。位于负载调整布线51与负载连接布线55之间的绝缘层可以包括开口56。开口56可以形成在第一层间绝缘层161、第三栅极绝缘层143、第二层间绝缘层162和第三层间绝缘层180中。开口56可以与负载调整布线51和负载连接布线55叠置。负载连接布线55可以位于开口56内。负载连接布线55可以通过开口56连接到负载调整布线51。

192.绝缘层可以位于第一负载调整电极52与负载调整布线51之间。例如,第二栅极绝缘层142可以位于第一负载调整电极52与负载调整布线51之间。

193.绝缘层可以位于第二负载调整电极53与负载调整布线51之间。例如,第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第二负载调整电极53与负载调整布线51之间。

194.绝缘层可以位于第一负载调整电极52与第二负载调整电极53之间。例如,第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162可以位于第一负载调整电极52与第二负载调整电极53之间。位于第一负载调整电极52与第二负载调整电极53之间的绝缘层可以包括开口54。开口54可以形成在第二栅极绝缘层142、第一层间绝缘层161、第三栅极绝缘层143和第二层间绝缘层162中。开口54不与负载调整布线51叠置。第二负载调整电极53可以位于开口54内。第二负载调整电极53可以通过开口54连接到第一负载调整电极52。

195.虽然已经结合当前被认为是实际的示例实施例的内容描述了本公开,但是将理解的是,根据本发明的实施例不限于公开的示例实施例。相反,其旨在涵盖包括在所附权利要求及其等同物的精神和范围内的各种修改和等同布置。

196.<附图标记中的一些的描述>

197.11:扫描线

198.12:信号线

199.20:连接布线部

200.21:第一连接布线

201.22:第二连接布线

202.23:第三连接布线

203.24:第四连接布线

204.50:负载调整部

205.51:负载调整布线

206.52:第一负载调整电极

207.53:第二负载调整电极

208.54、56:开口

209.110:基底。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。