1.本公开涉及半导体存储器件技术领域,更为具体来说,本公开涉及一种半导体结构及其形成方法、半导体存储器件。

背景技术:

2.动态随机存储器(dram,全称dynamic random access memory)是计算机中常用的半导体存储器件,包含排列成矩阵结构的多个dramcell(存储单元);每个存储单元主要由一个晶体管(transistor)和一个由晶体管(transistor)操控的电容器(cell capacitor)组成,各个存储单元之间通过字线(wordline)和位线(bitline)进行电性连接,数据从位线输入后通过晶体管传送到电容器中,而储存于电容器中的数据通过晶体管和位线进行输出。

3.常规的半导体存储结构中,位线的下方设置有位线接触部(bitlinecontact),位线接触部一般通过填充多晶硅的方式实现,位线接触部作为位线与晶体管连接的桥梁,位线接触部的对面设置存储接触部(storage contact),但随着半导体存储器件集成度的增加,为了快速地传输数据,用于制作位线的材料的电阻往往较低,位线与存储接触部之间的高电容值是造成动态随机存储器性能下降的主要原因之一。因此,如何降低位线与存储接触部之间的电容值成为了本领域技术人员亟待解决的技术问题和始终研究的重点。

技术实现要素:

4.为了解决位线与存储接触部之间的电容值较大的问题,本公开发明人发现可以通过减小两者之间的对视面积或增加两者之间的距离实现降低位线与存储接触部之间的电容值的目的,但由于半导体存储器件集成度的要求,要增加位线与存储接触部之间的距离几乎不可能实现,因而本公开采用减小位线与存储接触部之间的对视面积方式减小电容,具体通过省去多晶硅填充位线接触部的方式降低位线高度,以降低位线朝向存储接触部的面积,进而降低位线与存储接触部之间的电容值。

5.根据本公开的一个或多个实施例,半导体结构包括半导体衬底、第一位线槽、第二位线槽及位线。半导体衬底具有有源区,第一位线槽设置于有源区上,第二位线槽设置于第一位线槽内且与有源区连接,位线从有源区向上延伸且位于第一位线槽和第二位线槽中。

6.根据本公开的一个或多个实施例,一种动态随机存储器,包括:本公开一个或多个实施例的半导体结构。

7.根据本公开的一个或多个实施例,一种电子设备,可包括:本公开一个或多个实施例的动态随机存储器。

8.根据本公开的一个或多个实施例,一种半导体结构的形成方法,包括如下的步骤:提供半导体衬底,半导体衬底具有有源区;在有源区的上方形成第一位线槽;在第一位线槽内形成第二位线槽,第二位线槽与有源区连接;在有源区上形成位线,位线位于第一位线槽以及第二位线槽中。

9.本公开的有益效果为:

10.与现有技术相比,本公开能够在不使用传统方案的位线接触部的多晶硅的情况下形成位线,使位线仅仅通过阻挡金属与有源层连接,从而显著地降低了位线的高度、减少了位线的面积,进而能够极大地降低位线与存储接触部之间的电容,从而显著地提升使用本公开的半导体存储器件性能。而且,本公开省略了传统位线加工工艺的位线接触部处多晶硅沉积步骤,与传统方式相比,本公开提供的位线加工工艺上更为简单,较适于广泛地推广和应用。

附图说明

11.图1为本公开一些实施例中有源区、第一隔离区、介质层及第一位线槽的剖面结构示意图。

12.图2为本公开一些实施例中通过侧墙制程处理后的有源区、第一隔离区、介质层及第一位线槽的剖面结构示意图。

13.图3为本公开一些实施例中有源区、第一隔离区、介质层、第一位线槽及第二位线槽的剖面结构示意图。

14.图4为本公开一些实施例中在图3结构的基础上设置的阻挡金属、位线材料层及再次沉积的介质层的剖面结构示意图。

15.图5为本公开一些实施例中对图4结构中的再次沉积的介质层、位线材料层及阻挡金属进行选择性刻蚀后的剖面结构示意图。

16.图6为本公开一些实施例中对图5的结构进行介质层填充、第二隔离区设置、第二隔离区回蚀及与介质层相同的材料沉积后形成的结构的剖面示意图。

17.图7为利用本公开一些实施例的方法形成具有位线的器件剖面结构示意图。

18.图8为利用常规加工方法形成具有位线的器件剖面结构示意图。

19.图9为利用本公开形成的没有多晶硅接触部的位线平面结构示意图。

20.图10为利用常规加工方法形成位线接触部的平面结构示意图。

21.图中,

22.100、有源区;200、第一隔离区;300、介质层;400、第一位线槽;500、第二位线槽;600、位线材料层;700、阻挡金属;800、位线;900、第二隔离区;101、接触材料区;102、间隔层。

具体实施方式

23.以下,将参照附图来描述本公开的实施例。但是应该理解,这些描述只是示例性的,而并非要限制本公开的范围。此外,在以下说明中,省略了对公知结构和技术的描述,以避免不必要地混淆本公开的概念。

24.在附图中示出了根据本公开实施例的各种结构示意图。这些图并非是按比例绘制的,其中为了清楚表达的目的,放大了某些细节,并且可能省略了某些细节。图中所示出的各种区域、层的形状以及它们之间的相对大小、位置关系仅是示例性的,实际中可能由于制造公差或技术限制而有所偏差,并且本领域技术人员根据实际所需可以另外设计具有不同形状、大小、相对位置的区域/层。

25.在本公开的上下文中,当将一层/元件称作位于另一层/元件“上”时,该层/元件可以直接位于该另一层/元件上,或者它们之间可以存在居中层/元件。另外,如果在一种朝向中一层/元件位于另一层/元件“上”,那么当调转朝向时,该层/元件可以位于该另一层/元件“下”。

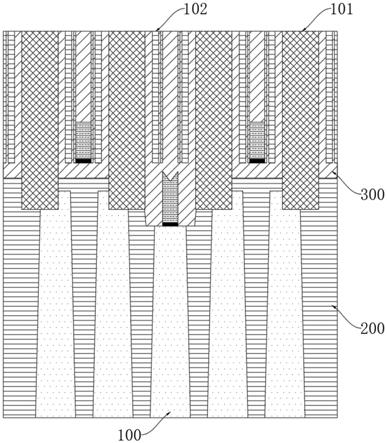

26.如图1-7所示,在本公开的另一些实施例中,提供了一种半导体结构。半导体结构包括半导体衬底,半导体衬底具有有源区100。半导体衬底例如可以是体硅衬底、绝缘体上硅(soi)衬底、锗衬底、绝缘体上锗(goi)衬底、硅锗衬底、iii-v族化合物半导体衬底或通过执行选择性外延生长(seg)获得的外延薄膜衬底。半导体结构包括位线800,位线800设置于有源区100的上方,位线800可以是埋入式位线,能够电性连接。

27.如图3-7所示,更为具体地,半导体结构包括阻挡金属700、第一位线槽400、第二位线槽500及位线800。阻挡金属700具有与位线800直接连接的上表面以及具有与有源区100直接连接的下表面,阻挡金属的材质可以包括例如tin、ti/tin、tisin、tan或wn。第一位线槽400设置于有源区100上,第二位线槽500设置于第一位线槽400内,第二位线槽500与有源区100连接。即本公开一些实施例的有源区100上方设置有第二位线槽500,例如可以通过沟槽形成工艺制作;阻挡金属设置于第二位线槽500内,处于位线800的下方。第二位线槽500,内部填充有介质层300。第二位线槽500,上方设置有与第二位线槽500连通的第一位线槽400,第一位线槽400例如可以通过沟槽形成工艺制作;位线800从有源区向上延伸,位于第二位线槽500和第一位线槽400中。第一位线槽400内部也填充有介质层300;位线处于介质层中,介质层填充在位线与第一位线槽内壁之间的空间内以及位线与第二位线槽内壁之间的空间内,介质层包绕位线。本公开的一些实施例能够将存储接触部对面的位线的面积减少至原本的一半以下,从而极大地降低了位线与存储接触部之间的电容值。

28.在本公开的另一些实施例中,提供了一种动态随机存储器(dram,全称dynamic random access memory),包括本公开任一实施例中的半导体结构800。对于现有技术加工出的用于多晶硅形成的位线接触部,请参阅图10,图10为利用常规加工方法形成位线接触部的平面结构示意图。对于本公开形成的无多晶硅接触部的位线,请参阅图9,图9为利用本公开形成的没有多晶硅接触部的位线平面结构示意图。本公开提供的位线设计方案适用于多种具有位线的半导体存储器件。本公开的一些实施例中还提供了一种电子设备,包括:本公开一个或多个实施例的动态随机存储器,电子设备例如可包括智能电话、计算机、平板电脑、可穿戴智能设备、人工智能设备、移动电源等。

29.本公开一些实施例中提供了一种半导体结构的形成方法。该方法能够省略传统位线加工工艺的位线接触部处多晶硅沉积步骤,使加工出的位线没有多晶硅,形成位线接触部。不仅工艺上更为简单,而且显著地降低了位线的高度,以使位线与存储接触部之间的对视面积更小,从而能够明显降低位线与存储接触部之间的电容,提升了半导体存储器件的性能,特别适于动态随机存储器(dram,全称dynamic random access memory)使用。具体地,该形成方法包括如下步骤。

30.请参阅图1,图1为本公开一些实施例中有源区、第一隔离区、介质层及第一位线槽的剖面结构示意图。在半导体衬底上形成有源区100,本公开的一些实施例中,多个有源区100可以交错地设置,多个有源区100之间、上部及周围设置第一隔离区200,通过隔离区200将所有有源区100交错形成的空间填充满且包围起来,并在隔离区上方沉积介质层300,通

过对介质层300和第一隔离区200依次地进行刻蚀(etch)处理的方式形成第一位线槽400,例如可以是在半导体衬底上形成第一介质层,在第一介质层形成光刻胶图案,并暴露要形成第一沟槽的第一开口,在第开口中对半导体衬底进行刻蚀形成第一位线槽;考虑到栅极(gate)的裕度(margin),本实施例在可接受的范围内能够以尽可能大的尺寸进行刻蚀,以暴露出有源区100。本公开的一些实施例中,有源区(active)100的材料为硅(sub silicon),第一隔离区200的材料为二氧化硅(sio2),介质层300的材料为氮化硅(sin)。

31.请参阅图2,图2为本公开一些实施例中通过侧墙制程处理后的有源区、第一隔离区、介质层及第一位线槽的剖面结构示意图。请参阅图3,图3为本公开一些实施例中有源区、第一隔离区、介质层、第一位线槽及第二位线槽的剖面结构示意图。基于侧墙结构进行刻蚀处理,在第一位线槽400内形成第二位线槽500,以侧墙为掩膜对半导体衬底进行刻蚀形成第二位线槽500,第二位线槽500与有源区100连接。本公开形成的第一位线槽400较大,可通过侧墙(spacer)制程的方式在整个半导体结构上方沉积介质层后进行刻蚀,以使第一位线槽400内的介质层300遮挡住有源区100以外的其他有源区100,即仅仅露出部分有源区100及旁边的第一隔离区200,从而能够避免位线与旁边临近的有源区可能发生的桥接(bridge)问题,提高本公开提供的方案的可靠性;还应当理解的是,本公开一些实施例附图中采用相同的填充图案的部分可以表示相同的材料,对于侧墙制程后形成的结构。本公开一些实施例中,在已形成的第一位线槽400基础上,本公开一些实施例对第一位线槽400下方的第一隔离区200和部分有源区100进行刻蚀(etch)处理的方式形成第二位线槽500,第二位线槽500与第一位线槽400相连通;形成第二位线槽500后的结构示意,在本公开的一个或多个实施例中,本公开为了形成后述图5中位线800的结构,在形成第一位线槽400之后,在整个半导体结构表面沉积介质层300后采用各向异性刻蚀,在第一位线槽400的侧壁形成侧墙,以基于侧墙结构形成第二位线槽500,从而得到截面宽度不同的第一位线槽400和第二位线槽500,第一位线槽400宽度大于第二位线槽500宽度,本公开的一些实施例中,第二位线槽500的纵截面宽度为相邻有源区100间距的1.2~1.4倍,即为相邻栅间距(gate pitch)的1.2~1.4倍。

32.本公开通过如下方式形成位线:在第二位线槽和第一位线槽中沉积阻挡金属和位线材料层,在导电层上形成第二介质层,在第二介质层上形成位线掩模,对第二介质层、位线材料层和阻挡金属进行刻蚀从而形成位线结构。

33.形成位线结构的具体说明如下:

34.请参阅图4,图4为本公开一些实施例中在图3结构的基础上设置的阻挡金属、位线材料层及再次沉积的介质层的剖面结构示意图。位线材料填充步骤,在整个半导体结构表面沉积位线材料层,包括向第二位线槽500内沉积位线材料,本公开在第二位线槽500中填满了位线材料,以及沿介质层300表面沉积位线材料,在第一位线槽400中沿着内壁沉积位线材料,以形成位线材料层600,位线材料层600中部具有凹槽,该凹槽深度的设置能够调节位线的高度,在本公开的一些实施例中,位线材料层600中部的凹槽纵截面呈v形,即位线材料沉积后形成“水波模样”的位线材料层600;在本公开的一些实施例中,位线材料为钨(符号w,英文名称tungsten),然后在位线材料层600上方再次沉积介质层300,此处的介质层作为掩模层(hardmasklayer)使用。在本公开的另一些实施例中,该形成方法还包括如下步骤;在向第二位线槽500内沉积位线材料以及沿介质层300表面沉积位线材料的过程中,位

线材料层600厚度的两倍大于第二位线槽500的纵截面宽度时,调整位线材料层600的台阶覆盖性(step coverage),以避免位线材料层中部填充不足的问题,保证合适且饱满的位线材料层600填充,以提高位线形成的可靠性和信任度。基于纵截面呈v形的位线材料层600中部的凹槽设计和台阶覆盖性调整,与现有技术相比,本公开能够在没有位线接触部的多晶硅的条件下形成位线800,位线800能够在不通过多晶硅的情况下连接有源区。

35.在本公开的另一些实施例中,该形成方法还包括如下步骤;在沉积位线材料前,还包括向第二位线槽500内和介质层300表面沉积阻挡金属700的步骤,在本公开的一些实施例中,阻挡金属700的材料为钛(符号ti,英文名称titanium)或氮化钛(tin)。

36.请参阅图5,图5为本公开一些实施例中对图4结构中的再次沉积的介质层、位线材料层以及阻挡金属进行选择性刻蚀后的剖面结构示意图。将位线材料层进行刻蚀形成位线;对位线材料层600及其上部的介质层300均进行选择性刻蚀处理,以形成伸入至第二位线槽500内且与有源区100连接的位线800。在对位线材料层600进行选择性刻蚀处理后,还包括选择性刻蚀阻挡金属700的步骤;本实施例中,可选择性刻蚀的选择区域可以如图5中区域,以使位线材料层600(本实施例指的是位线800)、阻挡金属700、有源区100依次地直接连接,以明显区别于现有技术。

37.在本公开的另一些实施例中,在半导体存储器件的位线的加工工艺中,该形成方法还可以包括如下步骤。

38.请参阅图6,图6为本公开一些实施例中对图5的结构进行介质层填充、第二隔离区设置、第二隔离区回蚀及与介质层相同的材料沉积后形成的结构的剖面示意图。再次实施侧墙制程,通过侧墙制程(spacer)可实现介质层300填充满第二位线槽500内的剩余空间和第一位线槽400内的剩余空间,使第一位线槽400和第二位线槽500均处于填满状态,如图6所示。本公开的一些实施例的下述过程采用ild(层间介质,interlayerdielectric)工艺,具体地,然后在介质层300上方设置第二隔离区900,在本公开的一些实施例中,第二隔离区900的材料为二氧化硅(sio2),通过回蚀第二隔离区900的方式形成暴露出介质层300的多个沟槽,如图6所示,向沟槽内沉积与介质层300相同的材料,沉积后形成的介质层能够与原介质层300处于连通状态,可见位线的高度被明显地降低,从而能够减少位线与存储接触部的对视面积(可理解为位线与存储接触部相对朝向的面积),进而能够极大地降低位线与存储接触部之间的电容值,达到显著地提升半导体存储器件的性能的目的。

39.请参阅图7,图7为利用本公开一些实施例的方法形成具有位线的器件剖面结构示意图。在本公开的一些实施例中,再次通过回蚀第二隔离区900的方式形成暴露出有源区100的多个沟槽,然后再向回蚀的这些沟槽内沉积接触材料,接触材料可以连接至刚暴露的有源区100,以形成多个接触材料区101,在本公开的一些实施例中,接触材料为多晶硅(poly,全称polycrystalline silicon),该形成方法还包括如下步骤,在两次回蚀第二隔离区900的过程中,将第二隔离区900上留下的隔离层(即剩余的第二隔离区900)设置为间隔层102(图6、图7中上述的“横线填充”区域)。本公开提供的位线(位线本体作为位线接触部)的形成方法及结构与常规方案存在实质性的不同,本公开的实施例中提供的位线没有常规位线接触部用的多晶硅,不仅能够减少位线与存储接触部之间的对视面积、降低了位线与存储接触部之间的电容,而且还能够减少传统的位线接触部处多晶硅的加工步骤;而常规的位线需要通过多晶硅与有源区连接、即进行位线接触部的多晶硅加工步骤,请参阅

图8,图8为利用常规加工方法形成具有位线的器件剖面结构示意图。

40.在以上的描述中,对于各层的构图、刻蚀等技术细节并没有做出详细的说明。但是本领域技术人员应当理解,可以通过各种技术手段,来形成所需形状的层、区域等。另外,为了形成同一结构,本领域技术人员还可以设计出与以上描述的方法并不完全相同的方法。另外,尽管在以上分别描述了各实施例,但是这并不意味着各个实施例中的措施不能有利地结合使用。

41.以上对本公开的实施例进行了描述。但是,这些实施例仅仅是为了说明的目的,而并非为了限制本公开的范围。本公开的范围由所附权利要求及其等价物限定。不脱离本公开的范围,本领域技术人员可以做出多种替代和修改,这些替代和修改都应落在本公开的范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。