静态随机存取存储元件

1.本技术是中国发明专利申请(申请号:201710849991.4,申请日:2017年09月20日,发明名称:静态随机存取存储元件)的分案申请。

技术领域

2.本发明涉及集成电路元件的领域,特别是涉及含有鳍式场效晶体管的静态随机存取存储单元。

背景技术:

3.集成电路的功能与效能在过去的四十年间有着爆炸性的成长。在集成电路的演进中,电路的功能密度(即每芯片区域中互连元件的数量)一般会随着图形尺寸(即制作工艺所能制作出的最小部件或是线结构)的缩小而增长。电路尺寸的微缩有益于增加生产效率并降低相关成本,但同时也会增加ic制作以及制作工艺的复杂度。一般的互补式金属氧化物半导体ic元件中会有两种主要的组成部件,亦即晶体管与导线。经由尺寸的微缩,晶体管的效能与密度都能获得改善得以如前述般增进ic的效能与功能性。然而,将晶体管彼此互联的导线(互连结构)却会因尺寸微缩的关系而劣化。因此在现今的ic电路中是导线对于ic的效能、功能性以及功耗有主要的影响。

4.为增进功能密度,半导体装置中常常整合有逻辑电路与内嵌式静态随机存取存储单元(static random

‑

access memory,sram),这类的应用遍及工业与科研用的子系统、车用电子、移动电话、数字相机、以及微处理器等等。sram具有不需刷新即可保存数据的优点,其单元中会含有不同数目的晶体管,通常被称为晶体管数目,如六晶体管(6t)sram、八晶体管(8t)sram等。这些晶体管一般会构成数据栓锁来存储一个位数据。其他的晶体管则可加入来控制该些晶体管的存取。sram单元通常会排列成具有多个行与列的阵列型态。每列sram单元都连接到一字线,其会决定是否选择当前的sram单元。每行sram单元都连接到一位线(或是一对互补的位线),其用来将位数据写入或从sram单元中读取数据。

5.仅靠尺寸微缩的动作已无法满足sram的高密度需求。举例言之,传统平面式晶体管的sram单元结构在半导体尺寸小到一定程度以下会出现效能劣化以及漏电等问题。为了克服此难题,业界提出了鳍式或多鳍式的三维晶体管架构,亦即鳍式场效晶体管(finfets)。鳍式场效晶体管应用在金属氧化物半导体场效晶体管结构中可以有效控制其短通道效应。为了要达到最佳的控制并缩减面积,一般会希望鳍状结构能越薄越好,制作这类超薄型态的鳍状结构的其中一方法就是间隙壁光刻制作工艺,其作法为在心轴(mandrel)图形的侧壁上形成间隙壁,之后将心轴图形移除后该间隙壁就可作为硅基板蚀刻制作工艺中的蚀刻掩模。心轴图形与间隙壁的尺寸将会决定鳍状结构的宽度与节距。对于该些心轴图形与间隙壁的关键尺寸的一致度上的控制是对于内嵌式finfet sram设计的一大挑战。

6.近来在finfet晶体管技术方面的进程已得以制作出高阶的finfet sram单元。然而先进半导体科技中所需要的极小特征尺寸仍然容易诱发装置的漏电问题。举例言之,在

附近有虚置单元或浮栅状态的字线的设计下,sram中的位元单元产生次临界漏电流的问题。此时电流会因为邻近的虚置字线没有完全关闭的缘故从位单元流向虚置单元。为因应现今对于更小型电子装置的需求,如何解决这类半导体漏电流问题变得更重要且迫切。

技术实现要素:

7.本发明的其中一目的在于提出一种静态随机存取存储元件(sram),其在使用虚置图形减轻微负载效应的情况下能更抵抗漏电损,且可在不影响现有的布局设计与制作工艺规划的前提下借着加入对应的虚置图形来进一步改善图形的一致度。

8.为了达到上述目的,本发明的一实施例中提出了一种静态随机存取存储元件,其结构包含一基底、一存储单元位于该基底上,其中该存储单元包含两个作为载入晶体管的p通道栅、两个作为驱动晶体管的n通道栅、以及两个作为存取晶体管的n通道栅、至少一第一虚置栅位于该基底上并邻近其中一该作为存取晶体管的n通道栅,其中该第一虚置栅与该作为存取晶体管的n通道栅跨过一主动(有源)区域、一位线节点位于该第一虚置栅与该作为存取晶体管的n通道栅之间,其中该位线节点电连接至该主动区域、一金属层电连接至该第一虚置栅,其中该第一虚置栅经由该金属层电连接至一接地电压、以及一第二虚置栅位于该基底上并邻近该第一虚置栅,其中该第二虚置栅与其中一该作为载入晶体管的p通道栅以及该作为驱动晶体管的n通道栅以该位线节点为中心对称。

9.本发明的sram元件具有一经由金属线接地而完全关闭的虚置栅极。如此,邻近该虚置栅极的位线不会再因被该虚置栅极拉降(pulldown)而引发次临界漏电流问题,进而避免sram的位线失效的情形发生。

10.无疑地,本发明的这类目的与其他目的在阅者读过下文以多种图示与绘图来描述的优选实施例细节说明后将变得更为显见。

附图说明

11.本说明书含有附图并于文中构成了本说明书的一部分,使阅者对本发明实施例有进一步的了解。该些图示描绘了本发明一些实施例并连同本文描述一起说明了其原理。在该些图示中:

12.图1为一静态随机存取存储单元(sram)的电路图;

13.图2为本发明实施例一静态随机存取存储单元的布局图;

14.图3为本发明实施例一静态随机存取存储单元的布局图,其中包含了层间介电层与第一金属层的布局图形;

15.图4为以图3中截线a

‑

a’所做的截面图;以及

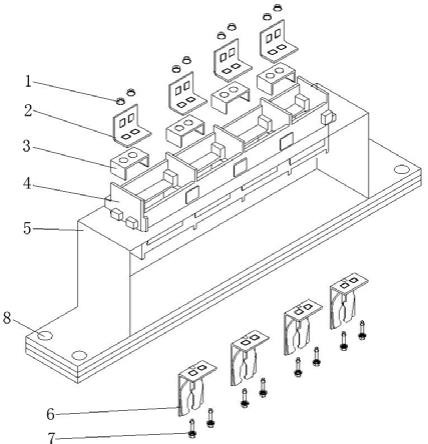

16.图5为一静态随机存取存储单元的布局图,其中包含了主动层(od)的导体图形分布。

17.需注意本说明书中的所有图示都为图例性质,为了清楚与方便图示说明之故,图示中的各部件在尺寸与比例上可能会被夸大或缩小地呈现,一般而言,图中相同的参考符号会用来标示修改后或不同实施例中对应或类似的元件特征。

18.主要元件符号说明

19.100sram单元

20.102,104位线节点

21.110,112数据节点

22.110aod层接触插塞

23.110b栅极接触插塞

24.114,116vdd节点

25.118,120vss节点

26.122栅电极

27.124主动区域

28.126主动区域

29.128栅电极

30.130栅电极

31.132主动区域

32.138,140虚置栅电极

33.141虚置栅电极

34.142虚置位线节点

35.144虚置vdd节点

36.146接载接触插塞

37.150vdd线

38.152,154,156导孔

39.158接载电力线

40.160,162导孔

41.164第一导体图形

42.166第二导体图形

43.200虚置单元

44.bl,blb位线

45.dg虚置栅极晶体管

46.pd

‑

1,pd

‑

2拉降晶体管

47.pg

‑

1,pg

‑

2传送栅晶体管

48.pu

‑

1,pu

‑

2拉升晶体管

具体实施方式

49.下文将要进行本发明实施例的讨论,然而。需了解该些实施例提出了许多可应用的发明概念,在其所述特定的上下文背景中可据以多种广泛的方式来施行体现。这些所讨论的特定实施例为说明之用,并未限定本发明的范畴。

50.根据本发明数种实施范例,其中提出了一种静态随机存取存储单元(sram),实施例中将讨论其多种变体。通篇图示中会用相同的参考符号来标示修改后或不同实施例中对应或类似的元件特征。

51.图1中描绘出根据本发明实施例依sram单元100的电路图。sram单元100含有作为载入晶体管的拉升(pull

‑

up)晶体管pu

‑

1与pu

‑

2,其为p通道金属氧化物半导体(pmos)晶体

管,以及作为存取晶体管的传送栅(pass gate)晶体管pg

‑

1与pg

‑

2以及作为驱动晶体管的拉降(pull

‑

down)晶体管pd

‑

1与pd

‑

2,其为n通道金属氧化物半导体(nmos)晶体管。传送栅晶体管pg

‑

1与pg

‑

2的栅极是由字线wl(未示出)来控制的,其决定该sram单元100是否被选择。拉升晶体管pu

‑

1与pu

‑

2以及拉降晶体管pd

‑

1与pd

‑

2构成了栓锁来存储位,其中位的互补值分别存储在数据节点110与数据节点112中。被存储的位会经由位线bl或blb写入或者是从sram单元100中读取。sram单元100经由具有正电压vdd的供能节点114,116供压。sram单元100也会连接至一供压vss,其可为一接地端。晶体管pu

‑

1与pd

‑

1构成了一第一反向器,晶体管pu

‑

2与pd

‑

2构成了一第二反向器。第一反向器的输入端连接至传送栅晶体管pg

‑

1以及第二反向器的输出端,而输出端连接至传送栅晶体管pg

‑

2以及第二反向器的输入端,形成双栓锁结构。

52.复参照图1,拉升晶体管pu

‑

1与pu

‑

2的源极端会分别连接至vdd节点114与vdd节点116,其复连接至供压(线)vdd。拉降晶体管pd

‑

1与pd

‑

2的源极端则会分别连接至vss节点118与vss节点120,其复连接至供压(线)vss。晶体管pu

‑

2与pd

‑

2的栅极会连接至晶体管pu

‑

1与pd

‑

1的漏极,此连接点称为数据节点112。传送栅晶体管pg

‑

1的源/漏极会连接至位线bl的位线节点102处,传送栅晶体管pg

‑

2的源/漏极会连接至位线blb的位线节点104处。

53.图2绘示出\根据本发明实施范例一sram单元100的布局。在某些实施例中,此布局是以图形数据系统(graphic database system,gds)的格式存在,且其可以有形的非暂态存储媒介如硬盘的方式来体现。此布局可通过计算机来存取并加以处理。再者,通篇说明中所描绘的布局可以透光或不透光图形的形式形成在光刻光掩模上,此光刻光掩模会用于光致抗蚀剂曝光,如此说明中所描绘的特征图形会形成具有实体的特征图形(形状)。故此,本发明揭露中的每个布局也可代表了多个含有所示特征图形的光刻光掩模。

54.在实施例中,为了揭露简明之故,图2并没有完整地表示出sram单元100的所有布局,sram单元100中只有一半的部件,即组成单一反向器的一传送栅晶体管pg

‑

1、一拉降晶体管pd

‑

1以及一拉升晶体管pu

‑

1在图中有绘示出。这些部位应已足够让本领域的一般技术人士了解并据以实施本发明。此外,图中还示有一边缘单元(后文中将称为虚置单元)200邻近sram单元100。在半导体领域中,此虚置单元200通常会设置在sram阵列与周边区域之间,作为一虚置区域来对付微负载效应(micro loading effect)的问题。sram单元100与虚置单元200的外边界会使用虚线来表示,如图中的长方形所示。

55.请参照图2,图中也有示出vdd节点114、vdd节点116、vss节点118、位线节点102与104等部件。栅电极122与下方的主动区域(n型阱区域,可为鳍式)1构成了一拉升晶体管pu

‑

1。栅电极122还与另一下方的主动区域(p型阱区域,可为鳍式)126构成了一拉降晶体管pd

‑

1。栅电极128与下方的主动区域126则构成了一传送栅晶体管pg

‑

1。栅电极130与下方的主动区域(n型阱区域,可为鳍式)132则构成了一拉升晶体管pu

‑

2。根据本发明实施例,晶体管pg

‑

1,pu

‑

1,pu

‑

2以及pd

‑

1可为鳍式场效晶体管(fin field

‑

effect transistors)。

56.如图2所示,数据节点110含有一od层(主动区层)接触插塞110a以及栅极接触插塞110b。od层接触插塞110a的长轴方向为y方向,其与栅电极122,128,130的延伸方向平行。od层接触插塞110a的两端会分别延伸至主动区域124与主动区域(漏极区)126的上方并与之电连接。栅极接触插塞110b有一部分位于栅电极130上方并与之电连接。在实施例中,栅极接触插塞110b的长轴方向为x方向。

57.再者,栅极接触插塞110b会与od层接触插塞110a的一端重叠。故此,当图2的布局在实体的半导体芯片上的sram单元中实作时,栅极接触插塞110b会与od层接触插塞110a结合形成一数据节点110,其可使用相同的金属填充制作工艺来形成一整合连续的数据节点110。图2上半部sram单元100的另一数据节点112具有与数据节点110完全相同的组态,为揭露简明之故,其相关的说明文中不再多予赘述。

58.复参照图2。在sram单元100设置在存储阵列最外围区域的情况下,栅电极128,130或位线节点102与vdd节点116等靠近单元边界的布局图形会受到微负载效应的影响,其会产生不正常的图案而严重影响到存储元件的电性。为了解决此问题,最外围的sram单元100以及周边区域(未示出)之间通常会设置虚置单元,以提供虚置图形来补偿微负载效应。

59.如图2所示,实施例中有数个虚置图形是设置来补偿微负载效应的,其中虚置栅电极138与虚置栅电极140设置在靠近sram单元100的虚置单元200边缘。虚置栅电极138与栅电极128设置成以位线节点102为中心对称,而虚置栅电极140与栅电极130设置成以vdd节点116为中心对称。虚置位线节点142与位线节点102设置成以虚置栅电极138为中心对称,而虚置vdd节点144与vdd节点116设置成以虚置栅电极140为中心对称。需注意虚置栅电极138与栅电极128以及栅电极122一样都跨过同个主动区域126并形成一虚置栅极晶体管dg。再者,在本发明实施例中,虚置栅电极138与虚置栅电极140的更外侧还具有另一虚置栅电极141。虚置栅电极141同样是位于虚置单元100中往y方向延伸,其邻近虚置栅电极138以及虚置栅电极140,之间隔着虚置位线节点142以及虚置vdd节点144等部件。更具体言之,虚置单元200中的虚置栅电极141与sram单元100中拉升晶体管pu

‑

1以及拉降晶体管pd

‑

1所在的栅电极122设置成以边界处的位线节点102以及vdd节点116等部件为中心对称。然而与分段的栅电极122不同的是,虚置栅电极141是一整条连续的直线,其功能与虚置栅电极138以及虚置栅电极140相同,设置来补偿微负载效应。

60.此外,在本发明一实施例中,虚置单元200也可能会提供一区域作为接载(pick

‑

up)区域。虚置位线节点142的附近可设置一接载接触插塞146来经由接载电力线在下层的接载阱区(p型阱)以及接地电压或共同电压vss之间提供电力连接。接载接触插塞146可位于虚置栅电极141相对于虚置位线节点142的另一侧。或者,在其他实施例中,虚置单元200也可能设置在存储阵列之中,而非介于存储阵列和周边区域之间。举例言之,虚置单元可作为两组存储单元之间的间隔单元,来提供接载电力或是补偿虚置图形。

61.图3绘示出根据本发明实施例一sram单元的布局,其中包含了层间介电层(ild)与第一金属层(m1)的布局图形。m1层形成有位线bl与vdd线150,其呈x方向走向穿过sram单元100以及虚置单元200并与主动区域124,126平行。在一连接机制范例中,位线连接至下层的导孔152,其复连接至下层的位线节点102。vdd线150连接至下层的导孔154,156,其复分别连接至下层的vdd节点114与vdd节点116,以提供供压vdd。vdd节点114还会提供供压vdd到主动区域124、数据节点110以及传送栅晶体管pg

‑

1与拉降晶体管pd

‑

1之间的主动区域126。sram中另一由vdd节点116与数据节点112组成的反向器具有相同的运作方式,为了揭露简明之故,其相关说明将不再多予赘述。

62.就现有的连接机制来说,邻近传送栅晶体管pg

‑

1的虚置栅极晶体管dg不会连接任何电压或电力线,而在浮置状态下关闭。然而在此状态下位线节点102与邻近的虚置位线节点142之间仍然容易因为浮置状态下的虚置栅极晶体管dg未完全关闭之故诱发出漏电路

径。在此状态下位线节点102会受到虚置栅极晶体管dg的拉降而导致sram的位线失效问题。

63.为了解决这样的漏电问题,请参照图3,本发明中提出了在虚置单元200的m1层中形成接载电力线158从接载区域延伸至虚置栅电极138处。此接载电力线158与位线bl以及vdd线150相同呈x方向走向而与主动区域124与126平行。在一连接机制范例中,接载电力线158连接至下层的导孔160与162,其复分别连接至下方od层中的接载接触插塞146与虚置栅电极138。由于接载接触插塞146通过其他金属层的电力线与一接地电压或是一共同电压vss连接,与该接载接触插塞146连接的虚置栅电极138也会被电连接至接地电压或共同电压vss,如此,虚置栅极晶体管dg会被接地并完全关闭,不会再有电流从位线节点102端流到虚置位线节点142,因而解决了sram位线失效问题。或者,在其他实施例方面,虚置栅极晶体管dg也可以经由其他金属线接地或接共同电压,并没有限定一定要使用接载电力线158。

64.此外,实施例中还提出一个额外的第一导体图形164设置在od层中的虚置栅电极138上,其中该第一导体图形164与栅电极128上的一常规的第二导体图形166以位线节点102为中心对称。如图4所示,其描绘出一sram单元的布局综览,其中具有od层中的导体图形分布。在实施例中,m0层的图形可包含数据节点110的栅极接触插塞110b、虚置电极上的第一导体图形164以栅电极上的第二导体图形166,其中第一导体图形164与第二导体图形166如同栅极接触插塞110b般作为栅极接触来与其上via_0层的导孔连接。在实施例中,此位于虚置栅电极上的额外第一导体图形164不仅可作为一接触插塞来连接导孔,也有助于补偿m0层的图形,使该层的布局更为均匀一致。再者,位于第一导体图形164更外侧的虚置栅电极141同样具有补偿微负载效应的功能,使得栅电极层的布局更为均匀一致。

65.图5为以图3中截线a

‑

a’所作的截面示意图,其中的层结构都是形成在一半导体基底或是晶片10上。需注意图5仅是示意性地描绘出多层的互连结构与其中的晶体管,其可能未完全反映出sram单元100与虚置单元200中真实的截面态样。图中的互连结构包含一od层(od代表主动区域)、一导孔层via_0、以及一金属层m1,其中m0层包含在od层中。图中的每一层都含有一或多层的介电层或是形成于其中的导体结构特征。位于同层的导体结构特征可能会有彼此齐平的顶面与底面,并且可能同时形成。od层将晶体管的栅电极(如所绘示的晶体管范例dg,pg

‑

1,pd

‑

1以及pu

‑

1等)连接至上方的via_0等层。od层也会将晶体管的源/漏极区与接载阱区等区域连接至上方的via_0等层。

66.从图5中可以看出,接载接触插塞146会与基底10上的接载阱区106接触,复经由导孔160连接至上方的接载电力线158。此接载电力线158会通过其他金属层的电力线与一接地电压或是一共同电压vss连接,达成其接载(pick

‑

up)功效。接载电力线158复会延伸至虚置栅电极138上方,并经由导孔162与第一导体图形164来与之电连接,以提供接地电压或是共同电压vss到虚置栅极晶体管dg。如此,虚置栅极晶体管dg会被接地并完全关闭,不会再有电流从位线节点经由主动区流到虚置位线节点处。

67.在实施例中,位线与带有vss供压的vss线(未示出)可设置在m2层并呈现与位线bl与vdd线150垂直的y方向走向。在一连接机制范例中,位线经由导孔连接至下方od层中的传送栅晶体管pg

‑

1与pg

‑

2,vss线则连接至下方od层中的导孔,其复连接至主动区域126部位,该主动区域部位可作为图2中拉降晶体管pd

‑

1的源极。由于本发明中字线与vss线的布局与连接为半导体领域的现有技术,为了揭露简明之故,其相关的组态与图示文中将不再多予赘述,避免模糊了本发明的重点。

68.根据上述揭露,本发明提出了一种静态随机存取存储元件,其在使用虚置图形减轻微负载效应的情况下能更抵抗漏电损,且可在不影响现有的布局设计与制作工艺规划的前提下借着在m0层加入对应的虚置图形以及接触图形来进一步改善图形的一致度。

69.以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。