1.本发明涉及自动控制与测量技术领域,具体地,涉及一种用于感应同步器输出端的前置放大电路及感应同步器。

背景技术:

2.随着航天器的寿命的越来越长以及航天器上活动部件的增多和精度的提高,对测角元件的精度和可靠性也越来越高,以圆光栅、编码器为代表的测角部件由于其难以保证在轨长寿命和高可靠性,在部分应用中,已经逐渐被感应同步器所替代。

3.感应同步器的后处理模块一般采用analog device公司的专用芯片实现。但是感应同步器的输出信号非常微弱,一般峰峰值不超过5mv,而专用芯片或者数字电路一般需要其输入端信号的峰峰值为5v,所以需要对输出信号进行有效的放大。同时,由于放大过程中不可避免的会造成信号相移,感应同步器的工作原理决定其两输出端和参考信号需要满足一定的相位关系,所以前处理电路还需要进行移相。前处理电路一般采用两低通和移相电路串联构成,但是采用此种方法时,感应同步器的驱动能力很弱,很容易受到地平面上噪声的干扰,同时为了实现较大的放大倍数,需要多级低通滤波器进行串联,对于一些低频的干扰也无法进行有效地滤除。

4.公开号为cn110864620a的专利文献公开了一种用于提高感应同步器信号信噪比的装置,涉及感应同步器测角领域,该装置包括前级放大电路,所述前级放大电路包括信号输入端子in1、信号输入端子in2、高精度匹配管u1、三极管q和二极管d,所述信号输入端子in1和信号输入端子in2与感应同步器的输出绕组连接,电阻r3、r4与电位器rp1串联组成零位调节电路,三极管q、二极管d、电阻r5、电阻r6、电阻r7组成恒流源电路。但是该专利文献仍然存在对干扰过滤效果不佳的缺陷。

技术实现要素:

5.针对现有技术中的缺陷,本发明的目的是提供一种用于感应同步器输出端的前置放大电路及感应同步器。

6.根据本发明提供的一种用于感应同步器输出端的前置放大电路,包括差分放大电路、低通滤波电路、带通放大电路及全通移相电路;

7.所述差分放大电路的输入端用于接收信号,所述差分放大电路的输出端与所述低通滤波电路的输入端连接;

8.所述低通滤波电路的输出端与所述带通放大电路的输入端连接;

9.所述带通放大电路的输出端与所述全通移相电路的输入端连接,所述全通移相电路的输出端用于输出信号;

10.所述差分放大电路用于将原有的感应同步器差分信号转换为单端信号;所述低通滤波电路用于进一步放大所述差分放大器输出的信号;所述带通放大电路用于滤除高频噪声和低频分量;所述全通移相电路用于调节放大后电路的输出相位。

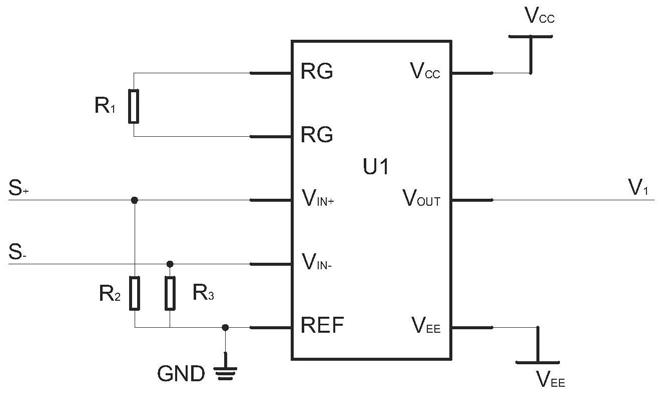

11.优选的,所述差分放大电路包括第一放大器u1、第一电阻r1、第二电阻r2及第三电阻r3;

12.所述第一电阻r1的两端分别连接在所述第一放大器u1的rg引脚上;

13.所述第二电阻r2的一端连接在所述第一放大器u1的v

in

引脚上并作为所述第一放大器u1的第一输入端;所述第二电阻r2的另一端分别连接所述第一放大器u1的ref引脚和所述第三电阻r3的一端并接地;

14.所述第三电阻r3的另一端连接所述第一放大器u1的v

in

‑

引脚并作为所述第一放大器u1的第二输入端;

15.所述第一放大器u1的v

out

引脚作为所述第一放大器u1的输出端。

16.优选的,所述低通滤波电路包括第二放大器u2、第四电阻r4、第五电阻r5、第一电容c1及第二电容c2;

17.所述第四电阻r4的一端作为所述低通滤波电路的输入端,所述第四电阻r4的另一端分别连接所述第二放大器u2的正相输入端、所述第一电容c1的一端及所述第五电阻r5的一端;

18.所述第一电容c1的另一端接地;所述第五电阻r5的另一端连接所述第二电容c2的一端;所述第二电容c2的另一端分别连接所述第二放大器u2的输出端和所述第二放大器u2的负相输入端并作为所述低通滤波电路的输出端。

19.优选的,所述带通放大电路包括第三放大器u3、第六电阻r6、第七电阻r7、第八电阻r8、第三电容c3及第四电容c4;

20.所述第六电阻r6的一端作为所述带通放大电路的输入端,所述第六电阻r6的另一端分别连接所述第三电容c3的一端、所述第四电容c4的一端、所述第七电阻r7的一端;

21.所述第三电容c3的另一端分别连接所述第八电阻r8的一端和所述第三放大器u3的输出端并作为所述带通放大电路的输出端;

22.所述第四电容c4的另一端分别连接所述第八电阻r8的另一端和所述第三放大器u3的负相输入端;

23.所述第七电阻r7的另一端连接所述第三放大器u3的正相输入端并接地。

24.优选的,所述全通移相电路包括第四放大器u4、第九电阻r9、第十电阻r10、第十一电阻r11及第五电容c5;

25.所述第九电阻r9的一端连接所述第五电容c5的一端并作为全通移相电路的输入端,所述第九电阻r9的另一端分别连接所述第十电阻r10的一端和所述第四放大器u4的负相输入端;

26.所述第十电阻r10的另一端连接所述第四放大器u4的输出端并作为所述全通移相电路的输出端;

27.所述第五电容c5的另一端分别连接所述第四放大器u4的正相输入端和所述第十一电阻r11的一端;

28.所述第十一电阻r11的另一端接地。

29.优选的,所述差分放大电路的放大倍数不小于100。

30.优选的,所述低通滤波电路通带内的放大倍数不小于10。

31.优选的,所述带通放大电路通带内的放大倍数不大于3。

32.优选的,所述全通移相电路的放大倍数为1,所述全通移相电路的移相方式为调节电容的容量。

33.本发明还提供一种感应同步器,包括上述的用于感应同步器输出端的前置放大电路。

34.与现有技术相比,本发明具有如下的有益效果:

35.1、本发明通过差分放大电路将原有的感应同步器输出的差分信号转换为单端信号,提高系统的驱动能力和抗干扰能力,确保了后续的滤波电路的正常工作,满足感应同步器输出特性;

36.2、本发明通过带通滤波器进一步滤除高频噪声和低频分量,提高信噪比;

37.3、本发明通过全通移相电路调节放大后电路的输出相位,使其满足后端解调电路和精度的要求。

附图说明

38.通过阅读参照以下附图对非限制性实施例所作的详细描述,本发明的其它特征、目的和优点将会变得更明显:

39.图1为本发明的用于感应同步器输出端的前置放大电路的结构框图;

40.图2为本发明的差分放大电路的连接图;

41.图3为本发明的低通滤波电路的原理图;

42.图4为本发明的带通放大电路的原理图;

43.图5为本发明的全通移相电路的原理图。

具体实施方式

44.下面结合具体实施例对本发明进行详细说明。以下实施例将有助于本领域的技术人员进一步理解本发明,但不以任何形式限制本发明。应当指出的是,对本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变化和改进。这些都属于本发明的保护范围。

45.如图1~5所示,本发明提供的一种用于感应同步器输出端的前置放大电路,包括差分放大电路、低通滤波电路、带通放大电路及全通移相电路,差分放大电路的输入端用于接收信号,差分放大电路的输出端与低通滤波电路的输入端连接,低通滤波电路的输出端与带通放大电路的输入端连接,带通放大电路的输出端与全通移相电路的输入端连接,全通移相电路的输出端用于输出信号,差分放大电路用于将原有的感应同步器差分信号转换为单端信号,低通滤波电路用于进一步放大差分放大器输出的信号,带通放大电路用于滤除高频噪声和低频分量,全通移相电路用于调节放大后电路的输出相位。

46.差分放大电路的放大倍数不小于100。低通滤波电路通带内的放大倍数不小于10。带通放大电路通带内的放大倍数不大于3。全通移相电路的放大倍数为1,全通移相电路的移相方式为调节电容的容量。

47.差分放大电路包括第一放大器u1、第一电阻r1、第二电阻r2及第三电阻r3,第一电阻r1的两端分别连接在第一放大器u1的rg引脚上,第二电阻r2的一端连接在第一放大器u1的v

in

引脚上并作为第一放大器u1的第一输入端,第二电阻r2的另一端分别连接第一放大

器u1的ref引脚和第三电阻r3的一端并接地,第三电阻r3的另一端连接第一放大器u1的v

in

‑

引脚并作为第一放大器u1的第二输入端,第一放大器u1的v

out

引脚作为第一放大器u1的输出端。

48.低通滤波电路包括第二放大器u2、第四电阻r4、第五电阻r5、第一电容c1及第二电容c2,第四电阻r4的一端作为低通滤波电路的输入端,第四电阻r4的另一端分别连接第二放大器u2的正相输入端、第一电容c1的一端及第五电阻r5的一端,第一电容c1的另一端接地;第五电阻r5的另一端连接第二电容c2的一端,第二电容c2的另一端分别连接第二放大器u2的输出端和第二放大器u2的负相输入端并作为低通滤波电路的输出端。

49.带通放大电路包括第三放大器u3、第六电阻r6、第七电阻r7、第八电阻r8、第三电容c3及第四电容c4,第六电阻r6的一端作为带通放大电路的输入端,第六电阻r6的另一端分别连接第三电容c3的一端、第四电容c4的一端、第七电阻r7的一端,第三电容c3的另一端分别连接第八电阻r8的一端和第三放大器u3的输出端并作为带通放大电路的输出端,第四电容c4的另一端分别连接第八电阻r8的另一端和第三放大器u3的负相输入端,第七电阻r7的另一端连接第三放大器u3的正相输入端并接地。

50.全通移相电路包括第四放大器u4、第九电阻r9、第十电阻r10、第十一电阻r11及第五电容c5,第九电阻r9的一端连接第五电容c5的一端并作为全通移相电路的输入端,第九电阻r9的另一端分别连接第十电阻r10的一端和第四放大器u4的负相输入端,第十电阻r10的另一端连接第四放大器u4的输出端并作为全通移相电路的输出端,第五电容c5的另一端分别连接第四放大器u4的正相输入端和第十一电阻r11的一端,第十一电阻r11的另一端接地。

51.差分放大电路将原有的感应同步器差分信号转换为单端信号,提高系统的驱动能力和抗干扰能力,确保了后续的滤波电路的正常工作,满足感应同步器输出特性。差分放大电路后端接入低通滤波电路,进一步提高放大倍数。低通滤波电路后端接入带通放大电路,进一步滤除高频噪声和低频分量,提高信噪比。带通放大电路后端接入一个全通移相电路,通过调节可调电容的容值,调节放大后电路的输出相位,使其满足后端解调电路和精度的要求。

52.图1中差分放大电路、低通滤波电路、带通放大电路及全通移相电路串联实现。

53.图2中为差分放大电路,其中u1建议为仪用放大器,s

、s

_

分别为差分输入端的电压,也就是感应同步器的输出端的电压,v1为输出端的电压,其输入输出满足:

[0054][0055]

r0为一个和u1型号相关的系数,其中r1具体的大小后续根据系统的综合放大倍数确定,的值不小于100,以提高输入端的信噪比。

[0056]

图3为低通滤波器,v1为其输入端的电压,v2为输出端的电压,其输出输入满足:

[0057][0058]

其中,s标示laplace变换中的s,放大倍数不小于10。

[0059]

图4为带通滤波器,v2为其输入端的电压,v3为输出端的电压,其输出输入满足:

[0060][0061]

设计放大倍数为1。

[0062]

图5为全通移相电路,v3为其输入端的电压,v4为输出端的电压,其输出输入满足:

[0063][0064]

r9=r

10

,所以可变为:

[0065][0066]

低通滤波电路完成电路板粘贴后,将输出端和参考信号(由感应同步器的励磁信号给出)联接到示波器上,调节c4,使感应同步器的每一路输出端的相位满足和参考信号的关系,同时满足感应同步器两路输出端之间的相位关系。在相位满足要求后,调节差分放大电路的r1,使输出端的幅值满足后端专用芯片的要求。

[0067]

本发明还提供一种感应同步器,包括上述的用于感应同步器输出端的前置放大电路。

[0068]

本发明通过差分放大电路将原有的感应同步器输出的差分信号转换为单端信号,提高系统的驱动能力和抗干扰能力,确保了后续的滤波电路的正常工作,满足感应同步器输出特性。

[0069]

以上对本发明的具体实施例进行了描述。需要理解的是,本发明并不局限于上述特定实施方式,本领域技术人员可以在权利要求的范围内做出各种变化或修改,这并不影响本发明的实质内容。在不冲突的情况下,本技术的实施例和实施例中的特征可以任意相互组合。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。