1.本发明涉及集成光电子器件和半导体材料技术领域,更具体地,涉及一种在硅上制作垂直腔面发射激光器阵列的方法。

背景技术:

2.垂直腔面发射激光器(vcsel)具有结构紧凑、大的直接调制带宽、容易制成阵列、容易与光纤耦合等特点,在短距离光通信中有重要应用。在当今的大数据时代,数据中心内部需要传输海量数据,以vcsel为核心的光发射模块或线缆在数据中心中获得了广泛的应用。近些年来,vcsel的应用进一步扩展到人脸识别、3d传感、自动驾驶等领域,其应用市场迅速扩大。vcsel的另一个重要的潜在应用是与硅芯片集成起来,一方面与硅基控制模块集成,以实现集成的传感或通信芯片;另一方面是与硅光芯片集成,将vcsel作为硅光芯片的光源。但由于短波长(发射波长1000nm以下)的vcsel多数都是在砷化镓衬底上外延生长的,将其与硅基控制电路或硅光芯片直接集成存在几个尚未完全解决的科学和技术难题:

3.在硅上直接外延生长砷化镓基vcsel非常困难。硅与砷化镓的材料性质不同,存在晶格、极性和热膨胀系数失配,这会导致在硅上直接外延生长的砷化镓单晶薄膜中出现大量的材料缺陷,如失配/穿透位错、反相畴、层错等,以及由热膨胀系数失配导致的晶圆翘曲和薄膜开裂。这些材料缺陷使vcsel的性能、可靠性和寿命急剧恶化,使其失去实用价值。其中穿透位错是影响激光器性能和可靠性的一种重要缺陷,其密度(threading dislocation density,tdd)是衡量硅上异质外延生长砷化镓等三五族半导体缺陷水平的一个主要指标。当前在硅上外延生长砷化镓所能获得的最低的tdd在大约106cm

‑2,而这对制造高性能、长寿命的激光器来说仍然太高。

4.利用晶圆键合或器件倒装键合的方式将在砷化镓衬底上制作的vcsel转移到硅上可以获得质量较好的器件,但这些方式自身受到一些限制,例如晶圆级集成和制造,比如当前vcsel主要制作在直径6英寸的砷化镓晶圆上,但直径6英寸的硅晶圆产线已比较稀少,直接进行晶圆级集成不方便,且这些方法的可靠性也有待检验。因此这些技术尚不成熟。

5.公开号为cn109449760a中国发明专利。于20公开了一种垂直腔面发射激光器阵列模块与显示装置,垂直腔面发射激光器阵列模块包括有源矩阵显示控制电路衬底;第一分布式布拉格反射光栅形成反射镜阵列;半导体发光量子层阵列;限制电流分布的光圈孔径阵列;以及第二分布式布拉格反射光栅形成反射镜阵列;其中,所述有源矩阵显示控制电路衬底中的有源矩阵显示控制电路通过金属电极阵列驱动半导体发光量子层阵列发光。该方案虽然也涉及垂直腔面的发射激光器,但其没有解决在硅衬底上外延生长的砷化镓基vcsel中缺陷密度较高,难以获得良好性能的vcsel的问题。

技术实现要素:

6.本发明为克服上述现有技术中在硅衬底上外延生长的砷化镓基vcsel中缺陷密度较高,难以获得良好性能的vcsel的缺陷,提供一种在硅上制作垂直腔面发射激光器阵列的

方法。

7.本发明的首要目的是为解决上述技术问题,本发明的技术方案如下:

8.一种在硅上制作垂直腔面发射激光器阵列的方法,包括以下步骤:

9.s1:用化学气相沉积法在硅(001)晶圆上外延生长一层锗缓冲层;

10.s2:利用金属有机物化学气相沉积或分子束外延设备或其他的三五族半导体外延生长设备,在所述锗缓冲层上外延生长一层掺杂的砷化镓缓冲层,用作vcsel的下电极;

11.s3:利用化学气相沉积法在砷化镓缓冲层上沉积一层二氧化硅或氮化硅薄膜;

12.s4:利用曝光和刻蚀方法,在所述二氧化硅或氮化硅薄膜中制作vcsel外延生长的掩膜图案;

13.s5:利用金属有机物化学气相沉积或分子束外延设备或其他的三五族半导体外延生长设备,在掩膜图案上外延生长vcsel的整体外延结构;

14.s6:在生长出的vcsel的整体外延结构上利用通常的vcsel制作工艺完成vcsel的制作,其中vcsel的底部电极可由最初外延生长的砷化镓缓冲层充当。

15.进一步地,所述锗缓冲层不超过1微米。

16.进一步地,所述掩膜图案的开口尺寸与vcsel相同,掩膜的开口中暴露出来砷化镓缓冲层表面。

17.进一步地,所述的硅(001)晶圆应具有一定的晶向斜切角度,使其表面具有双原子台阶;或经过表面热处理后可以形成双原子台阶,并将双原子台阶特征继续传递到锗缓冲层的表面,进而能够在外延生长砷化镓缓冲层时抑制反相畴的形成。

18.进一步地,所述的锗缓冲层能缓解晶格失配,多数的位错缺陷都局域在锗缓冲层与硅衬底的界面处,其表面的穿透位错密度不高于1

×

107cm

‑2。

19.进一步地,所述的砷化镓缓冲层与锗缓冲层晶格失配小于0.1%,其中的穿透位错密度不高于锗缓冲层,且没有反相畴、层错晶格缺陷。

20.进一步地,砷化镓缓冲层应为n型或p型掺杂,使其可以充当vcsel的电极接触层。

21.进一步地,用步骤s3和s4制作的二氧化硅或氮化硅掩膜图案的尺寸与将要制作的vcsel器件尺寸一致,其尺寸的取值范围为1微米至100微米。

22.进一步地,掩膜图案的排布亦与vcsel阵列一致。

23.进一步地,步骤s5中外延生长vcsel的整体外延结构包括上下两个布拉格反射镜和vcsel的量子阱有源区以及电极接触层,与通用的vcsel外延结构相同;

24.要制作的vcsel将在二氧化硅或氮化硅掩膜图案的开孔部位,即暴露出的砷化镓表面外延生长,vcsel的三维形状将由掩膜图案定义并实现,其中vcsel的底部电极可由最初外延生长的砷化镓缓冲层充当。

25.与现有技术相比,本发明技术方案的有益效果是:

26.本发明在硅衬底上外延生长缓冲层之后,利用氮化硅或二氧化硅介质薄膜作为掩膜,用来定义后续外延生长的vcsel的尺寸和形状,以及缓解大面积薄膜外延时由热膨胀系数失配导致的薄膜开裂和晶圆翘曲,从而制造出器件尺寸较小的vcsel阵列,减小单个vcsel中位错缺陷的数量或避开位错缺陷的影响,并通过进一步优化vcsel的尺寸和阵列排布方式,以提高阵列器件的完好率,最终提高硅衬底上外延生长的vcsel的性能和可靠性。

附图说明

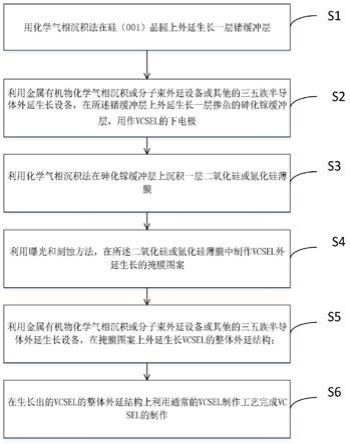

27.图1为本发明方法流程图。

28.图2为本发明实施例制备的vcsel结构的示意图。

29.图3为本发明实施例制备的vcsel阵列示意图。

具体实施方式

30.为了能够更清楚地理解本发明的上述目的、特征和优点,下面结合附图和具体实施方式对本发明进行进一步的详细描述。需要说明的是,在不冲突的情况下,本技术的实施例及实施例中的特征可以相互组合。

31.在下面的描述中阐述了很多具体细节以便于充分理解本发明,但是,本发明还可以采用其他不同于在此描述的其他方式来实施,因此,本发明的保护范围并不受下面公开的具体实施例的限制。

32.实施例1

33.如图1所示,一种在硅上制作垂直腔面发射激光器阵列的方法,包括以下步骤:

34.s1:用化学气相沉积法在(001)晶向的硅晶圆上外延生长一层锗缓冲层;

35.在本发明中,所述锗缓冲层厚度不超过1微米,锗缓冲层能缓解晶格失配,多数的位错缺陷都局域在锗缓冲层与硅衬底的界面处,其表面的穿透位错密度不高于1

×

107cm

‑2。

36.需要说明的是,所述的硅(001)晶圆应具有一定的晶向斜切角度,使其表面具有双原子台阶;或虽然没有特定的晶向斜切,但经过表面热处理后可以形成双原子台阶,并将双原子台阶特征继续传递到锗缓冲层的表面,进而能够在外延生长砷化镓缓冲层时抑制反相畴的形成。

37.s2:利用金属有机物化学气相沉积(mocvd)或分子束外延设备(mbe)或其他的三五族半导体外延生长设备,在所述锗缓冲层上外延生长一层掺杂的砷化镓缓冲层,用作vcsel的下电极;

38.需要说明的是,所述的砷化镓缓冲层与锗缓冲层晶格失配小于0.1%,其中的穿透位错密度不高于锗缓冲层,且没有反相畴、层错晶格缺陷。且砷化镓缓冲层应为n型或p型掺杂,使其可以充当vcsel的电极接触层。

39.s3:利用化学气相沉积法在砷化镓缓冲层上沉积一层二氧化硅或氮化硅薄膜;

40.s4:利用曝光和刻蚀方法,在所述二氧化硅或氮化硅薄膜中制作vcsel外延生长的掩膜图案;所述掩膜图案的开口尺寸与vcsel相同,掩膜的开口中暴露出来砷化镓缓冲层表面。

41.需要说明的是,用步骤s3和s4制作的二氧化硅或氮化硅掩膜图案的尺寸与将要制作的vcsel器件尺寸一致,其尺寸的取值范围为1微米至100微米。

42.s5:利用金属有机物化学气相沉积(mocvd)或分子束外延设备(mbe)或其他的三五族半导体外延生长设备,在掩膜图案上外延生长vcsel的整体外延结构,包括上下两个布拉格反射镜(dbr)和vcsel的量子阱有源区以及电极接触层;与通用的vcsel外延结构相同;

43.需要说明的是,要制作的vcsel将在二氧化硅或氮化硅掩膜图案的开孔部位,即暴露出的砷化镓表面外延生长,vcsel的三维形状将由掩膜图案定义并实现。

44.如图2所示为制备的vcsel结构的示意图。

45.s6:在生长出的vcsel的整体外延结构上利用通常的vcsel制作工艺完成vcsel的制作,其中vcsel的底部电极可由最初外延生长的砷化镓缓冲层充当。图3为本发明实施例制备的vcsel阵列示意图。

46.本发明充分利用vcsel较小的器件面积,在穿透位错密度约106cm

‑2~107cm

‑2时,通过合理设计器件尺寸、阵列排布和制作方式,尽量规避位错缺陷的不利影响,实现较高性能的硅基vcsel激光器。

47.本发明与选择性外延生长方式虽然形式相似,但物理原理完全不同。选择性外延生长利用掩膜图案的深宽比由介质掩膜图形的侧壁阻挡异质外延生长时三五族半导体中所产生的位错、层错等晶格缺陷,从而获得较高质量的三五族半导体。该方法中的介质掩膜图案的深宽比必须满足一定的要求,例如不小于2:1,否则介质掩膜将无法有效阻挡晶格缺陷的生长和传播。而本方明所涉及的二氧化硅或氮化硅掩膜图案的具体尺寸和形状并不符合选择性外延生长的要求,起不到阻挡晶格缺陷传播的作用,其主要作用是:1.用来定义vcsel的形状;2.缓解大面积薄膜外延时由热膨胀系数失配导致的薄膜开裂和晶圆翘曲。

48.附图中描述位置关系的用语仅用于示例性说明,不能理解为对本专利的限制;

49.显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明权利要求的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。