1.在非易失性存储器(nvm)的引导操作期间,修整和配置位被提供给片上系统(soc)的组件,包括向soc的组件提供稳定电流的参考电流块。

背景技术:

2.nvm可以用差分读取或单端读取来读取。为了执行差分读取,其中每个字节都被存储在称为直接单元和互补单元的两个物理单元中。相同的字节在直接单元中被存储为逻辑1,并且在互补单元中被存储为逻辑0,反之亦然。

3.当读取操作是对单元执行时,使用感测放大器比较来自直接单元及其互补单元的电流。感测放大器的输出是高或低。在一些情况下,高感测放大器输出将指示擦除单元已经被读取,并且低感测放大器输出将指示编码单元已经被读取。在其他情况下,高感测放大器输出将指示编程单元已经被读取,并且低感测放大器输出将指示擦除单元已经被读取。

4.在引导操作时,差分读取消除了对来自带隙或电流参考块的参考电流的可用性的依赖性。存在nvm阵列,该nvm阵列包括用于差分读取的单元和用于单端读取的单元。

技术实现要素:

5.初级存储器阵列包括多个可配置行,该多个可配置行分别具有多个存储器单元。存储器单元具有两种类型,包括用户存储器单元和测试存储器单元。用户存储器单元包括要被存储在存储器中的信息或数据。测试存储器单元是在启动时或在引导操作中要使用的配置或修整位。测试存储器单元具有两种类型,包括测试数据存储器单元和互补测试数据存储器单元。

6.本公开的可配置行可以被配置为用户存储器单元或测试存储器单元。每个存储器单元都可以被配置为测试存储器单元或用户存储器单元。例如,单行可以包括用户存储器单元和测试存储器单元。在第一配置中,行的第一单元可以被用作用户存储器单元。在第二配置中,行的第一单元可以被用作测试存储器单元。

7.初级存储器阵列包括由存储器单元组成的多列。初级存储器阵列包括多个字线,使得每个可配置行都被耦合至字线。初级存储器阵列还具有多个位线,使得位线被耦合至每列。列复用器被耦合至多个位线。列复用器包括第一多个晶体管,其中每个晶体管都被耦合至多个位线中的一个位线。存在至少两行第一多个晶体管。在一些实施例中,每行第一多个晶体管均包括两组晶体管。

8.列复用器还具有多个组选择晶体管,其中每个组选择晶体管被耦合至第一多个晶体管的两组晶体管之一。列复用器还具有两种类型的模式选择晶体管。一种类型的模式选择晶体管(第一模式选择晶体管)被耦合至反相器和另一类型,包括多个第二模式选择晶体管。第二模式选择晶体管中的每个第二模式选择晶体管被耦合至组选择晶体管组中的一个组选择晶体管。感测放大器被耦合至列复用器,该列复用器包括运算放大器以及耦合至运算放大器的两个电流到电压转换器。模式选择晶体管被耦合至电流到电压转换器。参考电

流晶体管开关通过反相器被耦合至第一模式选择晶体管。参考电流晶体管开关的源极被耦合至参考存储器单元阵列,该参考存储器单元阵列可以被用于向初级存储器阵列提供参考电流以进行单端读取操作。

9.在引导操作期间,在不存在来自带隙或电流参考块的稳定参考电流的情况下,nvm读取操作是不可靠的。同时,由于可靠的修整和配置位无法从nvm获得,因此带隙或电流参考块无法向nvm初级阵列提供稳定电流。因此,这些修整和配置位被存储在测试存储器单元中,以在引导操作期间以差分方式被读取。

10.在一个实施例中,参考电流还可以使用参考存储器单元阵列代替带隙或参考电流生成器来生成。参考存储器单元阵列包括一个或多个存储器单元,该一个或多个存储器单元是在与初级存储器阵列的存储器单元相同的过程中形成的。因此,对参考存储器单元阵列的过程和温度变化的响应类似于初级存储器单元阵列,这导致单端读取操作的更佳准确性。通过选择多个存储器单元来生成参考电流,从参考存储器单元阵列获得的参考电流的准确性是可调整的。该参考电流是基于参考电流阵列中的所有所选存储器单元的平均值来生成的。通过选择更多数量的存储器单元来生成参考电流,提高了参考电流的准确性,其是所有所选单元的平均值。

11.初级存储器阵列可以具有被布置为两行或多行字的多个存储器单元,使得每行中的单元是测试存储器单元和用户存储器单元。测试存储器单元具有两种类型:数据存储器单元及其互补(称为互补数据存储器单元)。数据存储器单元中的数据也被存储在其互补数据存储器单元中以进行差分读取操作。在本公开中,每行可以包含数据存储器单元、关联的互补数据存储器单元和用户存储器单元,使得该行可以具有单端读取部分和差分读取部分。在一种布置中,第一组用户存储器单元通过同一行的数据和互补数据存储器单元与单行的第二组用户存储器单元间隔开。备选地,每行还可以被配置为使得数据存储器单元和互补数据存储器单元通过用户存储器单元彼此间隔开。在该实施例中,每行可以以用户数据存储器单元、数据存储器单元和互补数据单元的各种定向来配置,以提供使用的灵活性。当用户基于存储器阵列的使用的参数存储数据时,这可以被调整。这允许最优地使用主存储器阵列的区域。

12.在另一实施例中,初级存储器阵列可以具有被布置为字的两个或更多个连续行的存储器单元,其中存储器单元在一行中的放置与存储器单元在另一行中的放置相同。在使用期间,代替从要被读取的单个存储器单元获得电流,平均电流是通过从两个或更多个连续行中选择相同单元来获取的。与读取单个单元相比,两个或更多个相同的存储器单元的平均电流允许更准确地读取存储器单元。

13.在差分读取被实施的另一实施例中,存储器阵列的存储器单元的多于一行可以被配置,使得数据存储器单元在一行中,并且关联的互补数据存储器单元在另一行中。该行可以彼此物理地相邻,或者这些行可以通过存储器阵列的其他行分开。通过提供对数据黑客的免疫力,这种布置允许读取操作更安全。

附图说明

14.图1是片上系统的组件的框图;

15.图2是用于差分和单端读取的存储器单元和电路组件的阵列;

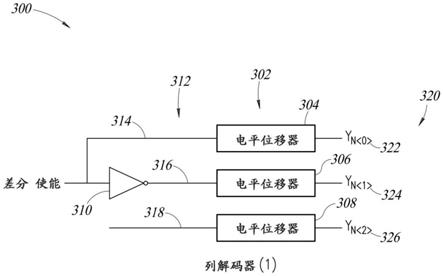

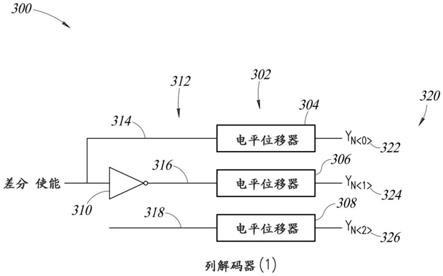

16.图3和4a是根据本技术的实施例的列解码器;

17.图4b是图4a的列解码器的真值表;

18.图5和6是图2的存储器单元的阵列,图示了差分读取和单端读取的示例;

19.图7是字线,该字线包括具有单端和差分读取单元的多个存储器单元;

20.图8是多个连续字线,分别具有多个存储器单元和电路组件,以生成更可靠的读取信息;

21.图9是多个连续字线,在本公开的替代实施例中,分别具有用于数据加密和数据安全性相关应用的多个存储器单元和电路组件;并且

22.图10是图2的参考电流生成器的增强视图。

具体实施方式

23.图1是片上系统(soc)100的组件的框图,该片上系统100包括耦合至数据总线108的非易失性存储器(nvm)阵列102。nvm阵列102包括用户存储器区段112、引导代码区段114和修整数据区段116。用户存储器区段112存储与用户对存储器的使用相关联的数据。引导代码区段114包括与存储器阵列的启动相关联的数据。修整数据区段116包括校准信息,该校准信息可以在存储器阵列的启动期间与引导代码区段114数据一起使用。

24.nvm阵列102通过总线108被耦合至系统随机存取存储器(ram)118。系统ram 118在soc 100的操作期间结合nvm阵列102使用。用户存储器112是非易失性存储器,在sco 100启动时,数据从该非易失性存储器被复制到系统ram 118(是易失性存储器)上。数据从用户存储器112被复制到系统ram 118中,以实现与微控制器106的高频通信。当soc 100被关闭时,来自系统ram 118的数据被擦除。相反,即使在soc 100关闭之后,用户存储器112中的数据也被保留。

25.输入/输出(i/o)控制器126被耦合至总线108,以用于控制和监测进入和离开soc 100的数据。微控制器106也在soc 100上,并且被耦合至总线108。附加的数字逻辑可以被包括在soc 100中,作为胶合逻辑120。soc 100的数模转换器和模数转换器(adc dac)块122从nvm阵列102的修整数据块116接收修整位,以用于校准。振荡器块124(用电连接110被耦合至nvm阵列102)被用于生成时针,该时针从nvm阵列102的引导代码块114接收配置位。带隙电流参考块104被耦合至nvm阵列102,其在soc 100启动之后向nvm阵列102的用户存储器112提供参考电流。

26.在soc 100引导或启动操作期间,在不存在来自带隙电流参考块104的稳定参考电流的情况下,nvm阵列102读取操作是不可靠的。同时,带隙电流参考块104无法向nvm阵列102提供稳定参考电流,因为无法从nvm阵列102获得可靠的修整和配置位。就此而言,这些修整和配置位被存储在测试或启动参数存储器单元中,以在引导操作期间以差分方式被读取。

27.图2是用于差分和单端读取的存储器单元和电路组件的阵列200。存储器阵列200包括耦合至位线或列复用器220的初级存储器单元阵列201,该复用器被耦合至感测放大器232。初级存储器单元阵列201包括多个存储器扇区203,存储器扇区分别包括多个存储器单元行202。多个存储器单元行202的每行包括多个存储器单元206。在该实施例中,多个存储器扇区203的每个存储器扇区具有两个存储器单元行,即,第一存储器单元行244和第二存

储器单元行246。在其他实施例中,每个存储器扇区203可以具有多于两个存储器单元行。

28.多个存储器单元行202中的每个存储器单元行包括多个存储器单元206中的偶数数目的存储器单元。偶数数目的存储器单元206被划分为两组,即,第一组205和第二组207。第一组205和第二组207被耦合至列复用器220,该列复用器的操作在下面被更详细地描述。

29.多个存储器单元行202可以被配置为多个用户存储器单元行212(参见扇区<0>和扇区<1>)或者多个测试存储器单元行214(参见扇区<n>)。用户存储器单元行212的存储器单元206可以被配置为数据存储元件,以存储针对除了soc引导操作之外的所有活动的数据。测试存储器单元行214的存储器单元206可以被配置为测试存储器单元,其中数据被存储用于soc引导操作的目的,该数据被配置用于不依赖于参考电流的差分读取。测试存储器单元具有两种类型,即,数据存储器单元216(被标记为d0至d15)和互补数据存储器单元218(被标记为c0至c15)。初级存储器单元阵列201还包括多个字线208,使得多个字线208中的每个字线被耦合至多个存储器单元行202的每行。初级存储器单元阵列201还包括多个位线210。在每个扇区203具有两行202的实施例中,第一位线209被耦合至第一行244,并且第二位线211被耦合至第二行246(参见扇区<0>)。第一位线209被耦合至每个扇区203的每个第一行244,并且第二位线211被耦合至每个扇区203的每个第二行246。

30.多个存储器单元列204被耦合至列复用器220。每列将包括来自扇区的每行的一个存储器单元。位线被耦合至列的每隔一行。列204在下面将相对于存储器阵列的操作被讨论。

31.列复用器220包括位线选择晶体管222的第一多行,其中第一多个位线选择晶体管222中的每个晶体管被耦合至多个位线210中的独有位线。第一多个位线选择晶体管222的每行包括晶体管的第一组219和第二组221。每行的第一组存储器单元205被耦合至第一多个位线选择晶体管222的第一组219。每行的第二组存储器单元207被耦合至第一多个位线选择晶体管222的第二组221。位线选择晶体管222的多行被布置为第一行位线选择晶体管248和第二行位线选择晶体管250。第一行位线选择晶体管248中的晶体管通过第二位线211被耦合至存储器扇区203的第二存储器单元行246的晶体管。第二行位线选择晶体管250中的晶体管通过第一位线209被耦合至存储器扇区203的第一存储器单元行244的晶体管。列复用器220还包括多个组选择晶体管,其包括第一组224和第二组225,其中多个组选择晶体管224中的每个晶体管被耦合至多个位线选择晶体管222的组219,并且多个组选择晶体管225中的每个晶体管被耦合至多个位线选择晶体管222的组221。

32.初级存储器单元阵列201可以以差分读取模式或单端读取模式来读取。列复用器220包括多个模式选择晶体管226,其有助于差分和单端读取模式。在差分读取模式下,两个存储器单元206被用于存储数据位,即,第一组205中的一个存储器单元206和第二组207中的另一存储器单元206。在单端读取模式下,存储器单元206中的每个存储器单元206被用于一个数据位。多个模式选择晶体管226中的每个晶体管被耦合至多个组选择晶体管224和225的组中的一组。例如,第一行位线选择晶体管248的第一组219的多个晶体管y0<0>至y0<7>被耦合至组选择晶体管224的第一组中的晶体管ym<1>。晶体管ym<1>被耦合至第一类型的模式选择晶体管228的yn<0>和第二类型的模式选择晶体管230的yn<1>。第二行位线选择晶体管250的第一组219的多个晶体管y0<0>至y0<7>被耦合至组选择晶体管224的第一组中的晶体管ym<0>。晶体管ym<0>被耦合至第一类型的模式选择晶体管228的yn<0>和第二类型

的模式选择晶体管230的yn<1>。类似布置适用于第二组221,如在图2中可以看到的。

33.两种类型的模型选择晶体管226包括第一类型的模式选择晶体管228(yn<0>)和第二类型的模式选择晶体管230(yn<1>和yn<2>),其中模式选择晶体管226中的每个晶体管具有栅极端子、源极端子和漏极端子。列复用器220通过模式选择晶体管226被耦合至感测放大器232。感测放大器包括第一电流到电压转换器241和第二电流到电压转换器242,它们都被耦合至运算放大器234。参考电流晶体管开关238被耦合至第二电流到电压转换器242和具有存储器单元阵列240的参考电流生成器。这可以被认为是副本偏差生成器,其通过温度、过程、电压等来追踪存储器单元的电流。

34.第一类型的模式选择晶体管228的栅极端子通过反相器236被耦合至参考电流晶体管开关238的栅极端子。第一类型的模式选择晶体管228的源极端子被耦合至第二电流到电压转换器242的输入。多个模式选择晶体管226中的第二类型的模式选择晶体管230的源极端子被耦合在一起,并且被耦合至第一电流到电压转换器241的输入。第一电流到电压转换器241的输出被耦合至运算放大器234的正极端子的输入。第二电流到电压转换器242的输出被耦合至运算放大器234的负极端子的输入。

35.图3包括列解码器300,以用于从多个模式选择晶体管226中选择一个或多个模式选择晶体管yn<0>、yn<1>和yn<2>。列解码器300包括多个电平位移器302、耦合至电平位移器302的多个输入312以及反相器310。多个电平位移器302中的第一电平位移器304和反相器310接收差分使能信号314。多个电平位移器302中的第二电平位移器306接收输入信号316,该输入信号316是反相器310的输出。反相器310的输出信号316是反相的差分使能信号314。第三输入信号318是多个电平位移器302中的电平位移器308的输入。

36.多个电平位移器302提高或降低用于多个电平位移器302的多个输入312的电压电平。多个输出信号320是从多个电平位移器302输出的。多个输出320中的第一输出信号322是从电平位移器304输出的,多个输出信号320中的第二输出信号324是从电平位移器306输出的,并且多个输出信号320中的第三输出信号326是从电平位移器308输出的。输出信号322被耦合至第一类型的模式选择晶体管228的栅极。输出324和326被连接至第二类型230的两个模式选择晶体管231、233的栅极。

37.如上面解释的,图2中的存储器阵列200可以以差分读取模式或单端读取模式来读取。针对存储器阵列的差分读取,差分使能信号314保持为高,并且针对存储器阵列的单端读取,差分使能信号314保持为低。当差分使能信号314为高时,那么模式选择晶体管开关231断开,并且模式选择晶体管开关228和233接通。当差分使能信号314为低时,那么模式选择晶体管开关228断开,并且模式选择晶体管开关231和233接通。

38.图4包括另一列解码器400,以用于例如从多个组选择晶体管223中选择一个或多个组选择晶体管ym<0>和ym<1>。列解码器400包括被耦合至多个地址位404的多个反相器401。存在多个反相器401的多个输出423。存在耦合至多个电平位移器412的多个与门407。存在被耦合至多个与门407中的一个与门407的异或(x

‑

or)门417。存在多个电平位移器输出418。地址位404还包括耦合至第一反相器402的第一地址位405和耦合至第二反相器403的第二地址位406。多个与门407还包括与门408、409、410和411。多个电平位移器412还包括电平位移器413、414、415和416。电平位移器输出419是来自电平位移器413的输出,电平位移器输出420是来自电平位移器414的输出,电平位移器输出421是来自电平位移器415的输

出,并且电平位移器输出422是来自电平位移器416的输出。

39.反相器402和403的输出被耦合至与门408的输入,该与门408的输出被耦合至电平位移器413的输入。耦合至地址位405的反相器402的输入以及反相器403的输出425被耦合至与门409的输入,该与门409的输出被耦合至电平位移器414的输入。与门410的输入427被耦合至反相器402的输出424。与门410的另一输入428被耦合至x

‑

or门417的输出429。与门411的输入430被耦合至反相器402的输入,该反相器402被耦合至地址位405。与门411的另一输入431被耦合至x

‑

or门417的输出429。x

‑

or门417的输入432被耦合至反相器403的输入435,该反相器被耦合至地址位406。x

‑

or门417的输入426被耦合至差分使能信号314。

40.电平位移器输出419被耦合至多个组选择晶体管223的第一组224的晶体管251的栅极。电平位移器输出420被耦合至多个组选择晶体管223的第一组224的晶体管252的栅极。电平位移器输出421被耦合至多个组选择晶体管223的第二组225的晶体管254的栅极。电平位移器输出422被耦合至组选择晶体管223的第二组225的晶体管255的栅极。

41.如上面解释的,存储器阵列200可以以差分读取模式或单端读取模式来读取。作为一种配置的示例,针对存储器阵列的差分读取,差分使能信号314保持为高,并且针对存储器阵列的单端读取,差分使能信号314保持为低。

42.当组选择晶体管251、252、254和255接通时,这由逻辑1指示。当组选择晶体管251、252、254和255断开时,这由逻辑0指示。图4a的电路的真值表在图4b中,该图4b捕获组选择晶体管251、252、254和255的逻辑状态。真值表针对使能信号314以及地址位405和406的不同逻辑值提供组选择晶体管的不同逻辑状态。

43.图5包括存储器单元和电路组件的阵列500,其是可以在单端或差分读取操作中操作的图2的存储器阵列的表示。图5图示了存储器阵列500的差分读取操作。差分读取操作是在启动或引导操作时执行的,使得带隙参考电流尚未稳定并且未被使用。差分读取操作也可以在存储器的其他操作中被使用。在图6中,具有存储器单元阵列240的参考电流生成器在数据的单端读取期间被使用,该数据被存储在存储器阵列中。

44.存储器阵列500包括多个用户存储器扇区512以及一个或多个测试存储器扇区514。测试存储器扇区514被配置用于差分读取操作,而用户存储器扇区512被配置用于单端读取操作。测试存储器扇区514包括测试数据存储器单元501和互补测试数据存储器单元503。在该配置中,每个测试数据存储器单元在同一行中都具有对应的互补测试数据存储器单元。存储在互补测试数据存储器单元中的数据是存储在对应的测试数据存储器单元中的数据的互补或反相。为了读取测试数据存储器单元502,存储器阵列500从多个列解码器(诸如图3和4的列解码器300和400)接收指令。

45.指令在存储器阵列中发起以下步骤,以用于执行差分读取操作。测试数据存储器单元502(d1)被选择,并且对应的互补测试数据存储器单元504(c1)也被选择。位线选择晶体管的第一组219的第一位线选择晶体管510被接通。位线选择晶体管的第二组221的第二位线选择晶体管513被接通。来自第一组组选择晶体管224的第二组选择晶体管252被接通。来自第二组组选择晶体管225的第二组选择晶体管255被接通。第一类型的模式选择晶体管228被接通,并且第二类型的模式选择晶体管中的第二晶体管233被接通。第二类型的模式选择晶体管中的第一晶体管231被断开。该指令可以被重复,以用于读取测试数据存储器单元501中的任何一个。

46.当测试存储器单元502被读取时,该步骤允许多个第二位线211中的第一位线506放电。同时地,互补测试存储器单元504(c1)被读取,这导致多个第二位线211中的第二位线508上的电流放电。第一位线506通过晶体管510、252和228放电。放电后的电流由第二电流到电压转换器242被转换为电压。第二位线508通过晶体管512、255和233放电。放电后的电流由第一电流到电压转换器241被转换为电压。

47.两个电流到电压转换器241和242的输出是比较器或运算放大器(op

‑

amp)234的输入。运算放大器234比较来自电流到电压转换器241和242的两个电压输出,并且给出逻辑高或逻辑低输出。根据一种逻辑,如果擦除的测试存储器单元502被读取,则运算放大器234的输出为逻辑高(逻辑1),并且如果编程的测试存储器单元502被读取,则运算放大器234的输出为逻辑低(0)。如果不同逻辑被使用,则如果擦除的测试存储器单元502被读取,则运算放大器234的输出可以为逻辑低(逻辑0),并且如果编程的测试存储器单元502被读取,则运算放大器234的输出为逻辑高(1)。

48.由于晶体管228的栅极上的高电压,第一类型的模式选择晶体管228被接通。晶体管228的栅极上的高电压也是反相器236的输入。反相器236将高输入电压转换为低输出电压,该低输出电压关闭参考电流晶体管开关238,从而将具有存储器单元阵列240的参考电流生成器与存储器阵列500隔离开。

49.图6表示存储器阵列600的单端读取操作中的图2的存储器阵列。存储器阵列包括多个用户存储器扇区612以及一个或多个测试存储器扇区614。

50.测试存储器扇区614被配置为执行差分读取操作,而用户存储器扇区612被配置为执行单端读取操作。用户存储器扇区612包括用户数据存储器单元,其中存储器阵列600的用户存储数据以用于存储器阵列600的正常数据存储操作。存储在用户存储器阵列612中的数据被用于除了存储器启动操作之外的操作。

51.存储器阵列600包括具有存储器单元阵列240的参考电流生成器,以在单端读取操作中的读取期间稳定带隙参考电流。为了发起单端读取,存储器阵列600从多个列解码器(诸如图3和4中的那些列解码器)接收用于读取用户存储器单元602的指令。响应于该指令,用户存储器数据单元602被选择。位线选择晶体管的第一组219的第一位线选择晶体管610被接通。来自第一组组选择晶体管224的第一组选择晶体管251被接通。来自第一组组选择晶体管224的第二组选择晶体管252被断开。来自第二组组选择晶体管225的第二组选择晶体管254和255被断开。第一类型的模式选择晶体管228被断开。第二类型的模式选择晶体管230中的第二晶体管233被断开,并且第二类型的模式选择晶体管230中的第一晶体管231被接通。

52.作为响应,当测试存储器单元602被读取时,多个第一位线209中的第一位线606被放电。第一位线606通过晶体管610、251和231放电。放电后的电流由第一电流到电压转换器241被转换为电压。由于晶体管228的栅极上的低电压,第一类型的模式选择晶体管228被断开。晶体管228的栅极上的低电压是反相器236的输入。反相器236将低输入电压转换为高输出电压,该高输出电压接通参考电流晶体管开关238,从而允许具有存储器单元阵列240的参考电流生成器向第二电流到电压转换器242的输入提供电流。第二电流到电压转换器242将输入电流转换为电压。

53.两个电流到电压转换器241和242的输出是运算放大器(op

‑

amp)234的输入。运算

放大器234比较来自电流到电压转换器241和242的两个电压输出,并且给出逻辑高(逻辑1)或逻辑低(逻辑0)输出。根据一种逻辑,如果擦除的测试存储器单元602被读取,则运算放大器234的输出为逻辑高,并且如果编程的测试存储器单元602被读取,则运算放大器234的输出为逻辑低。如果不同逻辑被使用,则如果擦除的测试存储器单元602被读取,则运算放大器234的输出可以为逻辑低,并且如果编程的测试存储器单元602被读取,则运算放大器234的输出为逻辑高。

54.图10是图2和6的参考电流生成器存储器240的多个可能实施例中的一个实施例。具有存储器单元阵列240的参考电流生成器在感测放大器232中,并且被配置为在图2的存储器阵列的单端读取期间提供更稳定的参考电流。存储器阵列240包括次级存储器单元阵列1002,其通过列复用器1004被耦合至源极跟随器晶体管1006的源极。源极跟随器晶体管1006的漏极被耦合至p

‑

mos(p沟道金属氧化物半导体)电流镜1008,该p

‑

mos电流镜又被耦合至n

‑

mos(n沟道金属氧化物半导体)电流镜1010。

55.代替带隙参考电流生成块104,具有存储器单元阵列240的参考电流生成器可以在常规存储器中被使用,以提供更稳定的参考电流。针对单端存储器读取操作,具有存储器单元阵列240的电流生成器被构造为使得向存储器阵列600提供比带隙参考电流生成器块104更准确的参考电流。

56.为了由具有存储器单元阵列240的参考电流生成器提供更准确的电流生成,次级存储器单元阵列1002是使用与用于制造初级存储器单元阵列201的单元的过程相同的过程来制造的。这确保了存储器阵列1002的存储器单元对过程、温度和其他操作变化的响应与初级存储器单元阵列201的存储器单元的响应相同或基本上类似。存储器阵列240的列复用器1004可以具有与单端读取存储器阵列600的列复用器220相同的架构。这使用于读取阵列201和1002的存储器单元的时间之间的时间变化最小化。

57.为了生成稳定的参考电流,次级存储器单元阵列1002的存储器单元被一起读取和平均。次级存储器单元阵列1002包括偶数数目的存储器单元。一半的存储器单元是编程单元(即,逻辑1),并且一半的存储器单元是擦除单元(即,逻辑0)。次级存储器单元阵列1002的单元的所有单元或偶数子集被选择,以用于在配置阶段期间读取。在该示例中,两个单元1012、1014被选择以用于读取。备选地,当更准确的参考电流是优选的并且单元的偶数子集被选择以用于读取时,所有单元被选择。

58.参考电流生成存储器被配置为对由用于读取的所选单元产生的电流取平均值,以输出阵列1002的平均电流,该平均电流代表单个存储器单元要与从初级存储器单元阵列读取的单元进行比较。被选择用于读取的单元数目越大,从存储器240到存储器阵列200的参考电流将更准确。

59.为了向存储器阵列600提供更多的准确参考电流,当vgs或vread电压被施加到单元1012和1014的栅极时,存储器240的次级存储器单元阵列1002预选第一存储器单元1012和第二存储器单元1014。在存储器单元1012和1014中,一个单元是擦除的存储器单元,并且另一个是编程的存储器单元。在接收偏置电压vds时,源极跟随器晶体管1006被接通。这允许单个位线1016通过p

‑

mos电流镜1008的第一p

‑

mos晶体管1007和源极跟随器晶体管1006放电或以其他方式解决电流。电流镜1008允许与两个存储器单元1012和1014相对应的平均电流流过p

‑

mos电流镜1008的第二p

‑

mos晶体管。该电流然后经过n

‑

mos电流镜1010。n

‑

mos

电流镜1010的n

‑

mos晶体管1013的漏极上可用的电流是存储器阵列600的单端读取操作所需的参考电流。

60.图7包括存储器单元702的可配置行700,使得行700的任何存储器单元都可以被配置为在单端或差分读取模式下操作。代替用户存储器扇区行512或测试存储器扇区行514,可配置的存储器行700可以在存储器阵列500中被使用,以向存储器用户提供灵活性。利用可配置行700的布置,并不迫使存储器用户仅在差分读取模式下或者仅在单端读取模式下使用存储器行。利用存储器阵列500的行,每行被建立为单端读取行或者差分读取行,并且未在使用期间被调整。因此,这些行的存储器单元中的一些单元在操作期间可能未由存储器使用,这可能不是存储器区域的最有效使用。相反,可配置行700可以被用作单端读取行、差分读取行或者单端和差分读取行的组合。这提供了由多个这些可配置行700形成的存储器阵列的灵活使用,使得每行可以被配置为对于整体存储器功能最有益的读取类型。

61.该可配置行700布置提供了区域效率,并且提供了对更多存储器单元的访问,否则该存储器单元可能无法在存储器阵列中被访问,该存储器阵列具有专用的单端读取行和专用的差分读取行。利用专用的差分读取行,如果一些单元未被用于启动或引导操作,则那些单元在存储器的生命周期内保持未使用和不可访问。相反,在可配置行700中,未被用于针对差分读取的启动或引导操作的任何单元都将针对用户数据保持可访问和可用,使用单端读取来读取。因此,存储器阵列中的更多存储器单元可以被使用,从而最大化可用存储器。在可配置的存储器行700的一个具体实施例中,存在十六个存储器单元702。前四个存储器单元构成可配置的存储器行700的第一字,并且后四个存储器单元构成可配置的存储器行700的第二字。八个存储器单元被配置为差分读取存储器单元,并且剩余的八个存储器单元被配置为单端读取存储器单元。八个差分读取存储器单元同样地被划分为测试数据存储器单元d1、d2、d3、d4和互补测试数据存储器单元c1、c2、c3、c4,它们在图7的该实施例中被放置在中心。在其他实施例中,差分读取测试数据存储器单元可以通过单端存储器单元与互补测试数据存储器单元分开。

62.在图7的实施例中,在差分读取单元706的第一侧存在四个单端读取单元704。在差分读取单元706的第二侧存在四个单端读取单元708。单端读取单元和差分读取单元的不同配置被设想,使得在可配置的存储器单元行中,该行包括第一多个单端读取单元,其通过多个差分读取单元与第二多个单端读取单元分开,使得在可配置的存储器行700的第一字和第二字中,测试数据存储器单元和互补测试数据存储器单元绝不放置在同一字中。多个差分读取单元的数目等于第一多个单端读取单元和第二多个单端读取单元的数目。例如,在该实施例中,存在8个差分读取单元,并且总共存在8个单端读取单元。

63.在替代实施例中,可配置行700可以包括分别被配置用于差分读取的十个或十二个单元以及被配置用于单端读取的六个或四个单元。

64.差分读取单元可以是该行的前单元,并且单端读取单元可以是该行的末单元,使得差分读取单元不在单端读取单元中的多个单端读取单元之间。

65.在使用包括多个可配置行700的存储器阵列的示例方法中,第一行包括多个第一存储器单元,并且第二行包括第二多个存储器单元。第一行被配置为在第一布置中具有单端和差分读取单元。第二行被配置为在第二布置中具有单端和差分读取单元,该第二布置不同于第一布置。例如,第一布置可以是图7中的布置,其中在差分读取单元的两侧具有单

端读取单元。第二布置可以首先具有单端读取单元,接着是差分读取单元。第一行中的单端读取单元的数目可以不同于第二行中的单端读取单元的数目。

66.在另一配置中,第一行被配置为在第一布置中具有单端和差分读取单元,并且第二行在第二布置中仅具有单端读取单元或差分读取单元。在第二布置中,差分读取单元首先可以被布置有所有测试数据存储器单元,接着是互补测试数据存储器单元,只要在可配置的存储器行700的第一字和第二字中,测试数据存储器单元和互补测试数据存储器单元未被放置在同一字中即可。

67.在又一实施例中,存储器的可配置行可以分别在第一使用时间段内具有第一配置,并且在第二使用时间段内具有第二配置,使得用户或制造商(诸如通过更新)可以重用每行,这对存储器阵列和存储器的当前用例来说最有益。

68.图8是存储器阵列800的一部分,该存储器阵列800包括多个可配置的存储器行700。在该实施例中,在存储器阵列的该部分中存在两行806、808,然而,可能存在由应用或访问存储器的用户选择的任何数目的行。该部分的行806、808中的每行中的数据是相同的。该行中的这种相同数据提供了存储器单元的更准确读取,因为该数据可以在差分读取或单端读取期间被平均。这些行可以与本公开的附图(诸如图5和6)的电路结构集成在一起。具体地,图3和4的列解码器、感测放大器和参考生成器存储器240等其他电路系统将与这些行集成在一起,以执行本文描述的读取操作。

69.在该部分中,两行806、808被配置为在该行的第一字中具有测试数据单元802,并且在该行的第二字中具有互补测试数据单元803。其他单元可以是附加的差分读取单元或者单端读取单元,如由存储器的当前用例建立的。

70.为了读取相同行,多个位线209或211中的对应位线通过相同的存储器单元802和804被放电。这些位线运送电流,该电流是两个存储器单元802和804的平均电流。来自相同数据行的相同存储器单元的数目越大,读取更准确,因为将存在更多单元要平均。该平均使温度和过程变化、制造差异以及其他变化的影响最小化,该其他变化会影响存储器单元中的数据的准确性。类似地,在另一实施例中,在单端读取的情况下,两个存储器行806和808中沿着同一位线的两个相同的存储器单元可以通过使对应位线放电来读取。

71.图9是存储器阵列900的一部分,图示了本公开的存储器阵列的另一实施例,该存储器阵列900可以使用两个或更多个可配置的存储器行700。在该配置中,基于加密逻辑,测试数据存储器单元在一行中,并且对应的互补测试数据存储器单元在另一行中。这种加密逻辑结合列解码器逻辑被使用,该列解码器逻辑被用于选择用于读取的存储器单元。当在这些存储器阵列中使用时,加密逻辑产生难以破解的存储器,从而提供更安全的存储器。

72.该加密是在存储器阵列900的该部分中实现的,其中测试数据存储器单元902在第一存储器行910中,并且对应的互补测试数据存储器单元904在第二存储器行912中。测试数据存储器单元902在第一行910的第一字的第二单元中,并且互补测试数据存储器单元904在第二行912的第二字的第二单元中。针对测试数据存储器单元902的差分读取,第一行和第二行是使用加密逻辑和列解码器逻辑来访问的。同样地,测试数据存储器单元906在第一存储器行910的第二字的第三单元中,并且对应的互补测试数据存储器单元908在第二存储器行912的第一字的第三单元中。通常,测试数据存储器单元和互补测试数据存储器单元无法在同一字中。

73.在本公开中,读取准确性是通过对来自多个存储器单元的电流取平均值来实现的,该多个存储器单元在单端和差分读取操作中具有沿着公共位线放置的相同数据。在正常存储器操作期间提高读取准确性的另一技术被示出,其中参考电流是从存储器单元的参考存储器阵列获得的,该参考存储器阵列是使用与初级存储器阵列相同的存储器单元组成的,在上面被称为可配置的存储器阵列。通过在相同或错列的字位置中,将测试数据存储器单元放置在一个存储器行中,并且将互补测试数据存储器单元放置在另一行中,用于实现数据安全性的加密被确保。

74.本公开涉及一种包括可配置的存储器阵列的设备,该可配置的存储器阵列包括多行存储器单元,至少一行存储器单元包括多个用户数据存储器单元、多个测试数据存储器单元和多个互补测试数据存储器单元。该行至少包括第一字和第二字,多个测试数据存储器单元在第一字中,并且多个互补测试数据存储器单元在第二字中。多个用户数据存储器单元的第一组在第一字中,并且多个用户数据存储器单元的第二组在第二字中。多个用户数据存储器单元的第一组通过多个测试数据存储器单元和多个互补测试数据存储器单元与多个用户数据存储器单元的第二组分开。

75.该行中的多个测试数据存储器单元和多个互补测试数据存储器单元通过多个用户数据存储器单元分开。多个用户数据存储器单元被配置为利用单端读取操作来读取,并且多个测试数据存储器单元和多个互补测试数据存储器单元被配置为利用差分读取操作来读取。多行中的每行均包括第一字和第二字,可配置的存储器阵列包括耦合至每行的第一字和第二字的列复用器、耦合至列复用器的感测放大器。感测放大器包括参考电流存储器单元阵列。参考电流存储器单元阵列被配置为在单端读取操作中提供感测放大器中的参考电流。

76.本公开涉及一种包括可配置的存储器阵列的设备,该可配置的存储器阵列具有包括多个测试数据存储器单元的第一行存储器单元以及包括多个互补测试数据存储器单元的第二行存储器单元,该多个互补测试数据存储器单元对应于第一行的多个测试数据存储器单元。第一行包括第一字和第二字,并且第二行包括第一字和第二字。第一测试数据存储器单元在第一行的第一字中,并且第一互补测试数据存储器单元在第二行的第二字中。第二测试数据存储器单元在第一行的第二字中,并且第二互补测试数据存储器单元在第二行的第一字中。

77.第一行的第一字中的多个测试数据存储器单元对应于第二行的第二字中的多个互补测试数据存储器单元。第一行的第二字中的多个测试数据存储器单元对应于第二行的第一字中的多个互补测试数据存储器单元。

78.本公开涉及一种方法,包括通过沿着第一位线平均来自两个或更多个存储器单元的电流,来读取初级存储器阵列。该读取包括选择初级存储器阵列的存储器行,每行将相同的数据值存储在每行的相应存储器单元中,并且根据列解码器逻辑,在列复用器和感测放大器中启动与第一位线相对应的第一多个晶体管。所选存储器行中的每个存储器行在初级存储器阵列中彼此相邻。该方法还包括使用第一位线执行单端读取操作,其中读取包括在感测放大器中生成参考电流生成器存储器单元阵列中的参考电流,使第一位线放电,将来自放电后的第一位线的电流转换为第一电压,将来自参考电流的电流转换为第二电压,并且将第一电压与第二电压进行比较。

79.该生成包括从参考电流生成器存储器单元阵列读取的多个存储器单元,参考电流生成器存储器单元阵列的存储器单元具有与初级存储器阵列相同的温度和过程变化。从参考电流生成器存储器单元阵列读取多个存储器单元包括:将读取信号发送给参考电流生成器存储器单元阵列的第一行和第二行,并且利用列复用器使参考电流生成器存储器单元阵列的位线放电,该列复用器与参考电流生成器存储器单元阵列的第一行和第二行的存储器单元相关联。

80.该方法还包括执行差分读取操作,该读取包括沿着第二位线平均来自两个或更多个存储器单元的电流,该第二位线对应于互补测试数据存储器单元,并且第一位线对应于测试数据存储器单元。读取包括:根据列解码器逻辑,在列复用器和感测放大器中启动与第二位线相对应的第二多个晶体管。

81.本公开涉及一种包括初级存储器阵列的设备,该初级存储器阵列具有多个位线、多行存储器单元、耦合至多个位线的列复用器以及耦合至列复用器的感测放大器。感测放大器包括参考电流生成器存储器单元阵列。参考电流生成器存储器单元阵列包括多行参考电流存储器单元、列复用器和电流镜。列复用器被耦合在电流镜与多行参考电流存储器单元之间。

82.感测放大器还包括第一电流到电压转换器、第二电流到电压转换器,参考电流生成器存储器单元阵列被耦合至第二电流到电压转换器。初级存储器阵列的列复用器包括多个位线选择晶体管、耦合至多个位线选择晶体管的多个组选择晶体管以及耦合至多个组选择晶体管和感测放大器的多个模式选择晶体管,多个模式选择晶体管中的第一模式选择晶体管被耦合至参考电流生成器存储器单元阵列。

83.本公开涉及一种方法,包括在半导体衬底中形成包括多行存储器单元的初级存储器单元阵列以及包括多行存储器单元的参考电流生成器存储器单元阵列,在衬底中形成第一列复用器和感测放大器,将第一列复用器耦合至初级存储器单元阵列的位线,将感测放大器耦合至第一列复用器和参考电流生成器存储器单元阵列。该方法还包括在感测放大器中形成第一电流到电压转换器和第二电流到电压转换器,在感测放大器中形成比较器,将第一电流到电压转换器和第二电流到电压转换器耦合至比较器,将参考电流生成器存储器单元阵列耦合至第二电流到电压转换器。

84.该方法包括将第一列复用器耦合至感测放大器的第一电流到电压转换器和第二电流到电压转换器。该方法还包括同时形成初级存储器单元阵列,并且形成参考电流生成器存储器单元阵列。该方法还包括形成第二列复用器,将第二列复用器耦合至多行参考电流生成器存储器单元阵列,形成电流镜,并且将电流镜耦合至第二列复用器。

85.本公开涉及一种包括初级存储器阵列的设备,该初级存储器阵列具有:第一可配置行,该第一可配置行具有第一多个存储器单元,包括处于第一配置并且具有第一数据集的第一多个测试数据单元和第一多个互补测试数据单元;以及第二可配置行,该第二可配置行具有第二多个存储器单元,包括处于第一配置并且具有第一数据集的第二多个测试数据单元和第二多个互补测试数据单元。初级存储器阵列在操作中从来自第一可配置行的第一多个测试数据单元和来自第二可配置行的第二多个测试数据单元平均对应数据。初级存储器阵列包括具有第三多个存储器单元的第三可配置行,该第三多个存储器单元包括处于第一配置并且具有第一数据集并在操作中的第三多个测试数据单元和第三多个互补测试

数据单元,初级存储器阵列在操作中从来自第一可配置行的第一多个测试数据单元、来自第二可配置行的第二多个测试数据单元和来自第三可配置行的第三多个测试数据单元平均对应数据。

86.第一可配置行和第二可配置行在第一操作时间段中存储第一数据集,并且在第二操作时间段中,第一可配置行在处于第二配置的第一多个存储器单元中具有第二数据集,并且第二可配置行在处于第二配置的第二多个存储器单元中具有第二数据集。第一可配置行和第二可配置行在第一操作时间段中存储第一数据集,并且在第二操作时间段中,第一可配置行在第一多个存储器单元中具有第二数据集,并且第二可配置行在第二多个存储器单元中具有第三数据集,第二数据集和第三数据集不同。

87.本公开涉及一种设备,包括衬底、衬底中的初级存储器阵列,该初级存储器阵列包括:多行存储器单元、耦合至多行存储器单元的第一列复用器、耦合至第一列复用器的感测放大器,该感测放大器包括:衬底中的参考电流生成器存储器阵列。第一列复用器包括:多行位线选择晶体管;多个组选择晶体管,被耦合至多行位线选择晶体管;多个模式选择晶体管,被耦合至多个组选择晶体管和感测放大器。第一列复用器包括列解码器,该列解码器包括:第一电平位移器,被耦合在使能信号与多个模式选择晶体管中的第一模式选择晶体管之间;第二电平位移器,被耦合在使能信号的反相与多个模式选择晶体管中的第二模式选择晶体管之间;以及第三电平位移器,被耦合至多个模式选择晶体管中的第三模式选择晶体管。

88.第一列复用器包括列解码器,该列解码器包括:多个反相器;多个地址位,被耦合至多个反相器;多个电平位移器,被耦合至多个地址位和多个反相器。列解码器包括耦合至多个电平位移器的多个与门以及耦合至多个与门中的一个与门的异或门。多个地址位包括耦合至多个反相器中的第一反相器的第一地址位以及耦合至多个反相器中的第二反相器的第二地址位。

89.示例1.一种设备,包括:

90.可配置的存储器阵列,包括:

91.多行存储器单元,至少一行所述存储器单元包括多个用户数据存储器单元、多个测试数据存储器单元和多个互补测试数据存储器单元。

92.示例2.根据示例1所述的设备,其中所述行至少包括第一字和第二字,所述多个测试数据存储器单元在所述第一字中,并且所述多个互补测试数据存储器单元在所述第二字中。

93.示例3.根据示例2所述的设备,其中所述多个用户数据存储器单元的第一组在所述第一字中,并且所述多个用户数据存储器单元的第二组在所述第二字中。

94.示例4.根据示例3所述的设备,其中所述多个用户数据存储器单元的所述第一组通过所述多个测试数据存储器单元和所述多个互补测试数据存储器单元与所述多个用户数据存储器单元的所述第二组分开。

95.示例5.根据示例1所述的设备,其中所述行中的所述多个测试数据存储器单元和所述多个互补测试数据存储器单元通过所述多个用户数据存储器单元分开。

96.示例6.根据示例1所述的设备,其中所述多个用户数据存储器单元被配置为利用单端读取操作来读取,并且所述多个测试数据存储器单元和所述多个互补测试数据存储器

单元被配置为利用差分读取操作来读取。

97.示例7.根据示例1所述的设备,其中所述多行中的每行均包括第一字和第二字,所述可配置的存储器阵列包括:

98.列复用器,被耦合至每行的所述第一字和所述第二字;以及

99.感测放大器,被耦合至所述列复用器,所述感测放大器包括:

100.参考电流存储器单元阵列。

101.示例8.根据示例7所述的设备,其中所述参考电流存储器单元阵列被配置为在单端读取操作中提供所述感测放大器中的参考电流。

102.示例9.一种设备,包括:

103.可配置的存储器阵列,包括:

104.存储器单元的第一行,包括多个测试数据存储器单元;以及存储器单元的第二行,包括与所述第一行的所述多个测试数据存储器单元相对应的多个互补测试数据存储器单元。

105.示例10.根据示例9所述的设备,其中所述第一行包括第一字和第二字,并且所述第二行包括第一字和第二字。

106.示例11.根据示例10所述的设备,其中第一测试数据存储器单元在所述第一行的第一字中,并且第一互补测试数据存储器单元在所述第二行的第二字中。

107.示例12.根据示例11所述的设备,其中第二测试数据存储器单元在所述第一行的第二字中,并且第二互补测试数据存储器单元在所述第二行的第一字中。

108.示例13.根据示例10所述的设备,其中所述第一行的第一字中的所述多个测试数据存储器单元对应于所述第二行的第二字中的所述多个互补测试数据存储器单元。

109.示例14.根据示例13所述的设备,其中所述第一行的第二字中的所述多个测试数据存储器单元对应于所述第二行的第一字中的所述多个互补测试数据存储器单元。

110.示例15.一种方法,包括:

111.通过沿着第一位线平均来自两个或更多个存储器单元的电流,来读取初级存储器阵列,所述读取包括:

112.选择所述初级存储器阵列的存储器行,每行将相同的数据值存储在每行的相应存储器单元中;以及

113.根据列解码器逻辑,在列复用器和感测放大器中启动与所述第一位线相对应的第一多个晶体管。

114.示例16.根据示例15所述的方法,其中所选的所述存储器行中的每个存储器行在所述初级存储器阵列中彼此相邻。

115.示例17.根据示例15所述的方法,还包括使用所述第一位线执行单端读取操作,其中所述读取包括:

116.在所述感测放大器中的参考电流生成器存储器单元阵列中生成参考电流;

117.使所述第一位线放电;

118.将来自放电后的所述第一位线的电流转换为第一电压;

119.将来自所述参考电流的电流转换为第二电压;以及

120.将所述第一电压与所述第二电压进行比较。

121.示例18.根据示例17所述的方法,其中所述生成包括从所述参考电流生成器存储器单元阵列读取多个存储器单元,所述参考电流生成器存储器单元阵列的所述存储器单元具有与所述初级存储器阵列相同的温度和过程变化。

122.示例19.根据示例18所述的方法,其中从所述参考电流生成器存储器单元阵列读取所述多个存储器单元包括:

123.将读取信号发送给参考电流生成器存储器单元阵列的第一行和第二行;以及

124.利用列复用器使所述参考电流生成器存储器单元阵列的位线放电,所述列复用器与所述参考电流生成器存储器单元阵列的所述第一行和所述第二行的所述存储器单元相关联。

125.示例20.根据示例15所述的方法,还包括执行差分读取操作,所述读取包括沿着第二位线平均来自两个或更多个存储器单元的电流,所述第二位线对应于互补测试数据存储器单元,并且所述第一位线对应于测试数据存储器单元。

126.示例21.根据示例20所述的方法,其中所述读取包括:根据所述列解码器逻辑,在所述列复用器和所述感测放大器中启动与所述第二位线相对应的第二多个晶体管。

127.示例22.一种设备,包括:

128.初级存储器阵列,包括:

129.多个位线;

130.多行存储器单元;和

131.列复用器,被耦合至所述多个位线;以及

132.感测放大器,被耦合至所述列复用器,所述感测放大器包括:

133.参考电流生成器存储器单元阵列。

134.示例23.根据示例22所述的设备,其中所述参考电流生成器存储器单元阵列包括:

135.多行参考电流存储器单元;

136.列复用器;以及

137.电流镜。

138.示例24.根据示例23所述的设备,其中所述列复用器被耦合在所述电流镜与所述多行参考电流存储器单元之间。

139.示例25.根据示例23所述的设备,其中所述感测放大器还包括:

140.第一电流到电压转换器;以及

141.第二电流到电压转换器,所述参考电流生成器存储器单元阵列被耦合至所述第二电流到电压转换器。

142.示例26.根据示例25所述的设备,其中所述初级存储器阵列的所述列复用器包括:

143.多个位线选择晶体管;

144.多个组选择晶体管,被耦合至所述多个位线选择晶体管;

145.多个模式选择晶体管,被耦合至所述多个组选择晶体管和所述感测放大器,所述多个模式选择晶体管中的第一模式选择晶体管被耦合至所述参考电流生成器存储器单元阵列。

146.示例27.一种方法,包括:

147.在半导体衬底中形成包括多行存储器单元的初级存储器单元阵列以及包括多行

存储器单元的参考电流生成器存储器单元阵列;

148.在所述衬底中形成第一列复用器和感测放大器;

149.将所述第一列复用器耦合至所述初级存储器单元阵列的位线;

150.将感测放大器耦合至所述第一列复用器和所述参考电流生成器存储器单元阵列。

151.示例28.根据示例27所述的方法,还包括:

152.在所述感测放大器中形成第一电流到电压转换器和第二电流到电压转换器;

153.在所述感测放大器中形成比较器;

154.将所述第一电流到电压转换器和所述第二电流到电压转换器耦合至所述比较器;

155.将所述参考电流生成器存储器单元阵列耦合至所述第二电流到电压转换器。

156.示例29.根据示例28所述的方法,还包括:

157.将第一列复用器耦合至所述感测放大器的所述第一电流到电压转换器和所述第二电流到电压转换器。

158.示例30.根据示例27所述的方法,还包括:同时形成所述初级存储器单元阵列,并且形成所述参考电流生成器存储器单元阵列。

159.示例31.根据示例27所述的方法,还包括:

160.形成第二列复用器;

161.将所述第二列复用器耦合至多行所述参考电流生成器存储器单元阵列;

162.形成电流镜;

163.将所述电流镜耦合至所述第二列复用器。

164.示例32.一种设备,包括:

165.初级存储器阵列,包括:

166.第一可配置行,具有第一多个存储器单元,所述第一多个存储器单元包括处于第一配置并且具有第一数据集的第一多个测试数据单元和第一多个互补测试数据单元;以及

167.第二可配置行,具有第二多个存储器单元,所述第二多个存储器单元包括处于所述第一配置并且具有所述第一数据集的第二多个测试数据单元和第二多个互补测试数据单元。

168.示例33.根据示例32所述的设备,其中所述初级存储器阵列在操作中从来自所述第一可配置行的所述第一多个测试数据单元和来自所述第二可配置行的所述第二多个测试数据单元平均对应数据。

169.示例34.根据示例32所述的设备,其中所述初级存储器阵列包括具有第三多个存储器单元的第三可配置行,所述第三多个存储器单元包括处于所述第一配置并且具有所述第一数据集并在操作中的第三多个测试数据单元和第三多个互补测试数据单元,所述初级存储器阵列在操作中从来自所述第一可配置行的所述第一多个测试数据单元、来自所述第二可配置行的所述第二多个测试数据单元和来自所述第三可配置行的所述第三多个测试数据单元平均对应数据。

170.示例35.根据示例32所述的设备,其中所述第一可配置行和所述第二可配置行在第一操作时间段中存储所述第一数据集,并且在第二操作时间段中,所述第一可配置行在处于第二配置的所述第一多个存储器单元中具有第二数据集,并且所述第二可配置行在处于所述第二配置的所述第二多个存储器单元中具有所述第二数据集。

171.示例36.根据示例35所述的设备,其中所述第一可配置行和所述第二可配置行在第一操作时间段中存储所述第一数据集,并且在第二操作时间段中,所述第一可配置行在所述第一多个存储器单元中具有第二数据集,并且所述第二可配置行在所述第二多个存储器单元中具有第三数据集,所述第二数据集和所述第三数据集不同。

172.示例37.一种设备,包括:

173.衬底;以及

174.所述衬底中的初级存储器阵列,所述初级存储器阵列包括:

175.多行存储器单元;

176.第一列复用器,被耦合至所述多行存储器单元;以及

177.感测放大器,被耦合至所述第一列复用器,所述感测放大器包括:

178.所述衬底中的参考电流生成器存储器阵列。

179.示例38.根据示例37所述的设备,其中所述第一列复用器包括:

180.多行位线选择晶体管;

181.多个组选择晶体管,被耦合至所述多行位线选择晶体管;

182.多个模式选择晶体管,被耦合至所述多个组选择晶体管和所述感测放大器。

183.示例39.根据示例38所述的设备,其中所述第一列复用器包括列解码器,所述列解码器包括:

184.第一电平位移器,被耦合在使能信号与所述多个模式选择晶体管中的第一模式选择晶体管之间;

185.第二电平位移器,被耦合在所述使能信号的反相与所述多个模式选择晶体管中的第二模式选择晶体管之间;以及

186.第三电平位移器,被耦合至所述多个模式选择晶体管中的第三模式选择晶体管。

187.示例40.根据示例38所述的设备,其中所述第一列复用器包括列解码器,所述列解码器包括:

188.多个反相器;

189.多个地址位,被耦合至所述多个反相器;

190.多个电平位移器,被耦合至所述多个地址位和所述多个反相器。

191.示例41.根据示例40所述的设备,其中所述列解码器包括耦合至所述多个电平位移器的多个与门以及耦合至所述多个与门中的一个与门的异或门。

192.示例42.根据示例41所述的设备,其中所述多个地址位包括耦合至所述多个反相器中的第一反相器的第一地址位以及耦合至所述多个反相器中的第二反相器的第二地址位。

193.上述各种实施例可以被组合,以提供其他实施例。在本说明书中提及和/或在应用数据单中列举的美国专利、美国专利申请出版物、美国专利申请、外国专利、外国专利申请和非专利出版物中的所有通过引用全部并入本文。如果需要采用各种专利、申请和出版物的概念以提供其他实施例,则实施例的各个方面可以被修改。

194.鉴于上面详述的描述,这些和其他改变可以对实施例进行。通常,在以下权利要求中,所使用的术语不应被解释为将权利要求限于本说明书和权利要求中所公开的具体实施例,而是应被解释为包括所有可能的实施例以及这种权利要求被赋予的等效物的全部范

围。因此,权利要求不受本公开的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。