技术特征:

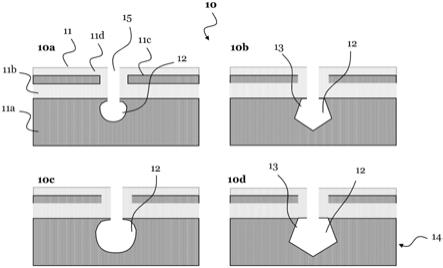

1.一种用于在绝缘体上硅soi结构(11)的绝缘体层(11b)下的硅基材(11a)中制造一个或多个腔室(12)的方法(10),所述方法(10)包括:对硅基材(11a)进行第一干法蚀刻(10a)以在绝缘体层(11b)下产生一个或多个腔室(12);对硅基材(11a)进行第一湿法蚀刻(10b)以使一个或多个腔室(12)扩张;对硅基材(11a)进行第二干湿法蚀刻(10c)以使一个或多个腔室(12)进一步扩张,并且破坏由第一湿法蚀刻产生的硅琢面(13);以及进行第二湿法蚀刻(10d)以使一个或多个腔室(12)扩张。2.如权利要求1所述的方法(10),所述方法(10)还包括:对硅基材(11a)交替进行一个或多个其它干法蚀刻和一个或多个其它湿法蚀刻;其中,各其它干法蚀刻使一个或多个腔室(12)进一步扩张,并且破坏由前序湿法蚀刻产生的硅琢面(13);以及各其它湿法蚀刻使一个或多个腔室(12)进一步扩张。3.如权利要求1或2所述的方法(10),所述方法还包括在进行第一干法蚀刻(10a)之前:蚀刻一个或多个沟槽(15)穿过绝缘体层(11b)并进入soi结构(11)的硅基材(11a)中;通过所述一个或多个沟槽(40)进行第一干法蚀刻(10a),以在绝缘体层(11b)下形成一个或多个腔室(12)。4.根据权利要求1至3中任一项所述的方法(10),其中,在硅基材(11a)中形成至少两个相邻腔室(12),并进行干法蚀刻和湿法蚀刻(10a

‑

10d),直至至少两个相邻腔室(12)合并。5.根据权利要求1至4中任一项所述的方法(10),其中,进行干法蚀刻和湿法蚀刻(10a

‑

10d),直至一个或多个腔室(12)的顶侧(70)到达绝缘体层(11b)。6.根据权利要求1至5中任一项所述的方法(10),其中,干法蚀刻(10a,10c)是选择性体硅蚀刻和/或各向同性蚀刻。7.根据权利要求1至6中任一项所述的方法(10),其中,干法蚀刻(10a,10c)各自包括包含氟的蚀刻步骤。8.根据权利要求1至7中任一项所述的方法(10),其中,干法蚀刻(10a,10c)各自包括使用六氟化硫或二氟化氙与氩或氦组合的蚀刻步骤。9.根据权利要求1至8中任一项所述的方法(10),其中,干法蚀刻(10a,10c)在80℃至120℃的温度下各自进行1000秒至1400秒。10.根据权利要求1至9中任一项所述的方法(10),其中,湿法蚀刻(10b,10d)是各向异性湿法蚀刻。11.根据权利要求1至10中任一项所述的方法(10),其中,湿法蚀刻(10b,10d)各自包括使用氢氧化四甲基铵和/或氢氧化钾的蚀刻步骤。12.如权利要求11所述的方法(10),其中,湿法蚀刻(10b,10d)各自包括使用氟化氢以去除原生氧化物的蚀刻步骤。13.如权利要求12所述的方法(10),其中,湿法蚀刻(10b,10d)各自包括使用0.2%至0.4%的氟化氢进行10秒至20秒的蚀刻步

骤,随后使用2%至8%的氢氧化四甲基铵在75℃至85℃的温度下进行400秒至800秒的蚀刻步骤。14.根据权利要求1至13中任一项所述的方法(10),所述方法还包括:在各干法蚀刻(10a,10c)和后续湿法蚀刻(10b,10d)之间进行剥离和/或清洗步骤。15.一种在绝缘体soi结构(14)上的半导体,其包括:硅基材(11a)、绝缘体层(11b)、以及在绝缘体层(11b)下形成的一个或多个腔室(12);其中,soi结构(14)是使用如权利要求1至14中任一项所述的方法(10)制备的。

技术总结

本公开涉及一种用于在绝缘体上硅(SOI)结构中产生底切(UCUT)的方法,具体涉及一种用于300mm SOI平台的方法。为此,本公开提供了一种用于在SOI结构的绝缘体层下的硅基材中制造一个或多个腔室的方法。该方法包括:对硅基材进行第一干法蚀刻以产生一个或多个腔室,对硅基材进行第一湿法蚀刻以使一个或多个腔室扩张,对硅基材进行第二干湿法蚀刻以使一个或多个腔室进一步扩张,并且破坏由第一湿法蚀刻产生的硅琢面,以及进行第二湿法蚀刻以使一个或多个腔室扩张。个腔室扩张。个腔室扩张。

技术研发人员:D

受保护的技术使用者:IMEC非营利协会

技术研发日:2021.05.27

技术公布日:2021/12/3

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。