1.本技术涉及半导体技术领域,特别是涉及一种晶圆结构及其制作方法。

背景技术:

2.随着半导体技术的快速发展,芯片的集成度也随之不断提高,使得芯片的制作工艺日趋复杂。为了保证较高的成品率,对整个芯片加工工艺流程和装置设备的要求就会更加严格。光刻的基本原理是:利用光刻胶曝光后因光化学反应而形成耐蚀性的特点,使光刻胶在特殊波长光线或者电子束下发生化学变化,通过曝光、显影、刻蚀等工艺过程,将设计在掩膜上的图形转移到被加工的晶圆(wafer)上。在曝光过程中,由于曝光系统一次曝光的面积大小是有限的,因此在曝光时会产生非完全曝光的芯片。工艺过程中,为了监控过程工艺质量,需要对这样的非完整芯片进行标识。

3.传统的标识方法主要采用物理墨点的形式对非完整芯片进行标识,主要步骤为:在芯片完成过程工艺及测试后,将硅片放入物理墨点的设备,输入专用程序,对第一颗非完整芯粒进行打墨点工艺,待打点完成后,将硅片放入烘箱进行墨点烘干操作。

4.然而,传统的标识方法不仅需要昂贵的专用设备以及打墨点工艺所需的材料,工艺步骤还较为繁琐复杂;同时,在加工过程中容易产生硅片破碎及沾污等问题。

技术实现要素:

5.基于此,有必要针对上述背景技术中的技术问题,提供一种无需专用设备或专用材料,即可对非完整芯片进行标识的晶圆结构及其制作方法。

6.根据一些实施例,一方面,本技术提供一种晶圆结构的制作方法,包括如下步骤:

7.提供晶圆,所述晶圆包括内部区域及位于所述内部区域外围的边缘区域;所述内部区域包括多个完整芯片区,所述边缘区域包括多个非完整芯片区;

8.于各所述完整芯片区内及各所述非完整芯片区内形成功率器件,在形成所述功率器件的工艺中还于需要标定的所述非完整芯片区形成特征图形。

9.本技术提供的晶圆结构的制作方法能够在形成功率器件的工艺过程中直接于需要标定的非完整芯片区形成特征图形,避免曝光机的产能与质量受到影响;无需昂贵的专用设备或打墨点工艺所需的材料,可减少工艺步骤,降低成本;同时由于工艺步骤较为简便,可以避免产生硅片破碎或沾污等问题,提升芯片质量。该特征图形可以用于监控过程工艺质量。

10.在其中一个实施例中,所述晶圆内形成有切割道,所述切割道位于相邻所述完整芯片区之间、相邻所述完整芯片区与所述非完整芯片区之间及相邻所述非完整芯片区之间。

11.在其中一个实施例中,所述于各所述完整芯片区内及各所述非完整芯片区内形成功率器件,在形成所述功率器件的过程中还于需要标定的所述非完整芯片区形成特征图形,包括如下步骤:

12.于所述晶圆的表面形成氧化层,所述氧化层覆盖各所述完整芯片区及各所述非完整芯片区;

13.于所述氧化层的上表面形成金属层;

14.于所述金属层的上表面形成图形化光刻胶层,所述图形化光刻胶层内形成有开口图形,所述开口图形定义出所述特征图形的形状及位置;

15.基于所述图形化光刻胶层刻蚀所述金属层,以在所述金属层内形成开口,所述开口暴露出部分所述氧化层,暴露出的部分所述氧化层为所述特征图形。

16.在其中一个实施例中,所述基于所述图形化光刻胶层刻蚀所述金属层,以在所述金属层内形成开口之后,还包括:

17.去除所述图形化光刻胶层。

18.上述实施例提供的晶圆结构的制作方法,通过暴露部分氧化层作为特征图形的方式在形成功率器件的工艺过程中直接于需要标定的非完整芯片区形成特征图形,省去了额外形成特征图形的工艺步骤,可减少工艺流程,降低成本;同时还可以避免产生硅片破碎或沾污等问题,提升芯片质量。

19.在其中一个实施例中,所述于所述金属层的上表面形成图形化光刻胶层,包括如下步骤:

20.于所述金属层的上表面形成光刻胶层,所述光刻胶层包括正性光刻胶层;

21.基于光罩对所述光刻胶层进行曝光,以于所述光刻胶层内形成曝光区域;

22.对曝光后的所述光刻胶层进行显影,去除位于所述曝光区域的光刻胶层,以得到所述图形化光刻胶层。

23.在其中一个实施例中,所述于各所述完整芯片区内及各所述非完整芯片区内形成功率器件,在形成所述功率器件的过程中还于需要标定的所述非完整芯片区形成特征图形,包括如下步骤:

24.于所述晶圆的表面形成氧化层,所述氧化层覆盖各所述完整芯片区及各所述非完整芯片区;

25.于所述氧化层的上表面形成金属层;

26.于所述金属层的上表面形成钝化层;

27.对需要标定的所述非完整芯片区内的所述钝化层进行图形化,以得到所述特征图形。

28.上述实施例提供的晶圆结构的制作方法,通过对需要标定的非完整芯片区内的钝化层进行图形化,能够在功率器件表面钝化工艺制备结束后于需要标定的非完整芯片区直接形成特征图形,省去了额外形成特征图形的工艺步骤,可减少工艺流程,降低成本;同时还可以避免产生硅片破碎或沾污等问题,提升芯片质量。

29.在其中一个实施例中,所述钝化层包括负性光刻材料层;

30.所述对所述钝化层进行图形化,以得到所述特征图形,包括如下步骤:

31.基于光罩对所述钝化层进行曝光,以于所述钝化层内形成曝光区域;

32.对曝光后的所述钝化层进行显影,去除位于所述曝光区域之外的所述钝化层,以得到所述特征图形。

33.本技术还提供了一种晶圆结构,包括:

34.晶圆,所述晶圆包括内部区域及位于所述内部区域外围的边缘区域;所述内部区域包括多个完整芯片区,所述边缘区域包括多个非完整芯片区;

35.功率器件,位于各所述完整芯片区内及各所述非完整芯片区内;

36.特征图形,位于需要标定的所述非完整芯片区,且位于所述功率器件内,所述特征图形基于形成所述功率器件的制作工艺而形成。

37.本技术提供的晶圆结构中的特征图形,是在形成功率器件的工艺中直接于需要标定的非完整芯片区形成的,能够避免曝光机的产能与质量受到影响;无需昂贵的专用设备或打墨点工艺所需的材料,可减少工艺步骤,降低成本;同时由于工艺步骤较为简便,可以避免产生硅片破碎或沾污等问题,提升芯片质量。该特征图形可以用于监控过程工艺质量。

38.在其中一个实施例中,所述晶圆内设有切割道,所述切割道位于相邻所述完整芯片区之间、相邻所述完整芯片区与所述非完整芯片区之间及相邻所述非完整芯片区之间。

39.在其中一个实施例中,所述功率器件包括:

40.氧化层,位于所述晶圆的表面,且覆盖各所述完整芯片区内及各所述非完整芯片区;

41.金属层,所述金属层内形成有开口,所述开口暴露出部分所述氧化层;

42.暴露出的所述氧化层为所述特征图形。

43.在其中一个实施例中,所述功率器件包括:

44.氧化层,位于所述晶圆的表面,且覆盖各所述完整芯片区内及各所述非完整芯片区;

45.金属层,位于所述氧化层的上表面;

46.钝化层,位于所述金属层的上表面,且位于各所述完整芯片区内及不需要标定的所述非完整芯片区内;

47.所述特征图形为通过对位于需要标定的所述非完整芯片区内钝化层进行曝光显影而得到。

48.在其中一个实施例中,所述钝化层包括负性光刻材料层。

附图说明

49.为了更清楚地说明本技术实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

50.图1为本技术其中一个实施例中提供的晶圆结构的制作方法的流程图;

51.图2为本技术其中一个实施例中提供的晶圆结构的制作方法中,晶圆以及特征图形的结构示意图;图2亦为本技术另一实施例中提供的晶圆结构的结构示意图;

52.图3为本技术其中一个实施例提供的晶圆结构的制作方法中,步骤s2的流程图;

53.图4为本技术其中一个实施例提供的晶圆结构的制作方法中,步骤s21所得结构的结构示意图;

54.图5为本技术其中一个实施例提供的晶圆结构的制作方法中,步骤s22所得结构的结构示意图;

55.图6为本技术另一个实施例提供的晶圆结构的制作方法中,步骤s23的流程图;

56.图7为本技术另一个实施例提供的晶圆结构的制作方法中,步骤s231所得结构的结构示意图;

57.图8为本技术另一个实施例提供的晶圆结构的制作方法中,步骤s233所得结构的结构示意图;

58.图9为本技术一些实施例提供的晶圆结构的制作方法中,步骤s24所得结构的结构示意图;

59.图10为本技术其中一个实施例提供的晶圆结构的制作方法中,步骤s25所得结构的结构示意图;

60.图11为本技术另一个实施例提供的晶圆结构的制作方法中,步骤s2的流程图;

61.图12为本技术其中一个实施例提供的晶圆结构的制作方法中,步骤s26所得结构的结构示意图;

62.图13为本技术另一个实施例提供的晶圆结构的制作方法中,步骤s27的流程图;

63.图14为本技术其中一个实施例提供的晶圆结构的制作方法中,步骤s272所得结构的结构示意图;

64.图15为本技术一些实施例提供的晶圆结构的制作方法中,特征图形的形状示意图。

65.附图标记说明:

66.1、晶圆;101、完整芯片区;102、非完整芯片区;103、切割道;104、缺口;2、特征图形;201、衬底;202、氧化层;203、金属层;204、光刻胶层;205、钝化层。

具体实施方式

67.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的首选实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使对本技术的公开内容更加透彻全面。

68.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

69.应当明白,当元件或层被称为“在...上”、“与...相邻”、“连接到”或“耦合到”其它元件或层时,其可以直接地在其它元件或层上、与之相邻、连接或耦合到其它元件或层,或者可以存在居间的元件或层。相反,当元件被称为“直接在...上”、“与...直接相邻”、“直接连接到”或“直接耦合到”其它元件或层时,则不存在居间的元件或层。应当明白,尽管可使用术语第一、第二、第三等描述各种元件、部件、区、层、掺杂类型和/或部分,这些元件、部件、区、层、掺杂类型和/或部分不应当被这些术语限制。这些术语仅仅用来区分一个元件、部件、区、层、掺杂类型或部分与另一个元件、部件、区、层、掺杂类型或部分。

70.空间关系术语例如“在...下”、“在...下面”、“下面的”、“在...之下”、“在...之上”、“上面的”等,在这里可以用于描述图中所示的一个元件或特征与其它元件或特征的关系。应当明白,除了图中所示的取向以外,空间关系术语还包括使用和操作中的器件的不同取向。例如,如果附图中的器件翻转,描述为“在其它元件下面”或“在其之下”或“在其下”元

件或特征将取向为在其它元件或特征“上”。因此,示例性术语“在...下面”和“在...下”可包括上和下两个取向。此外,器件也可以包括另外地取向(譬如,旋转90度或其它取向),并且在此使用的空间描述语相应地被解释。

71.在此使用时,单数形式的“一”、“一个”和“所述/该”也可以包括复数形式,除非上下文清楚指出另外的方式。还应明白,当术语“组成”和/或“包括”在该说明书中使用时,可以确定所述特征、整数、步骤、操作、元件和/或部件的存在,但不排除一个或更多其它的特征、整数、步骤、操作、元件、部件和/或组的存在或添加。同时,在此使用时,术语“和/或”包括相关所列项目的任何及所有组合。

72.这里参考作为本技术的理想实施例(和中间结构)的示意图的横截面图来描述发明的实施例,这样可以预期由于例如制造技术和/或容差导致的所示形状的变化。因此,本技术的实施例不应当局限于在此所示的区的特定形状,而是包括由于例如制造技术导致的形状偏差。因此,图中显示的区实质上是示意性的,它们的形状并不表示器件的区的实际形状,且并不限定本技术的范围。

73.请参阅图1,本技术提供一种晶圆结构的制作方法,包括如下步骤:

74.s1:提供晶圆,晶圆包括内部区域及位于内部区域外围的边缘区域;内部区域包括多个完整芯片区,边缘区域包括多个非完整芯片区;

75.s2:于各完整芯片区内及各非完整芯片区内形成功率器件,在形成功率器件的工艺中,还于需要标定的非完整芯片区形成特征图形。

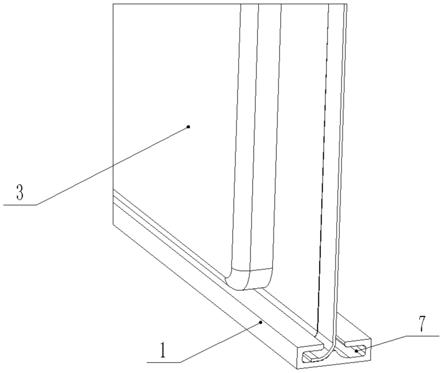

76.在步骤s1中,请参阅图2,提供晶圆1,晶圆1包括内部区域(未标示出,内部区域为非完整芯片区102内侧的区域)及位于内部区域外围的边缘区域(未标示出,边缘区域为非完整芯片区102所在的区域);内部区域包括多个完整芯片区101,边缘区域包括多个非完整芯片区102。

77.在步骤s2中,请继续参阅图2,于各完整芯片区101内及各非完整芯片区102内形成功率器件;在形成功率器件的工艺中,还于需要标定的非完整芯片区102形成特征图形2。

78.本技术提供的晶圆结构的制作方法能够在形成所述功率器件的工艺中直接于需要标定的非完整芯片区形成特征图形,能够避免曝光机的产能与质量受到影响;无需昂贵的专用设备或打墨点工艺所需的材料,可减少工艺步骤,降低成本;同时由于工艺步骤较为简便,可以避免产生硅片破碎或沾污等问题,提升芯片质量。该特征图形可以用于监控过程工艺质量。

79.具体的,功率器件可以为任意一种所需的器件,譬如,功率器件可以包括但不仅限于晶体管或发光器件等等。

80.可选的,在其中一个实施例中,需要标定的非完整芯片区102可以为晶圆1上的第一个非完整芯片区,也就是可以仅将边缘区域中的第一个非完整芯片区定义为需要标定的非完整芯片区101,即仅于边缘区域中的第一个非完整芯片区形成特征图形2。上述实施例中的晶圆结构的制作方法通过仅在边缘区域中的第一个非完整芯片区形成特征图形2,在监控过程工艺质量的同时,还由于不用在所有非完整芯片区都形成特征图形2,可进一步减少工艺步骤,降低成本。需要说明的是,这里的“晶圆2上的第一个非完整芯片区”可以为位于晶圆1的缺口104相对一侧,且与位于最远离缺口104的一行完整芯片区101位于同一行,图2中以位于最远离缺口104的一行完整芯片101左侧作为示例。

81.请参阅图3,在其中一个实施例中,步骤s2可以包括如下步骤:

82.s21:于晶圆1的表面形成氧化层;具体的,氧化层可以覆盖各完整芯片区101及各非完整芯片区102;

83.s22:于氧化层的上表面形成金属层;

84.s23:于金属层的上表面形成图形化光刻胶层,图形化光刻胶层内形成有开口图形,开口图形可以定义出特征图形2的形状及位置;

85.s24:基于图形化光刻胶层刻蚀金属层,以在金属层内形成开口;开口暴露出部分氧化层,暴露出的部分氧化层为特征图形2。

86.上述实施例中提供的晶圆结构的制作方法,通过暴露部分氧化层作为特征图形的方式在形成功率器件的工艺过程中直接于需要标定的非完整芯片区形成特征图形,省去了额外形成特征图形的工艺步骤,可减少工艺流程,降低成本;同时还可以避免产生硅片破碎或沾污等问题,提升芯片质量。进一步的,由于上述方法在表面金属工艺制备结束的同时就能够在需要标定的非完整芯片区102形成特征图形2,因此还能够避免曝光机的产能与质量受到影响。

87.具体的,在步骤s21中,请参阅图3中的s21及图4,于晶圆1的表面形成氧化层202;氧化层202可以覆盖各完整芯片区101及各非完整芯片区102。

88.在其中一个实施例中,晶圆1可以包括基底材料及位于基底材料内的沟槽结构;具体的,基底材料可以包括但不仅限于硅衬底。在另一实施例中,氧化层202可以包括但不仅限于二氧化硅层。

89.在步骤s22中,请参阅图3中的s22及图5,于氧化层202的上表面形成金属层203。

90.具体的,金属层203可以包括但不仅限于铜层、钴层、铬层或钛层中的一种或几种。

91.在其中一个实施例中,晶圆1内也可以形成有器件结构,可以包括但不限于晶体管和/或二极管等等;晶体管1中的器件结构可以与金属层203电连接,并经金属层203电学引出。

92.对于步骤s23,请结合图3中的s23参阅图6至图8,在其中一个实施例中,步骤s23可以包括如下步骤:

93.s231:如图7所示,于金属层203的上表面形成光刻胶层204;具体的,光刻胶层204包括正性光刻胶层;

94.s232:基于光罩(mask)对光刻胶层204进行曝光,以于光刻胶层204内形成曝光区域;

95.s233:对曝光后的光刻胶层204进行显影,去除位于曝光区域的光刻胶层204,以得到图形化光刻胶层。

96.具体的,如图8所示,在步骤s233中,去除位于曝光区域的光刻胶层204后,剩余的光刻胶层204为图形化光刻胶层。

97.需要说明的是,对于步骤s23,上述实施例通过采用正性光刻胶,在曝光区域,正性光刻胶溶解度增强,会被显影液溶解,而在非曝光区域,光刻胶溶解受到抑制,不会被显影液溶解,因此曝光加显影之后留下的是未曝光部分;也就是说正性光刻胶的作用包括把与光罩上图形相同的图形复刻到所得结构表面。

98.可以理解,上述步骤s23中形成图形化光刻胶层的方式还可以采用其他形式,而不

限于上述实施例已经提到的利用正性光刻胶层的形式,只要其能够于金属层的上表面形成图形化光刻胶层,图形化光刻胶层内形成有开口图形,开口图形可以定义出特征图形2的形状及位置即可;譬如,在其他实施例中,光刻胶层204可以包括负性光刻材料层,在此基础上,通过调整光罩的位置和/或形状,也能够去除部分光刻胶层204并使得所得结构如图8所示。

99.在步骤s24中,请参阅图3中的s24及图9,基于图形化光刻胶层刻蚀金属层203,以在金属层203内形成开口;开口暴露出部分氧化层202,暴露出的部分氧化层202为特征图形2。

100.功率器件的表面一般会暴露出用于引出的金属层。上述实施例中提供的晶圆结构的制作方法,在曝光显影后,暴露出部分氧化层202作为特征图形2,由于氧化层202与金属层203的材质不同,二者具有不同的颜色,这就使得特征图形2与晶圆1上的其他区域具有明显的颜色差异,从而很容易辨识出特征图形2。

101.在其中一个实施例中,对金属层203进行刻蚀工艺后,形成的图形化金属层可以包括但不仅限于引出焊盘。

102.请继续参阅,在其中一个实施例中,步骤s24之后还可以包括如下步骤:

103.s25:如图10所示,去除图形化光刻胶层。

104.具体的,在步骤s25中,可以采用但不仅限于灰化工艺去除图形化光刻胶层。

105.请参阅图11,在本技术另一个实施例的步骤s2中,于氧化层202的上表面形成金属层203之后,还可以包括如下步骤:

106.s26:于金属层203的上表面形成钝化层;

107.s27:对需要标定的非完整芯片区102内的钝化层进行图形化,以得到特征图形2。

108.上述实施例提供的晶圆结构的制作方法,通过对需要标定的非完整芯片区内的钝化层进行图形化,能够在功率器件表面钝化工艺制备结束后于需要标定的非完整芯片区直接形成特征图形,省去了额外形成特征图形的工艺步骤,可减少工艺流程,降低成本;同时还可以避免产生硅片破碎或沾污等问题,提升芯片质量。进一步的,由于上述方法在表面钝化工艺制备结束的同时就能够于需要标定的非完整芯片区102形成特征图形2,因此还能够避免曝光机的产能与质量受到影响。

109.在步骤s26中,请参阅图11中的s26及图12,于金属层203的上表面形成钝化层205。

110.对于步骤s27,在其中一个实施例中,钝化层205包括负性光刻材料层,也就是说,上述实施例中的钝化层205其材料具有负性光刻胶的性能,同时还具有钝化性能;需要说明的是,采用负性光刻材料层,在曝光区域,负性光刻材料能够快速发生光固化反应,不会被显影液溶解,而在非曝光区域,光刻胶可以被显影液溶解,因此曝光加显影之后留下的是曝光部分;也就是说负性光刻材料层的作用包括把与掩膜板上图形相反的图形复刻到所得结构表面。

111.请参阅图13,上述实施例中步骤s27可以包括如下步骤:

112.s271:基于光罩对钝化层205进行曝光,以于钝化层205内形成曝光区域;

113.s272:对曝光后的钝化层205进行显影,去除位于曝光区域之外的钝化层205,以得到特征图形2。

114.在步骤s272中,请结合图13中的s272及图14,去除位于曝光区域之外的钝化层205

后,剩余的钝化层205为特征图形2。

115.可以理解,对于步骤s27,还可以采用其他形式对钝化层205进行图形化,而不限于上述实施例中已经提到的利用负性光刻材料层的形式,只要其能够对需要标定的非完整芯片区102内的钝化层进行图形化并得到特征图形2即可。

116.譬如,在其中一个实施例中,钝化层205还可以是包括正性光刻胶层,在此基础上,步骤s27可以包括如下步骤:

117.基于光罩对钝化层205进行曝光,以于钝化层205内形成曝光区域;

118.对曝光后的钝化层205进行显影,去除位于曝光区域的钝化层205,以得到特征图形2。

119.又譬如,在另一个实施例中,步骤s27还可以包括如下步骤:

120.于钝化层205的上表面形成掩膜层;

121.对掩膜层进行图形化,以定义曝光区域;

122.基于图形化后的掩膜层刻蚀钝化层205,以得到特征图形2;在得到特征图形2之后还可以包括去除剩余掩膜层的步骤。

123.由于上述实施例中的特征图形2为钝化层205图形化而得,而钝化层205与金属层203的材质不同,二者具有不同的颜色,这就使得曝光显影完成后形成的特征图形2与晶圆1上的其他区域具有明显的颜色差异,从而很容易辨识出特征图形2。

124.需要说明的是,对金属层203或钝化层204进行图形化工艺后即形成了芯片;此时,完整芯片区101上形成了完整的芯片,非完整芯片区102上形成了非完整芯片。

125.本技术对于钝化层205的材质并不做限定。具体的,对于钝化层205包括负性光刻材料层的实施例而言,钝化层可以包括负性光刻聚酰亚胺(pi)层;聚酰亚胺具有优异的耐热性、抗化学腐蚀性、电绝缘性及力学机械性能,因此上述实施例提供的制作方法,能够通过负性光刻聚酰亚胺层减少各种自然环境和工作环境对半导体器件造成的影响,提高芯片的成品率,增强器件的可靠性和稳定性。在另一些于钝化层205的上表面形成图形化掩膜层,基于图形化掩膜层刻蚀钝化层205,以得到特征图形2的实施例中,钝化层可以包括二氧化硅(sio2)、氮化硅(si3n4)和/或磷硅玻璃(psg)等等。

126.请继续参阅图2,在其中一个实施例中,晶圆1内形成有切割道103,切割道103位于相邻完整芯片区101之间、相邻完整芯片区101与非完整芯片区102之间及相邻非完整芯片区102之间。具体的,切割道103在晶圆1内将晶圆1分割为多个完整芯片区101及多个非完整芯片区102。

127.请参阅图15中的(a)图至(h)图,特征图形2的形状可以根据实际需要进行设定;具体的,特征图形2的形状可以包括但不仅限于圆形、正方形、三角形、矩形、五边形、六边形、梯形以及椭圆形等等中的任意一种,本技术对于特征图形2的形状并不做具体限定。

128.在其中一个实施例中,请参阅图15中的(a)图,特征图形2的形状为圆形,特征图形2的半径可以为300μm至5000μm;具体的,特征图形2的半径可以为300μm、900μm、1500μm、2400μm、3600μm、1800μm或5000μm;本实施例对于特征图形2半径的大小并不做具体限定。

129.在其中一个实施例中,请参阅图15中的(b)图,特征图形2的形状可以为正方形,特征图形2的边长可以为300μm至5000μm;具体的,特征图形2的边长可以为300μm、900μm、1500μm、2400μm、3600μm、1800μm或5000μm;本实施例对于特征图形2边长的长度并不做具体限

定。

130.需要说明的是,上述数据仅作为示例,在实际实施例中,特征图形2的半径或边长可以根据晶圆的大小作适应性的调整,其数值具有较强的灵活性,并不以上述数据为限。

131.请继续参阅图2,本技术还提供一种晶圆结构,晶圆结构可以包括晶圆1、功率器件及特征图形2;

132.其中,晶圆1包括内部区域及位于内部区域外围的边缘区域;内部区域包括多个完整芯片区101,边缘区域包括多个非完整芯片区102。功率器件位于各完整芯片区101内及各非完整芯片区102内。特征图形2位于需要标定的非完整芯片区102,且位于功率器件内;具体的,特征图形2基于形成功率器件的制作工艺而形成。

133.本技术提供的晶圆结构中的特征图形,是在形成功率器件的工艺中直接于需要标定的非完整芯片区形成的,无需昂贵的专用设备或打墨点工艺所需的材料,可减少工艺步骤,降低成本;同时由于工艺步骤较为简便,可以避免产生硅片破碎或沾污等问题,提升芯片质量。该特征图形可以用于监控过程工艺质量。

134.具体的,功率器件可以为任意一种所需的器件;譬如,功率器件可以包括但不限于晶体管或发光器件等等。

135.在其中一个实施例中,需要标定的非完整芯片区102可以为晶圆1上的第一个非完整芯片区,也就是可以仅将边缘区域中的第一个非完整芯片区定义为需要标定的非完整芯片区101,即仅于边缘区域中的第一个非完整芯片区形成特征图形2。上述实施例中的晶圆结构的制作方法通过仅在边缘区域中的第一个非完整芯片区形成特征图形2,在监控过程工艺质量的同时,还由于不用在所有非完整芯片区都形成特征图形2,可进一步减少工艺步骤,降低成本。需要说明的是,这里的“晶圆2上的第一个非完整芯片区”可以为位于晶圆1的缺口104相对一侧,且与位于最远离缺口104的一行完整芯片区101位于同一行,图2中以位于最远离缺口104的一行完整芯片101左侧作为示例。

136.请继续参阅图10,在其中一个实施例中,功率器件可以包括氧化层202及金属层203。

137.其中,氧化层202,位于晶圆1的表面,且覆盖各完整芯片区101内及各非完整芯片区102。金属层203内形成有开口,开口暴露出部分氧化层202,暴露出的氧化层202为特征图形2。

138.上述实施例提供的晶圆结构,是通过暴露部分氧化层作为特征图形的方式在形成功率器件的工艺过程中直接于需要标定的非完整芯片区形成特征图形,省去了额外形成特征图形的工艺步骤,可减少工艺流程,降低成本;同时还可以避免产生硅片破碎或沾污等问题,提升芯片质量。

139.请继续参阅图14,在另一个实施例中,功率器件可以包括氧化层202、金属层203及钝化层205。

140.其中氧化层202位于晶圆1的表面,且覆盖各完整芯片区101内及各非完整芯片区102。金属层203位于氧化层202的上表面。钝化层205位于金属层203的上表面,且位于各完整芯片区101内及不需要标定的非完整芯片区102内。

141.上述实施例提供的晶圆结构中,特征图形2为通过对位于需要标定的非完整芯片区102内钝化层205进行曝光显影而得到;需要说明的是,在需要标定的非完整芯片区102

内,可以基于光罩对钝化层205进行曝光,以于钝化层205内形成曝光区域,对曝光后的钝化层205进行显影,去除位于曝光区域之外的钝化层205,剩余的钝化层205为特征图形2;在各完整芯片区101内及不需要标定的非完整芯片区102内,保留全部的钝化层205。

142.上述实施例提供的晶圆结构中,特征图形是通过对需要标定的非完整芯片区内的钝化层进行图形化而形成的,无需昂贵的专用设备或打墨点工艺所需的材料即可形成,可减少工艺步骤,降低成本;同时由于工艺步骤较为简便,可以避免产生硅片破碎或沾污等问题,提升芯片质量。

143.作为示例,钝化层205的材质可以包括但不仅限于聚酰亚胺(pi)、二氧化硅(sio2)、氮化硅(si3n4)及磷硅玻璃(psg)等等中的任意一种或几种;具体的,上述实施例中的钝化层205的材质包括聚酰亚胺。

144.请继续参阅图15中的(a)图至(h)图,特征图形2的形状可以根据实际需要进行设定。具体的,特征图形2的形状可以包括但不仅限于圆形、正方形、三角形、矩形、五边形、六边形、梯形以及椭圆形等等中的任意一种,本技术对于特征图形2的形状并不做具体限定。

145.在其中一个实施例中,请参阅图15中的(a)图,特征图形2的形状为圆形,特征图形2的半径可以为300μm至5000μm;具体的,特征图形2的半径可以为300μm、900μm、1500μm、2400μm、3600μm、1800μm或5000μm;本实施例对于特征图形2半径的大小并不做具体限定。

146.在其中一个实施例中,请参阅图15中的(b)图,特征图形2的形状可以为正方形,特征图形2的边长可以为300μm至5000μm;具体的,特征图形2的边长可以为300μm、900μm、1500μm、2400μm、3600μm、1800μm或5000μm;本实施例对于特征图形2边长的长度并不做具体限定。

147.应该理解的是,虽然图1、图3、图6、图11及图13的流程图中的各个步骤按照箭头的指示依次显示,但是这些步骤并不是必然按照箭头指示的顺序依次执行。除非本文中有明确的说明,这些步骤的执行并没有严格的顺序限制,这些步骤可以以其它的顺序执行。而且,图1、图3、图6、图11及图13中的至少一部分步骤可以包括多个步骤或者多个阶段,这些步骤或者阶段并不必然是在同一时刻执行完成,而是可以在不同的时刻执行,这些步骤或者阶段的执行顺序也不必然是依次进行,而是可以与其它步骤或者其它步骤中的步骤或者阶段的至少一部分轮流或者交替地执行。

148.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

149.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对申请专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。