1.本发明属于信息技术领域,具体涉及一种用于存内计算的数据编码方法以及一种存内计算方法。

背景技术:

2.近年来在存储器内部实现计算功能(简称存内计算)成为研究热点。存内计算被普遍认为能够解决传统冯诺依曼结构计算的存储瓶颈和功耗瓶颈问题。当前的存内计算实现普遍为低精度实现,而功能主要为神经网络的推断,神经网络的推断不需要太高的精度,因此存内计算非常适合被应用于神经网络推断。

3.目前,有一些研究者提出了高精度的存内计算架构,这些架构大部分是基于逻辑门存内计算或者数字存内计算的。其优点是高能效,缺点是延迟非常高,在微秒量级。例如,jingcheng wang等人利用sram和附加电路实现了1位串行全加器,并通过处理器串行指令实现了32bit整数和32bit浮点数运算,但是这一实现并非并行运算,进行一个浮点操作需要4978个周期,延迟非常高,参见《a compute sram with bit

‑

serial integer/floating

‑

point operations for programmable in

‑

memory vector acceleration》。ji

‑

hoon kim等人使用了基于逻辑门的存内计算,利用稀疏性提高了效能,但是运算延迟高,参见《z

‑

pim:an energy

‑

efficient sparsity aware processing

‑

in

‑

memory architecture with fully

‑

variable weight precision》。yun long等人提出了一种数字存内计算方法,但每一次运算真正开启的行数只能小于等于1,对于高比特的数据输入,需要大量周期才能完成存内计算,带来大量延迟,参见《flex

‑

pim:a ferroelectric fet based vector matrix multiplication engine with dynamical bitwidth and floating point precision》。mahmut e.sinangil等人提出了一种模拟存内计算方法,使用多次脉冲作为该存内计算方法的输入方式,这种方式对于高比特的输入会带来大量延迟。

4.因此,为了在高精度的存内计算要求下能够提高能效,并且降低延迟,需要一种新的针对存内计算的编码方法以及相应的存内计算方法。

技术实现要素:

5.为解决上述问题,提供一种用于存内计算的数据编码方法和存内计算方法,本发明采用了如下技术方案:

6.本发明提供了一种用于存内计算的数据编码方法,用于对原始数据进行针对于存内计算的数据编码,其特征在于,包括步骤a1,在原始数据的首位前和末尾后均添加1比特的0;步骤a2,将原始数据的每两位相邻的比特位做差,相对高位的比特位为减数,相对低位的比特位为被减数,得到编码后的数据。

7.本发明提供了一种存内计算方法,其特征在于,包括步骤s1,通过数据编码方法对存储器内的原始数据进行数据编码,得到编码后的存储数据,通过数据编码方法对输入的原始数据进行数据编码,得到编码后的输入数据;步骤s2,将存储数据按照预定的排列方法

存储到存储器的单元矩阵中;步骤s3,将输入数据输入到存储器的输入段,进行存内模拟计算,得到存内模拟计算结果,其中,数据编码方法为上述的数据编码方法。

8.本发明提供的存内计算方法,还可以具有这样的技术特征,其中,排列方法为三角形排列方法,该三角形排列方法包括以下步骤:步骤b1,将存储数据按照从最高有效位到最低有效位的顺序横向排布开,得到横向存储数据,并将横向存储数据存储在存储器的第一行单元矩阵中;步骤b2,将横向存储数据的每个比特位右移1位并移除最后一个比特位,在横向存储数据的最高有效位用0补充,然后将处理后的横向存储数据存储在存储器的下一行单元矩阵中;步骤b3,重复步骤b2,重复次数为横向存储数据的比特位数

‑

1。

9.本发明提供的存内计算方法,还可以具有这样的技术特征,其中,排列方法为线性排列方法。

10.本发明提供的存内计算方法,还可以具有这样的技术特征,其中,存内模拟计算具体为:将输入模拟信号作用到存储器的单元矩阵上,在存储器的单元矩阵的列方向上产生电流或电荷的积累,积累为存内模拟计算结果。

11.本发明提供的存内计算方法,还可以具有这样的技术特征,其中,将存内模拟计算结果作为存内计算结果进行输出。

12.本发明提供的存内计算方法,还可以具有这样的技术特征,其中,通过模数转换单元将存内模拟计算结果转化为数字信号,将数字信号作为存内计算结果进行输出。

13.发明作用与效果

14.根据本发明的存内计算方法,由于采用了用于存内计算的数据编码方法分别对存储器内的原始数据以及输入的原始数据进行了针对存内计算的编码,得到编码后的存储数据以及输入数据,因此,明显降低了存内计算数据二进制表示中1的个数,从而降低了存内计算功耗;还由于采用了三角形排列方法将编码后的存储数据存储到存储器的单元矩阵中,因此,将输入数据转换为模拟信号并直接作用到该单元矩阵上,在单元矩阵的列方向上产生的电流或电荷积累即为存储数据和输入数据乘加的计算结果,从而能够以这样的方式快速直接地得到存内模拟计算结果,提高了计算效率。

附图说明

15.图1是本发明实施例中存内计算方法的流程图;

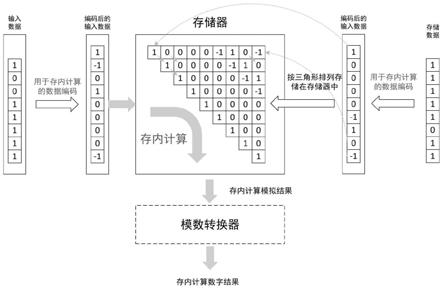

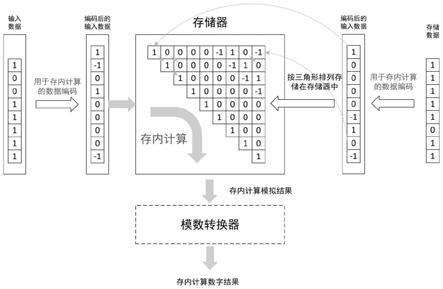

16.图2是本发明实施例中数据编码方法和存内计算方法的示意图。

具体实施方式

17.为了使本发明实现的技术手段、创作特征、达成目的与功效易于明白了解,以下结合实施例及附图对本发明的用于存内计算的数据编码方法和存内计算方法作具体阐述。

18.<实施例>

19.图1是本发明实施例中存内计算方法的流程图。

20.如图1所示,本发明实施例的存内计算方法包括以下步骤:

21.步骤s1,通过数据编码方法对存储器内的原始数据进行编码,得到编码后的存储数据,通过相同的数据编码方法对输入的原始数据进行编码,得到编码后的输入数据。

22.图2是本发明实施例中数据编码方法和存内计算方法的示意图。

23.如图2所示,本实施例中,数据编码方法为用于存内计算的数据编码方法,包括以下步骤:

24.步骤a1,在原始数据的首位前和末尾后均添加1比特的0;

25.步骤a2,将原始数据的每两位比特位做差,相对高位的比特位为减数,相对低位的比特位为被减数,得到编码后的数据。

26.编码前的数据表示为:

27.a=a

727

a

626

a

525

a

424

a

323

a222 a121 a02028.=

‑0·28

a

727

a

626

a

525

a

424

a

323

a222 a121 a020 0

·2‑129.=(

‑

0 a7)28 (

‑

a7 a6)27 (

‑

a6 a5)26 (

‑

a5 a4)25 (

‑

a4 a3)24 (

‑

a3 a2)23 (

‑

a2 a1)22 (

‑

a1 a0)21 (

‑

a0 0)2030.编码后的数据表示为:

31.a=y

828

y

727

y

626

y

525

y

424

y

323

y222 y121 y02032.其中,

33.y8=a7,y7=

‑

a7 a6,y6=

‑

a6 a5,y5=

‑

a5 a4,y4=

‑

a4 a3,y334.=

‑

a3 a2,y2=

‑

a2 a1,y1=

‑

a1 a0,y0=

‑

a035.式中,a0~a7为原始数据第0位至第7位的比特值,y0~y8为编码后的数据的第0位至第8位的比特值,其中第0位为最低位。可以看到编码后的数据比原始数据多一个比特位。

36.本实施例中,如图2中所示,存储器内的原始数据为11111011,输入的原始数据为10011111,将两者分别进行上述的数据编码后,得到编码后的存储数据为10000

‑

110

‑

1,编码后的输入数据为1

‑

1010000

‑

1。对比原始数据和编码后的数据,可以看到编码后的存储数据以及编码后的输入数据中1的位数明显减少。

37.步骤s2,将编码后的存储数据按照预定的排列方法存储到存储器的单元矩阵中。

38.本实施例中,预定的排列方法为三角形排列方法,该三角形排列方法包括以下步骤:

39.步骤b1,将编码后的存储数据按照从最高有效位(msb)到最低有效位(lsb)的顺序横向排布开,得到横向存储数据,并将该横向存储数据存储在存储器的第一行单元矩阵中;

40.步骤b2,将横向存储数据的每个比特位右移1位并移除最后一个比特位,在横向存储数据的最高有效位用0补充,并将处理后的横向存储数据存储在存储器的下一行单元矩阵中;

41.步骤b3,重复步骤b2,重复次数为横向存储数据的比特位数

‑

1。

42.本实施例中,编码后的存储数据按照从最高有效位到最低有效位的顺序横向排布开,得到的横向存储数据即为10000

‑

110

‑

1,将10000

‑

110

‑

1存入存储器的第一行单元矩阵;然后,将该横向存储数据的每个比特右移1位并移除最后一个比特位,也即保持该横向存储数据的总长度不变,在其最高有效位用0补充,得到010000

‑

110,将010000

‑

110存入存储器的第二行单元矩阵;依次类推,直到右移次数等于存储数据的比特数

‑

1,最终有效数据(即除首位0以外的数据)在存储器内形成三角形排列,如图2中所示。

43.步骤s3,将编码后的输入数据输入到存储器的输入端,进行存内模拟计算,得到存内模拟计算结果。

44.本实施例中,输入数据为数字信号,将该数字信号直接输入到存储器的输入端。存

内模拟计算的方法为,将输入模拟信号作用到存储器的单元矩阵上,在存储器的单元矩阵中已存储有上述三角形排列的存储数据,输入模拟信号直接作用到该单元矩阵后,在存储器的单元矩阵的列方向上产生电流或电荷的积累,该积累即为存储数据和输入数据乘加的计算结果,也即为存内模拟计算结果,该存内模拟计算结果为模拟信号。

45.本实施例中,如图2所示,存储器的单元矩阵中存储有按三角形排列的存储数据,编码后的输入数据为10000

‑

110

‑

1,将对应的输入数字信号作用到存储器的单元矩阵,在列方向上产生积累,得到的存内计算结果具体为:左数第1列的积累结果为1,第2列积累结果为

‑

1,第3列积累结果为0,第4列积累结果为1,第5列积累结果为0,第6列积累结果为

‑

1,第7列积累结果为2,第8列积累结果为

‑

1,第9列积累结果为

‑

3。

46.最后,可以将该存内模拟计算结果直接进行输出,也可以通过模数转换单元将该存内模拟计算结果转换为数字信号再进行输出。本实施例中,模数转换单元为现有技术中的模数转换器,将模拟信号(即电平)转换成对应的数字信号。

47.如上所述,通过本发明实施例的存内计算方法,分别对存储器内的原始数据以及输入的原始数据进行了针对存内计算的编码,并对编码后的数据进行了存内模拟计算,最后将存内模拟计算的结果直接进行输出或转为数字信号再进行输出。

48.实施例作用与效果

49.根据本发明的存内计算方法,由于采用了用于存内计算的数据编码方法分别对存储器内的原始数据以及输入的原始数据进行了针对存内计算的编码,得到编码后的存储数据以及输入数据,因此,明显降低了存内计算数据二进制表示中1的个数,从而降低了存内计算功耗;还由于采用了三角形排列方法将编码后的存储数据存储到存储器的单元矩阵中,因此,将输入数据转换为模拟信号并直接作用到该单元矩阵上,在列方向上产生的电流或电荷积累即为存储数据和输入数据乘加的计算结果,从而能够以这样的方式快速直接地得到存内模拟计算结果,提高了计算效率。

50.此外,由于输入的原始数据为数字信号,而通过本发明的存内计算方法得到的存内模拟计算结果也可以通过模数转换器转化为数字信号后再进行输出,也即输入输出数据都可以为数字信号,因此,可以实现高精度的存内计算。

51.上述实施例仅用于举例说明本发明的具体实施方式,而本发明不限于上述实施例的描述范围。

52.在上述实施例中,存储器内的原始数据在编码后按照三角形排列存储到存储器的单元矩阵中,在本发明的其他方案中,存储器内的原始数据在编码后也可以按照传统线性排列存储到存储器的单元矩阵中,同样也能实现本发明的技术效果。

53.在上述实施例中,输入数据为编码后的数字信号,将该数字信号直接输入到存储器的输入端进行存内计算,在本发明的其他方案中,也可以将输入数据通过数模转换器转换为相应的模拟信号,再将该模拟信号输入到存储器的输入端进行存内计算,同样也能实现本发明的技术效果。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。